Xilinx高速SerDes布线要点

一.为什么要重视高速信号的走线

>随着信号速率的提高,PCB布线不是简单的互联,成为了信号的传输线,从而存在寄生电感和寄生电容;

>存在导体损耗,导体损耗包含趋肤效应,因此会受到表面层的粗糙度影响;

>串扰:串扰一旦产生,后期就无法消除,且信号频率越高,串扰越明显

>阻抗不连续会引起反射,比如信号换层,变换参考平面,线宽改变,P/N间距发生变化等都会导致阻抗不连续;

>抖动:时钟抖动,触发信号的抖动

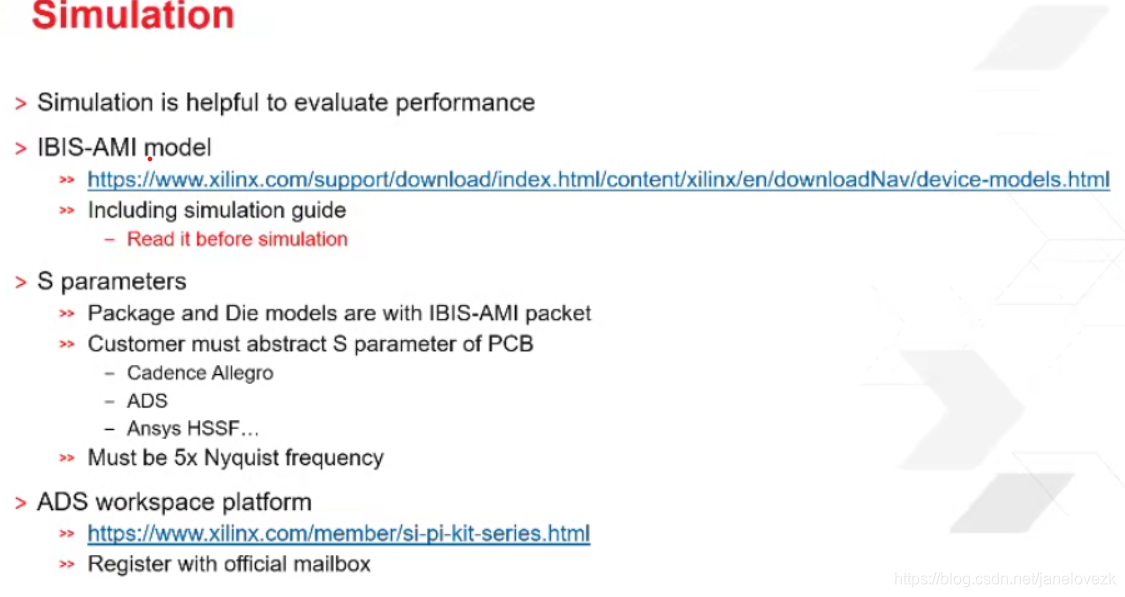

>在进行高速信号走线时,simulation是必要的。

二.布线要点

1.平面连续,一般都选择GND平面作为参考平面;

2.stub要短

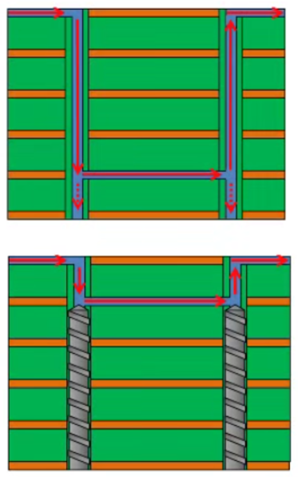

1)过孔的残余部分(stub)要短;

>stub长度要小于0.2*Trising;

>比如,FPGA在top层,信号线尽量在离bottom层较近的那一层,减小stub。但是不能走在表层,表层一般只能走微带线,且抗干扰的性能较差。因此在布线时,速率最高的信号线要占据最好的信号层优先布局。

>被钻也是减小stub长度的方式;

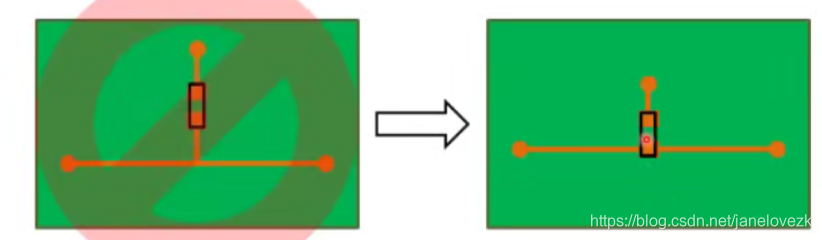

2)信号走线的stub要短

一些信号难免需要上拉或者下拉电阻,为了减小stub,增强信号完整性,一般将焊盘放在信号线上。

3.P/N等长

P与N的时间差最多允许在2ps;PN等长的目的是保证P 与N反相,从而消除共模噪声,消除共模电压的漂移,消除信号间的串扰。

等长需要考虑以下几点:

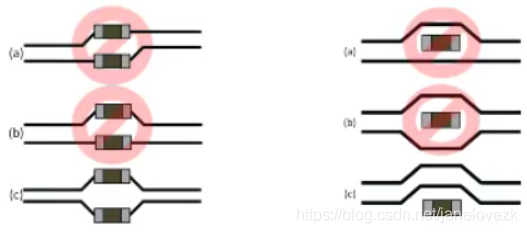

>走线要对称,图中c是正确的走线方式;

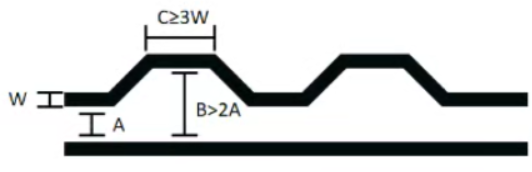

>绕线等长

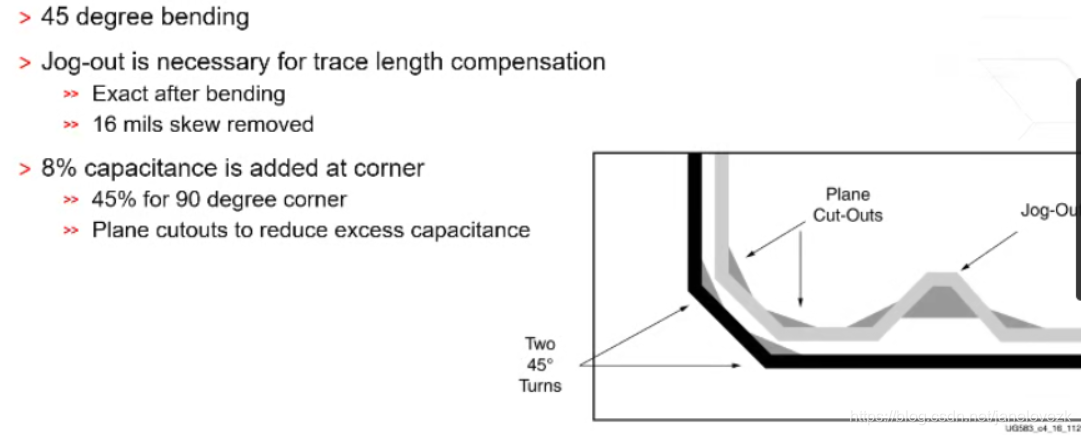

>差分线45度弯曲,较短的线需要通过蛇形走线来弥补,差分线弯曲处的电容增加,可通过切割平面的方式减少多余的电容。

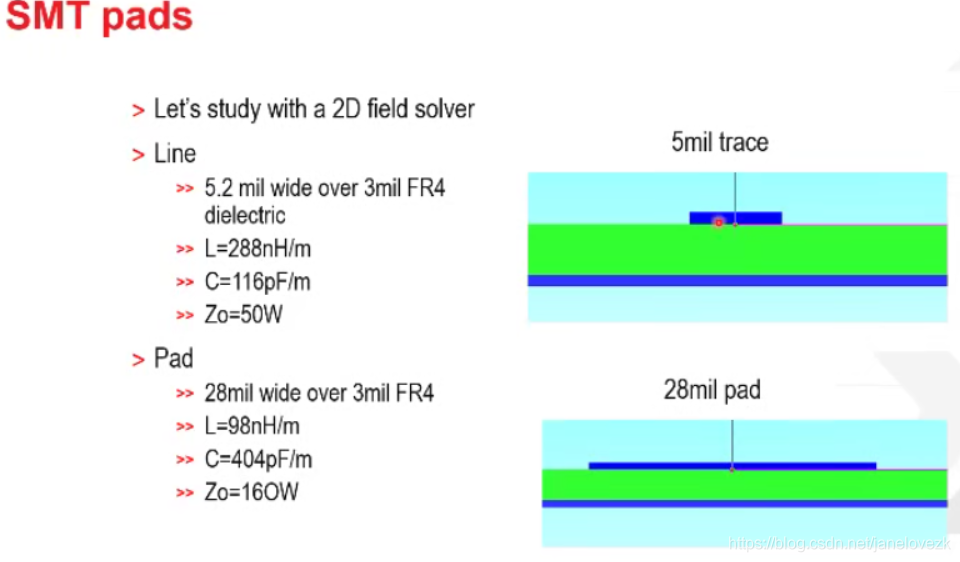

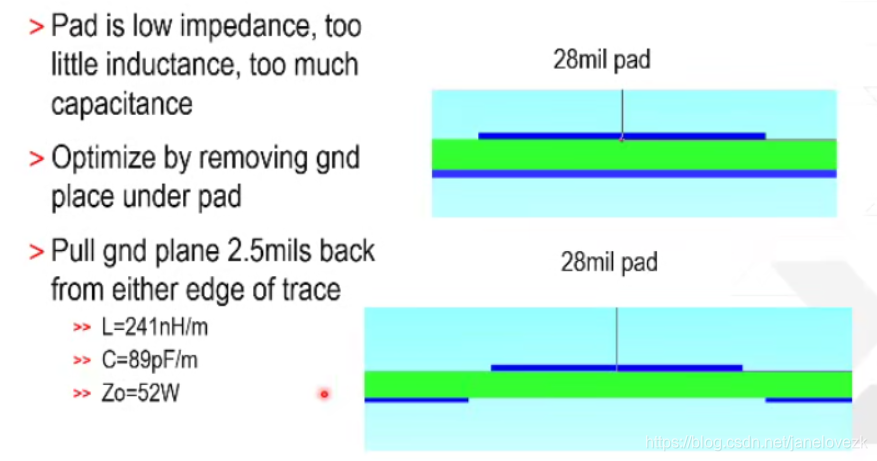

4)阻抗要连续

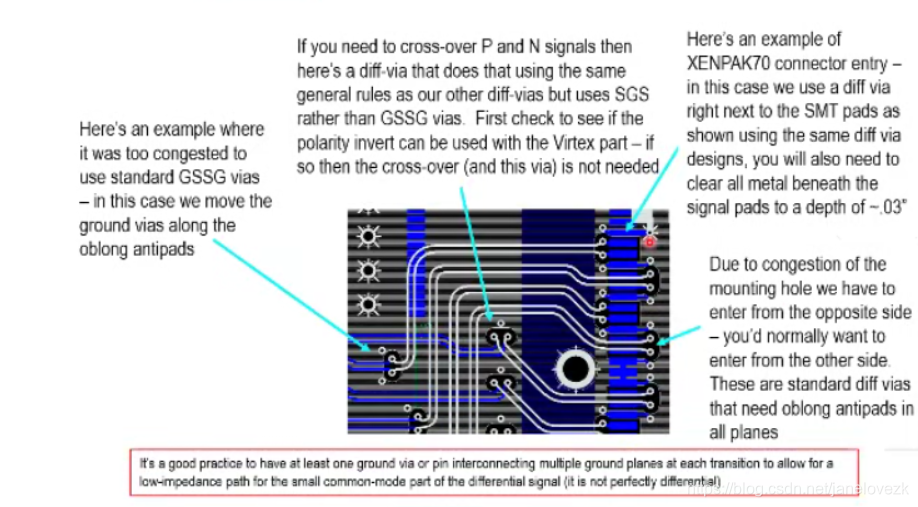

差分对过孔旁需要加两个地孔,减小回流路径上的串扰

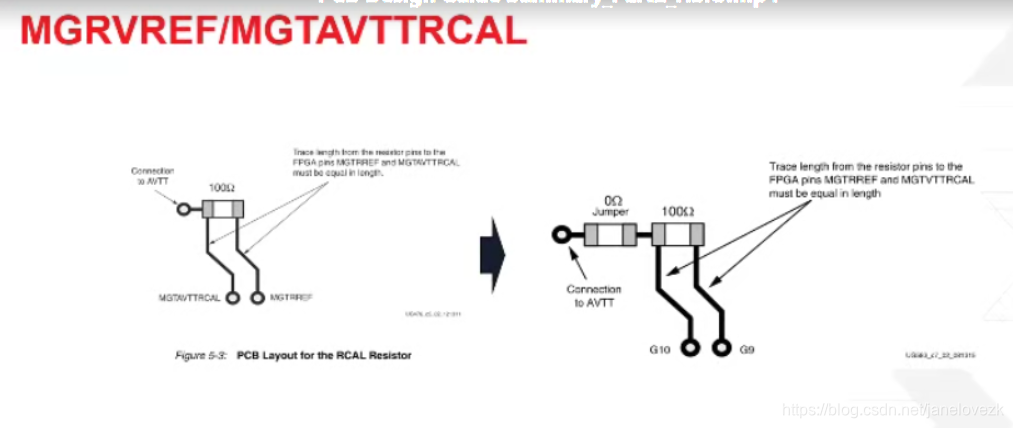

Serdes上要在MGAVTTRCAL与MGRVREF间串一个100欧姆精密电阻。

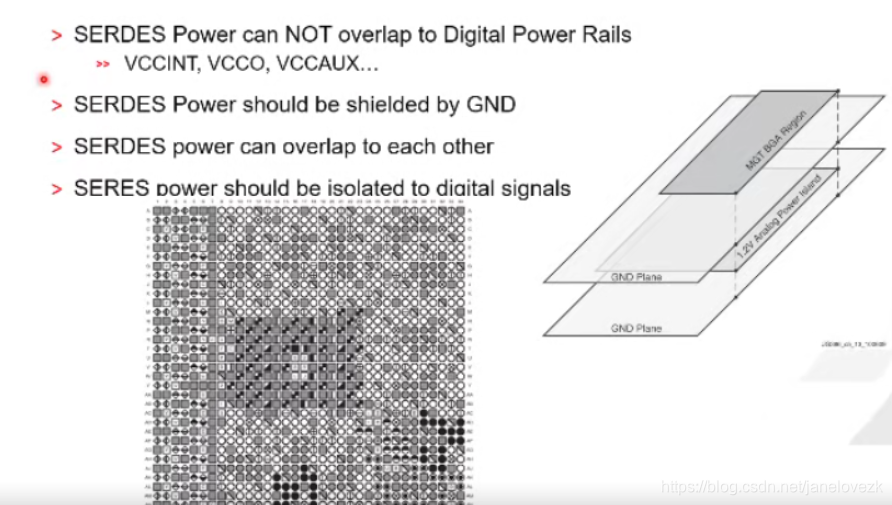

Serdes上电源需要干净的放置

信号仿真资源网址

本文详细介绍了高速信号走线的重要性,包括寄生效应、导体损耗、串扰、阻抗不连续和抖动等问题。重点讨论了布线要点,如平面连续、stub缩短、P/N等长和阻抗匹配。提出了平面连续选择GND作为参考平面,减小stub长度以降低信号完整性影响,强调差分线的等长和蛇形走线以消除串扰,以及使用精密电阻和优化电源布局来改善SerDes性能。同时,建议在布线过程中进行信号仿真以确保设计质量。

本文详细介绍了高速信号走线的重要性,包括寄生效应、导体损耗、串扰、阻抗不连续和抖动等问题。重点讨论了布线要点,如平面连续、stub缩短、P/N等长和阻抗匹配。提出了平面连续选择GND作为参考平面,减小stub长度以降低信号完整性影响,强调差分线的等长和蛇形走线以消除串扰,以及使用精密电阻和优化电源布局来改善SerDes性能。同时,建议在布线过程中进行信号仿真以确保设计质量。

223

223

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?