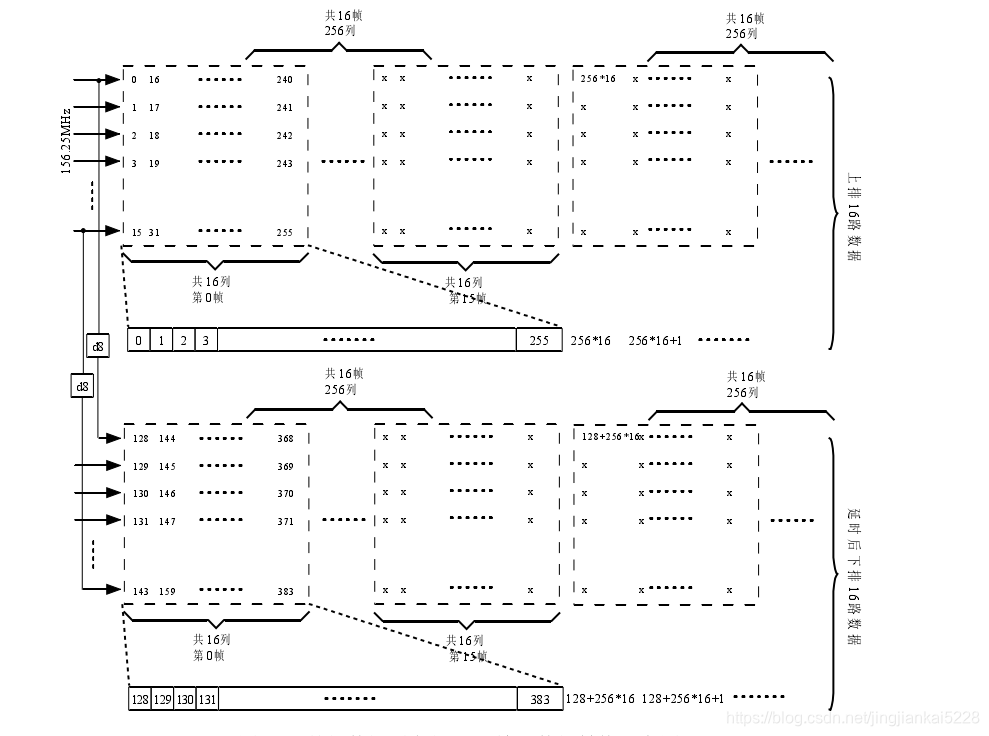

雷达数字信号处理实际工程中,随着AD采样率越来越高,FPGA不能实时的处理全带宽的数据,一般在FPGA内部采取分相(也就是串并转换)的方式降低处理速度,在雷达信号处理过程中,对信号进行检测常用的方式有多相滤波架构和直接进行FFT进行频域分析,这里不进行展开,本博客主要是通过频域分析介绍一种通过串行FFT核恢复出最原始的N点的FFT结果,比如我们需要进行4096点FFT运算时,我们可以通过8个512点的串行FFT运算恢复出最终的4096点FFT结果,当然也可以通过将数据缓存下来然后分别进行4096点FFT运算,具体的流水结构如下图所示:

这样的结构在实现过程中需要消耗大量的RAM,并且需要消耗8个4096点的FFT ip核资源上不推荐,当然感兴趣的同学可以看一下博客下面的链接上传的论文。

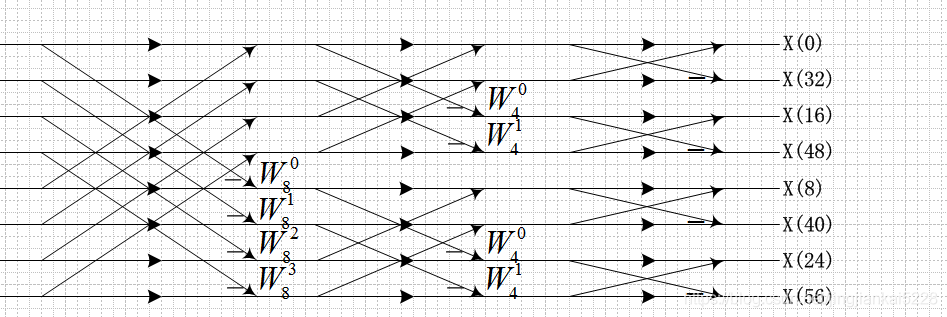

下面推到一下并行架构,为了方便这里只演示一个两相的结构

这里不做具体过多的解释,感兴趣的同学可以自行再推到一边,这里直接告诉结论,就是需要如果要得到N点FFT结果,原始数据为M相,可以通过M个FFT核分别做一个N/M点的FFT,每相分别乘一个exp(j*(-2pik*(fft_pahse-1))/N)的因子,最后做一个M点的并行FFT即可。这里给出一个8点DFT蝶形结构图,注意我这里是从64点截取出来的 注意运算结果的关系,FPGA实现过程中需要调整。

实现

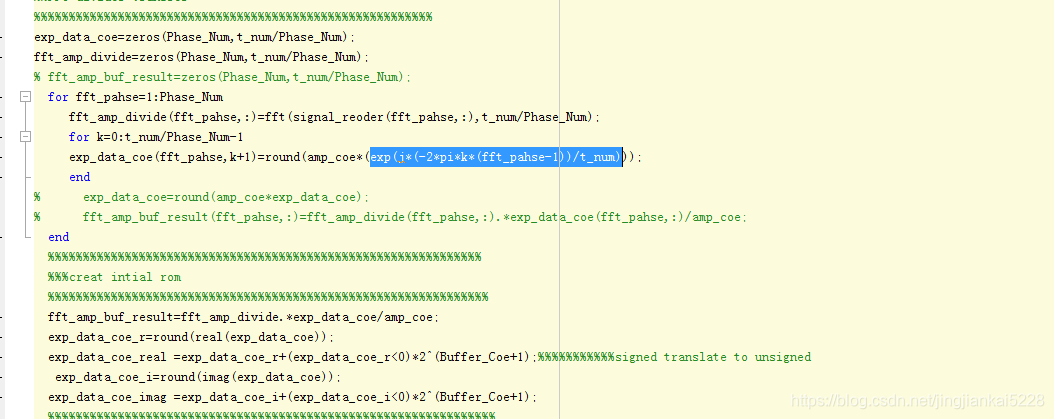

在进行实际工程实现时,对于这种复杂的运算,为了方便测试,推荐将所有的结构都先用matlab进行仿真一边,一方面是为了验证方案可行性,再就是为了方便对比运算结果,这里就一个8相的结构实现。

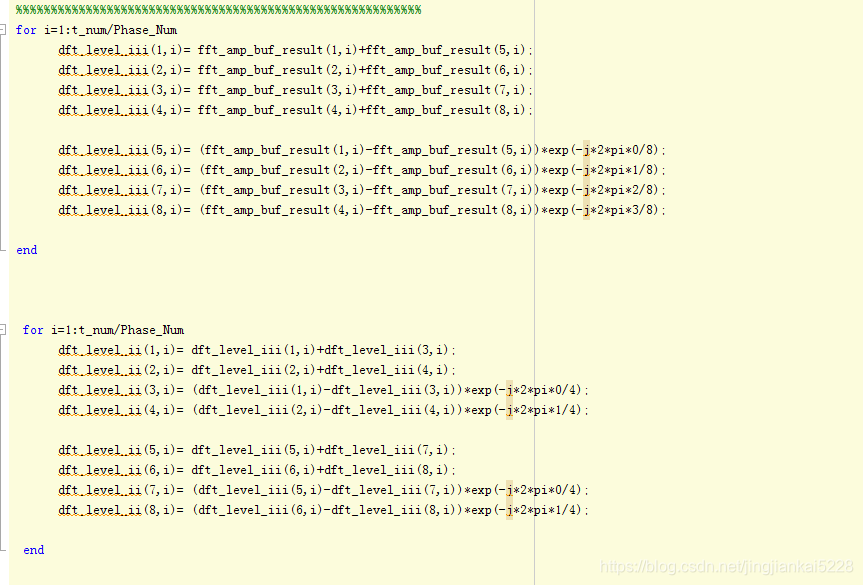

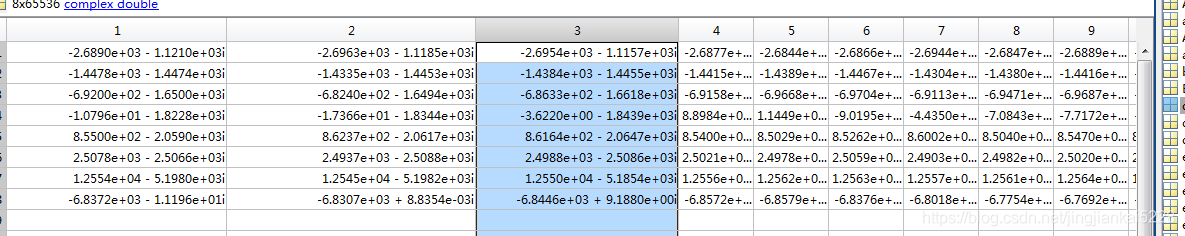

将8点的并行结构每一级都单独写出,方便对比,下面是FFT的matlab仿真结果:

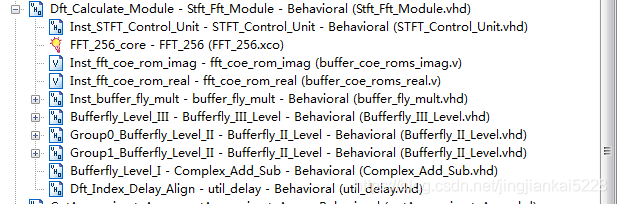

这里产生的事一个2.4G采样率,信号为1.9G的信号,可以看到直接做FFT的结果和先同时处理,然后恢复的结果基本一致,在FPGA代码实现过程中注意蝶形因子及中间过程中的化简,可以把运算过程中需要乘的因子前移,最重要的就是为了做到程序的模块化:

这样只要做好一个8相的结构,实际工程中遇到4相的结构,只需要要改变设计的常量进行选择例化即可

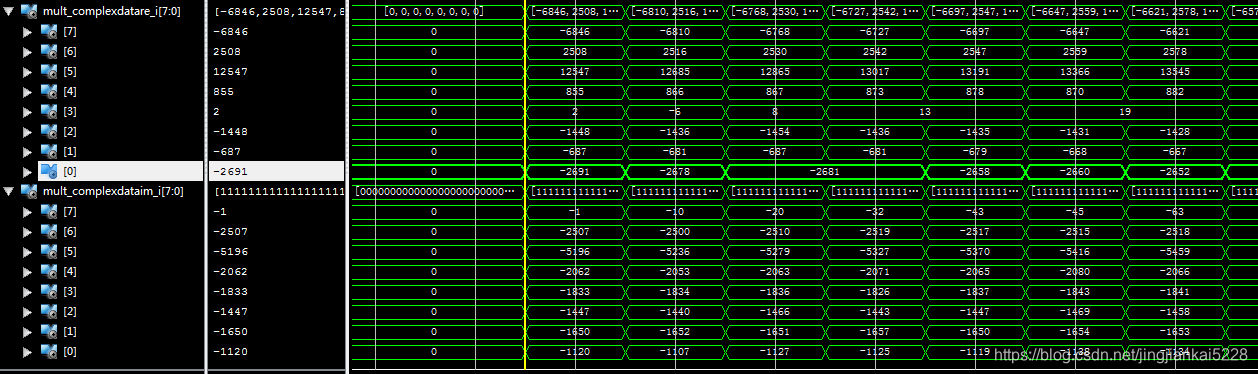

以下分别是matlab运算结果及FPGA实现结果

以上算法也可运用到频谱监测,可以显示全带宽覆盖的频谱,即使频谱仪也是有占用比的,通过以上方式不会有漏掉时域信号的可能。

PS:串行FFT论文链接

https://download.csdn.net/download/jingjiankai5228/15333437

1069

1069

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?