Zero-Order Hold:实现零阶保持采样期间

- 在仿真库中的位置为:

-

Simulink / Discrete

HDL Coder / Discrete

模型为:

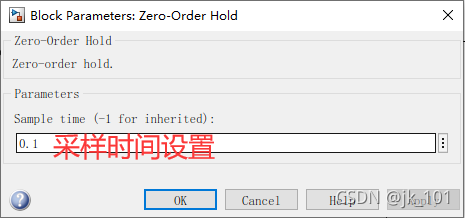

双击模型打开参数设置界面,如图所示:

说明

Zero-Order Hold 模块在指定的采样期间内保持其输入不变。如果输入为向量,模块会按相同的采样期间保持向量中的所有元素。

可通过 Sample time 参数指定样本之间的时间间隔。设置为 -1 表示模块将继承 Sample time

Simulink / Discrete

HDL Coder / Discrete

模型为:

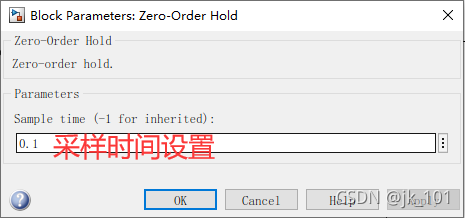

双击模型打开参数设置界面,如图所示:

Zero-Order Hold 模块在指定的采样期间内保持其输入不变。如果输入为向量,模块会按相同的采样期间保持向量中的所有元素。

可通过 Sample time 参数指定样本之间的时间间隔。设置为 -1 表示模块将继承 Sample time

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?