VCU128评估板的使用

vivado报错:[Labtoolstcl 44-513] HW Target shutdown.

ViVado中打开硬件后,突然关掉开发板电源就会报该错误。

FPGA差分时钟输入

差分时钟输入

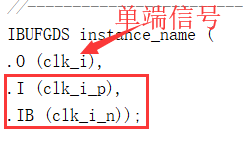

将差分时钟转化为单端时钟clk_tmp,然后再将clk_tmp输入到全局时钟bufg上。并且注意在约束文件中仅仅对差分时钟的p端进行约束。

将差分时钟转化为单端时钟主要用IBUFGDS这个原语。

IBUFDS 是差分输入的时候用;

OBUFDS 是差分输出的时候用;

IBUFGDS 则是时钟信号专用的输入缓冲器。

IBUFGDS u0 (

.O(data_clk_tmp), // Buffer output

.I(data_clk_p), // Diff_p buffer input

.IB(data_clk_n) // Diff_n buffer input

);

BUFG i0 (

.O(data_clk),

.I(data_clk_tmp)

);

差分的管脚分配是成对分配的,只要分配好了一个,另一个会自动分配好,所以不用担心另一个信号怎么分配的问题。

只有差分端口的P侧需要被约束;如果两者都被约束,则工具将它们作为两个独立的时钟定义,并分析它们之间的时钟路径。这可能导致不正确的要求。

类似地,只有差分数据端口的p侧需要在输入延迟和输出延迟约束中受到约束。

set_property PACKAGE_PIN AD12 [get_ports {clk_i_p}]

set_property IOSTAND LVDS [get_ports {clk_i_p}]

总结:

输入信号需要用到IBUFDS实现差分转单端,输入时钟还需要加BUFG

输出信号使用OBUFDS实现单端转差分

差分信号只需要绑P端管脚,“IOSTANDARD”设置需要注意

Vivado报错ERROR: [Place 30-675] Sub-optimal placement for a global clock-capable IO pin and BUFG pair.

ERROR: [Place 30-675] Sub-optimal placement for a global clock-capable IO pin and BUFG pair.If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

这是因为我在约束文件中把时钟输入信号错误地绑定在普通引脚上。后来把时钟输入信号绑定在全局时钟输入引脚GC上,解决此问题。

解释如下:

做约束文件中的时序例外约束部分的内容的时候,发现很多单位之前的FPGA项目中的约束文件里经常出现的一句时序例外约束是:

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets NETS_NAME_IBUF]

约束的对象往往是除了sys_clk之外的、由外部引入作为一些通信接口比如SPI或者MDIO接口的时钟管脚的IBUF线。

如果不加这个约束,执行implement的时候往往就会报error或者critical warning、内容中也会提到加上这个约束的话、就会将严重警告或者错误降级为普通warning。

这是因为原来FPGA的管脚上有一类专用的时钟管脚、他们一般用于将外部的时钟信号引入FPGA、并在FPGA module中使用这些引入的时钟信号。但是如果设计时管脚分配没做好、或者管脚不够用了,那么就有可能将本该接入专用时钟管脚(或者叫做全局时钟管脚)的信号,接到了普通IO口上,这样只能通过添加CLOCK_DEDICETED_ROUTE FLASE绕过PAR的检查,但是没有解决根本问题。

必须使用片上的MRCC或者SRCC引脚来把外部时钟信号引入FPGA、然后再在FPGA上使用这些引入的时钟。MRCC/SRCC管脚这两类管脚在一般情况下、不做时钟引入的管脚的时候、也可以作为普通IO来使用。

烧录比特文件的信息INFO: [Labtools 27-1434] Device xc7k410t (JTAG device index = 0)

INFO: [Labtools 27-1434] Device xc7k410t (JTAG device index = 0) is programmed with a design that has no supported debug core(s) in it.

我在VCU128写了一个流水灯,发现烧录比特流文件后,板子灯没有任何变化。后来发现是我把时钟输入信号加错了,虽然我加的是全局时钟GC,但是该时钟不是上电就跑的时钟,而是依赖某些条件才有的。所以流水灯没有变化。后来我将晶振产生的时钟输入就解决了该问题。

如何在电路图中找全局时钟和晶振时钟

在电路图中搜索GC,则会出现全局时钟输入引脚。在说明手册中输入晶振的英文名称(oscilator),则会找出晶振时钟。

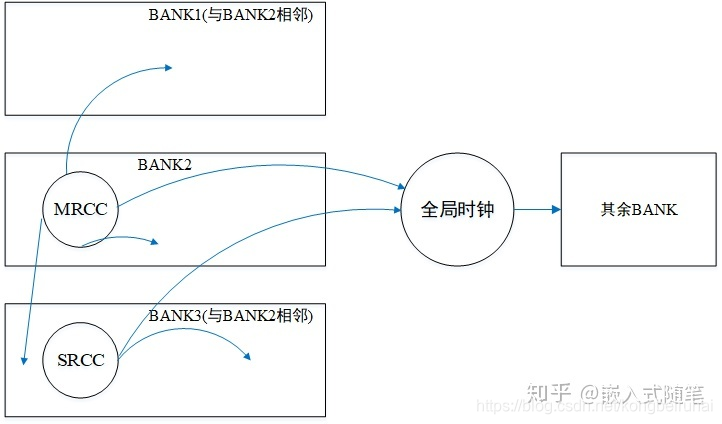

Xilinx的7系列的SRCC和MRCC(转载)

首先MRCC和SRCC都是可以连接到全局时钟的,但是全局时钟的资源有限。如果程序较大都使用全局时钟的话,那时钟资源就不够用了。SRCC可用于本区域时钟这个比较好了解,MRCC用于相邻的区域该这么理解,MRCC通过不同于全局时钟的渠道可以到达相邻的区域。如下图BANK1和BANK3可以使用BANK2的MRCC分上来的时钟,没必要先将BANK2的MRCC连接到全局时钟再连接到BANK1和BANK3,这样不但节省了全局时钟资源,而且路径更短。

Xilinx 芯片全局时钟资源的使用方法主要有下面5种:

-

GCLK -> IBUFG --> BUFG.

IBUFG 后面连接 BUFG的方法是最基本的全局时钟资源的使用方法, 其等效于 BUFGP

-

GCLKP&&GCLKN --> IBUFGDS —> BUFG

当输入时钟为差分信号时候,需要使用 IBUFGDS 原语

- IBUFG + DCM + BUFG

通过 DCM(digital clock manage) 不仅能对时钟进行同步、移相、分频、倍频等变换,而且可以使用全局时钟的输出无抖动和小延迟。

-

Logic + BUFG

BUFG 不但可使用 IBUFG 的输出,还可以驱动其他普通信号的输出。当某个信号的扇出非常大,并且要求抖动延迟最小时,可以使用BUFG驱动该信号,使该信号利用全局时钟资源。

-

Logic + DCM + BUFG

DCM 可以改变也可以控制变换普通时钟信号。

时钟架构总览

链接: https://www.cnblogs.com/hcr1995/p/9800547.html.

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?