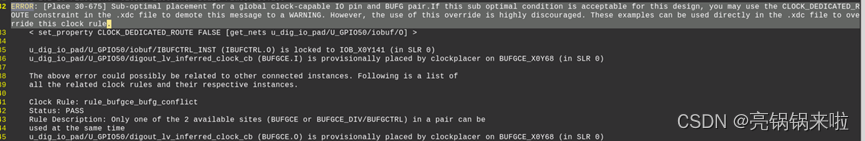

ERROR [placed 30-675] ERROR: Sub-optimal placement for a global clock-capable I0 pin and BUFG pair. If this sub optimal condition is acceptable for this design, you may use the CLOCK DEDICATED ROUTE constraint in the xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

<set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets u_dig_io_pad/U_GPIO10/iobuf/0]

这个错误是在放置器件的时候报出来的,意思就是时钟使能的I/O和全局缓冲器BUFG放置的位置不是最优的。如下图我的设计报错:

这里的规矩就是一个SLR里面(普及一

订阅专栏 解锁全文

订阅专栏 解锁全文

1487

1487

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?