独热码

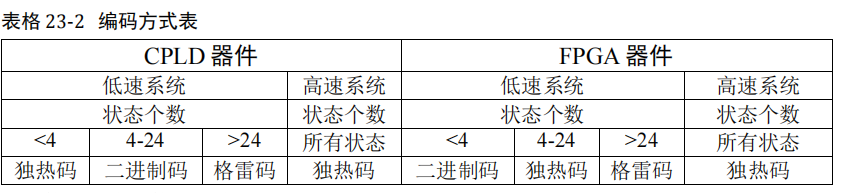

首先独热码因为每个状态只有 1bit 是不同的,所以在执行到 55 行时的(state == TWO)这条语句时,综合器会识别出这是一个比较器,而因为只有 1 比特为 1,所以综合器会进行智能优化为(state[2] == 1’b1),这就相当于把之前 3 比特的比较器变为了 1 比特的比较器, 大大节省了组合逻辑资源,但是付出的代价就是状态变量的位宽需要的比较多,而我们 FPGA 中组合逻辑资源相对较少,所以比较宝贵,而寄存器资源较多,所以很完美。

二进制编码

情况和独热码刚好相反,他因为使用了较少的状态变量,使之在减

少了寄存器状态的同时无法进行比较器部分的优化,所以使用的寄存器资源较少,而使用的组合逻辑资源较多。

比较

CPLD 就是一个组合逻辑资源多而寄存器逻辑资源少的器件,因为这里我们使用的是 FPGA 器件,所以使用独热码进行编码。

高速系统

就因为这个比较部分的优化,还使得使用独热码编码的状态机可以在高速系统上运行,其原因是多比特的比较器每个比特到达比较器的时间可能会因为布局布线的走线长短而导致路径延时的不同,这样在高速系统下,就会导致采集到不稳定的状态,导致比较后的结果产生一个时钟的毛刺,使输出不稳定,而单比特的比较器就不用考虑这种问题。

格雷码

但是如果状态数非常多的话即使是 FPGA 也吃不消独热码对寄存器的消耗,所以当状态数特别多的时候可以使用格雷码对状态进行编码。格雷码虽然也是和二进制编码一样使用的寄存器资源少,组合逻辑资源多,但是其相邻状态转换时只有一个状态发生翻转,这样不仅能消除状态转换时由多条信号线的传输延迟所造成的毛刺,又可以降低功耗,所以要优于二进制码的方式,相当于是独热码和二进制编码的折中。

1033

1033

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?