前言

PCIe在FPGA的开发中可谓经常被用到,PCIe IP帮助开发者解决了协议层的事情,使对PCIe没有很多了解的的开发中也能开发,XDMA(DMA/Bridge Subsystem for PCI Express) IP就实现了这个功能。Xilinx官方还为系统端提供了驱动与中间件,甚至包括了源代码。极大的缩短了开发周期。

本文使用的是Vivado 2019.1 芯片型号K7325T

一、PCIe是什么

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。(百度百科)

现在的主流是PCIe3.0

PCI Express 3.0基本规范版本3.0在多个延迟之后于2010年11月提供。 2007年8月,PCI-SIG宣布PCI Express 3.0将以每秒8吉比特的速度(GT / s)进行比特率,并且将与现有的PCI Express实现向后兼容。当时还宣布,PCI Express 3.0的最终规范将延迟到2010年第二季度。PCI Express 3.0规范的新功能包括增强信令和数据完整性的一些优化,包括发射机和接收机均衡,PLL改进,时钟数据恢复和当前支持的拓扑的通道增强。

更详细的资料可以找书或翻百度,网上大牛写的PCIe理解挺多的

二、XDMA IP核

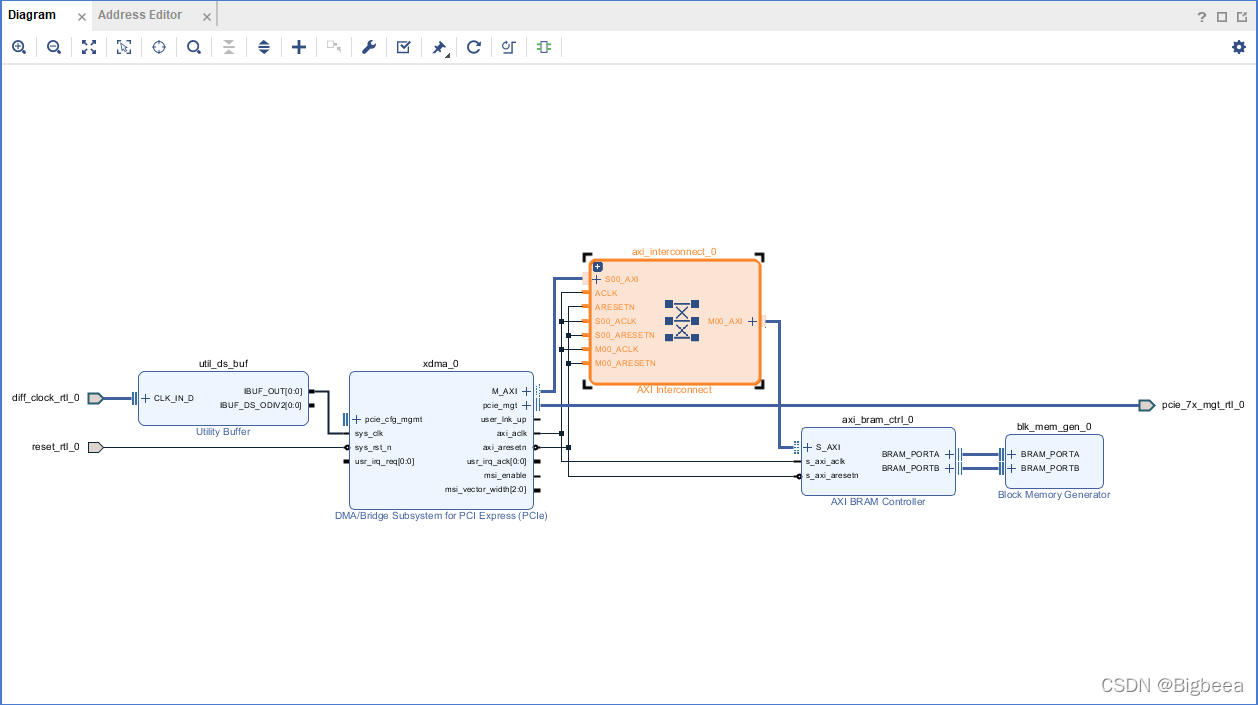

XDMA被用于Block Design(一种图形化编程的方式)开发中,不同的Vivado版本和芯片型号可能存在界面上的差异

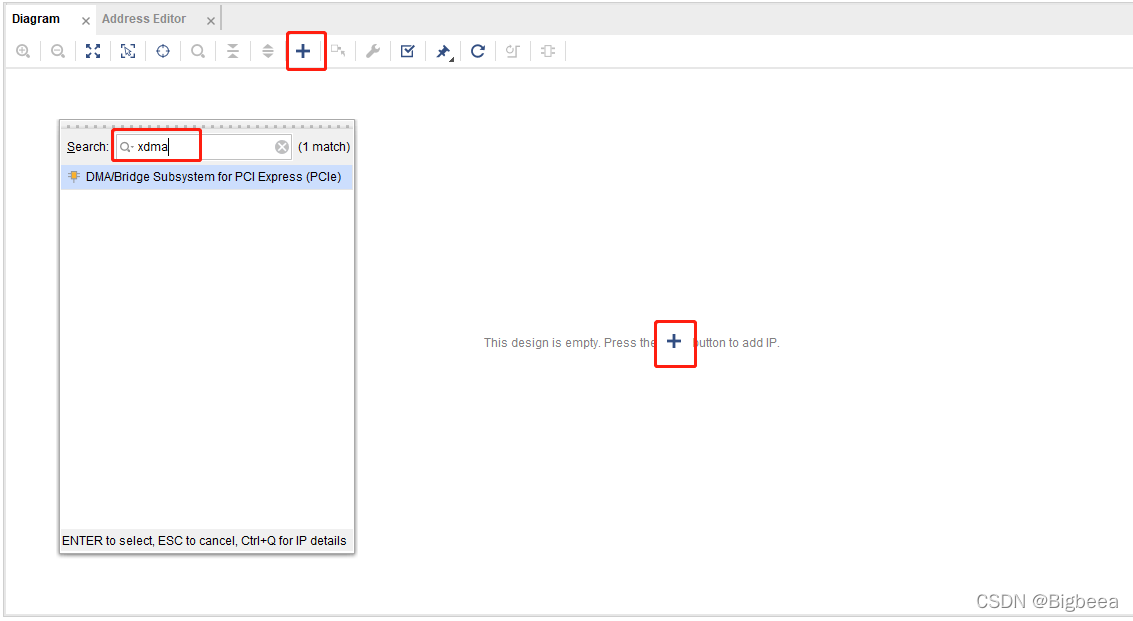

打开BD,添加XDMA IP,双击IP

预览

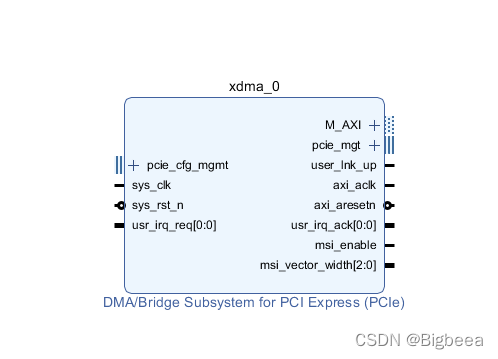

先看一下XDMA IP的外观

XDMA有几个关键的接口,主要用到的也就这几个:

- sys_clk ip时钟,根据设计选择具体使用后文会讲

- sys_rst_n ip复位

- usr_irq_req和usr_irq_ack 中断请求和会应

- M_AXI AXI4总线,XDMA IP无FPGA逻辑进行数据交换的接口,用户逻辑对于PCIe的访问都通过这个接口。

- pcie_mgt pcie总线,用于物理层的链接,要走顶层的

- user_lnk_up pcie链接正常信号,端到端连接成功,能够开始正常同学,这个部分通常是上电后自动完成的,如果不正常就很麻烦了,可能得排查硬件,因为高速差分对PCB走线有很高的要求。

- axi_aclk和axi_aresetn 由于这里XDMA ip作为一个AXI的master设备,所以这里输出AXI需要的clk和areset信号

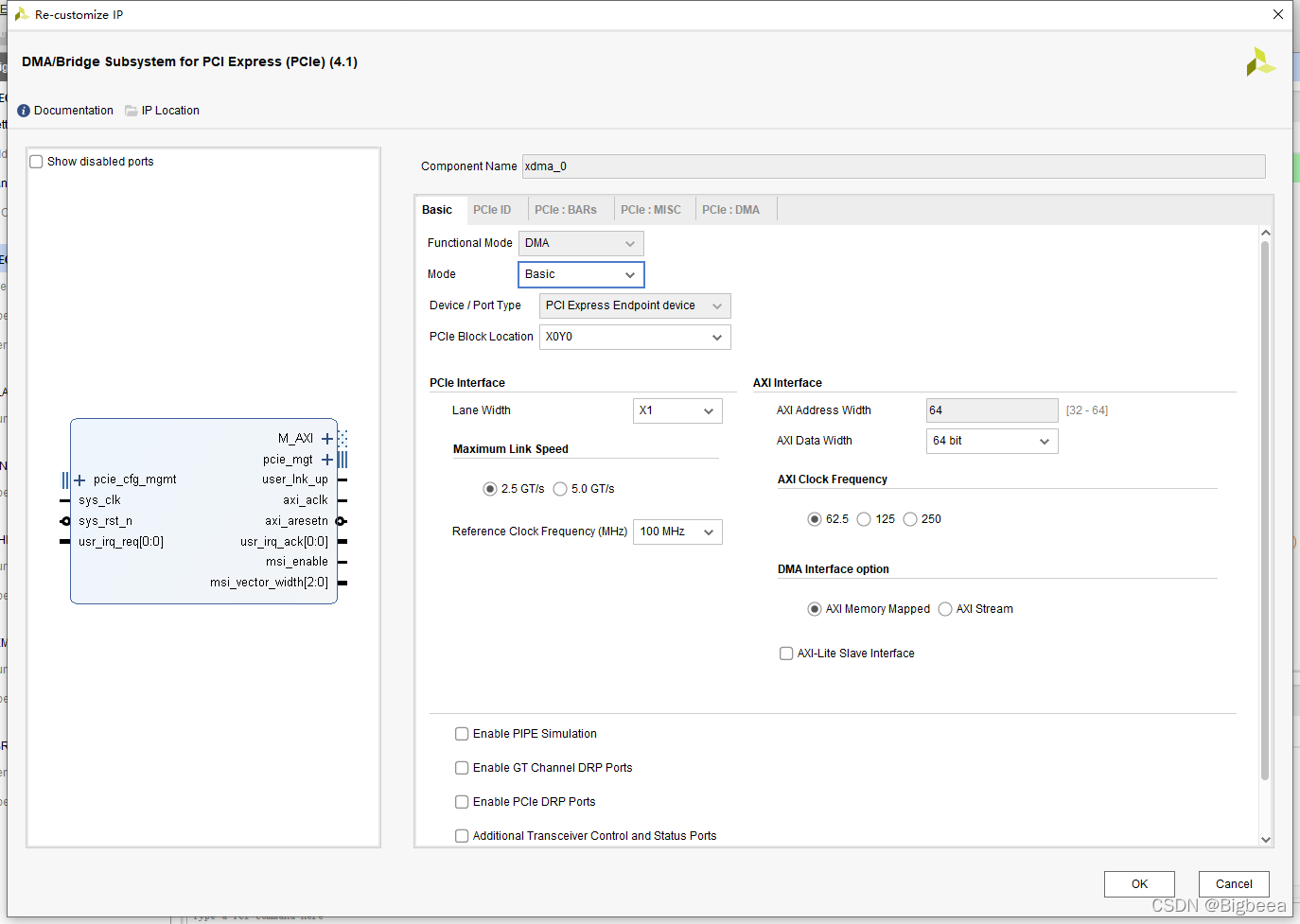

Basic

第一个界面,关键的设置是:(所有的设置都根据需求或者硬件设计进行选择)

- Lane Width lane的个数要根据需求进行选择,lane越多,传输速率越快

- Maximum Link Speed

- AXI DATA Width和AXI Clock 这个根据Lane数和速率相关

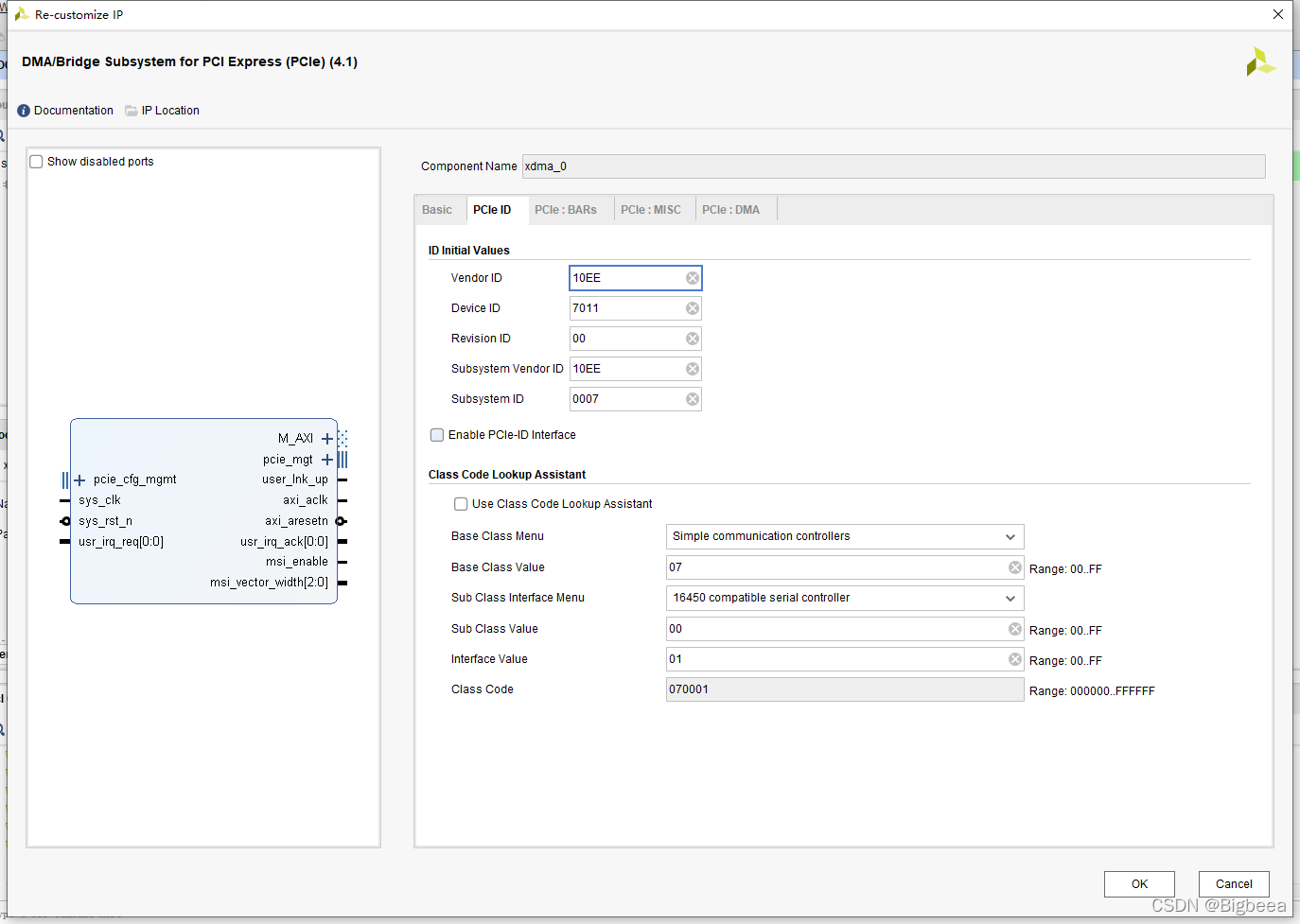

PCIe ID

这里是PCIe设备ID的设置,这与PCIe的协议有关,可以保持默认

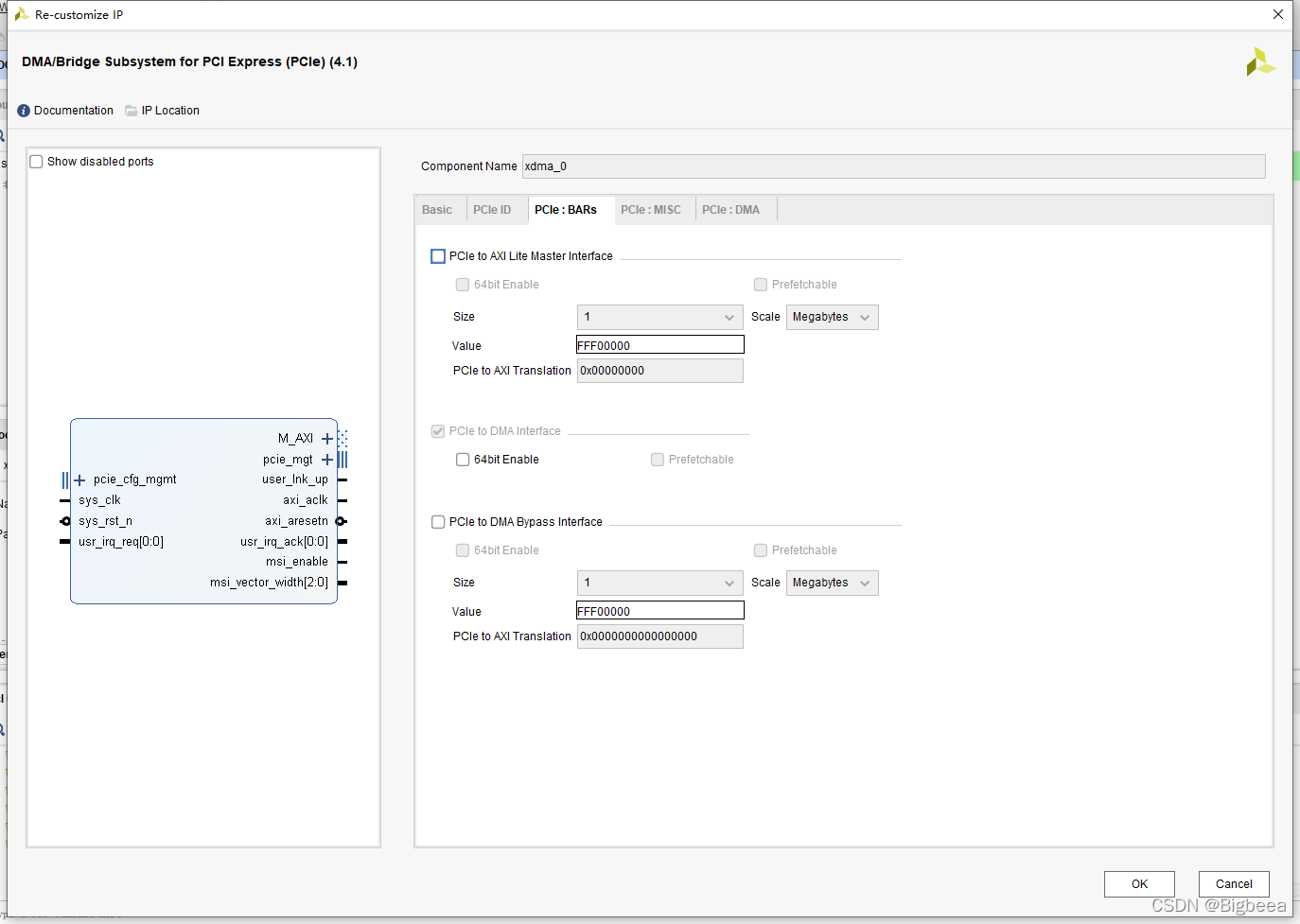

PCIe:BARs

对于XDMA IP有两个可选的BARs空间,勾选以后可以挂载两片新的存储空间,常用来做控制信息的交互。选择以后和M_AXI接口差不多。

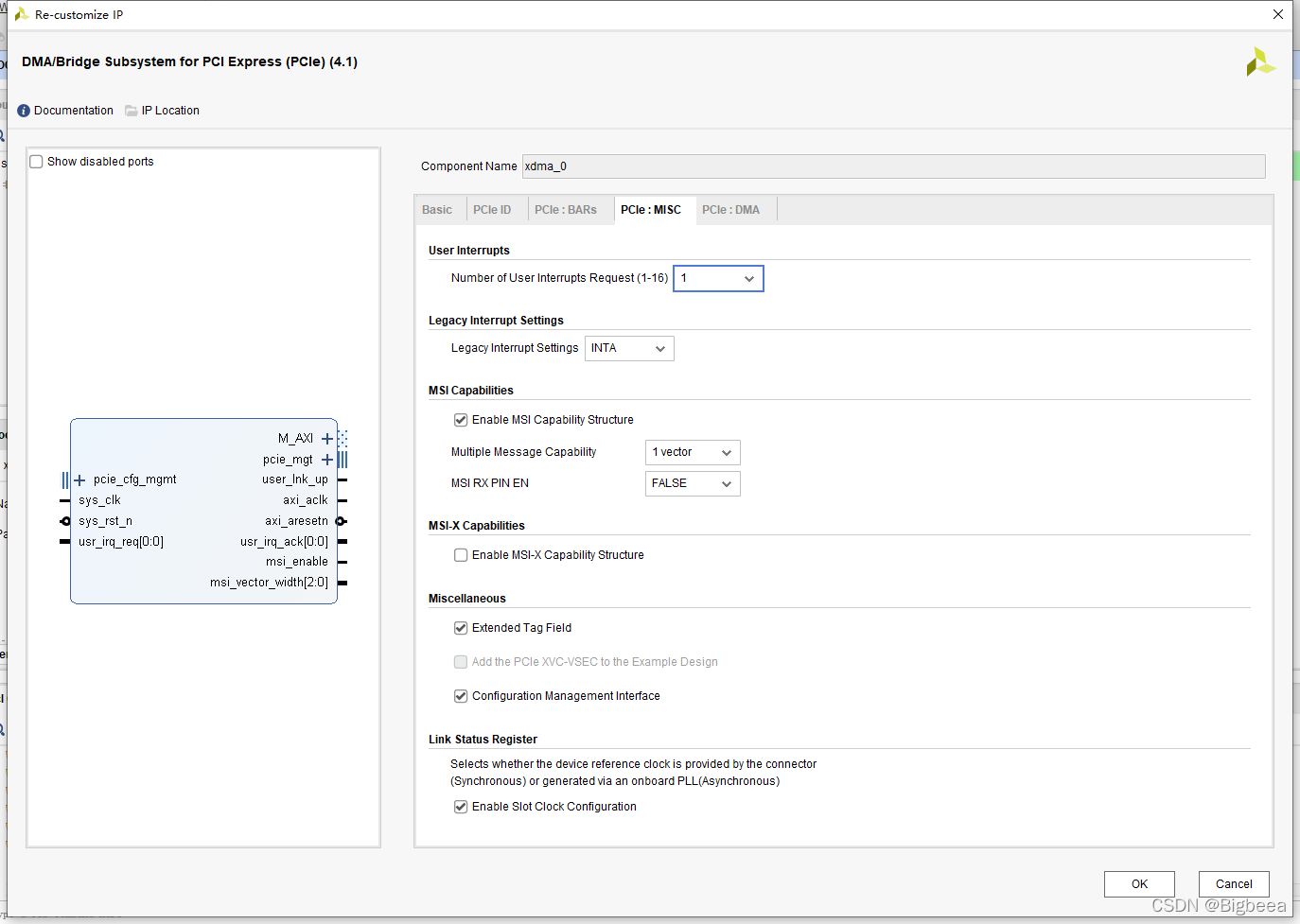

PCIe:MISC

使能中断啥的,

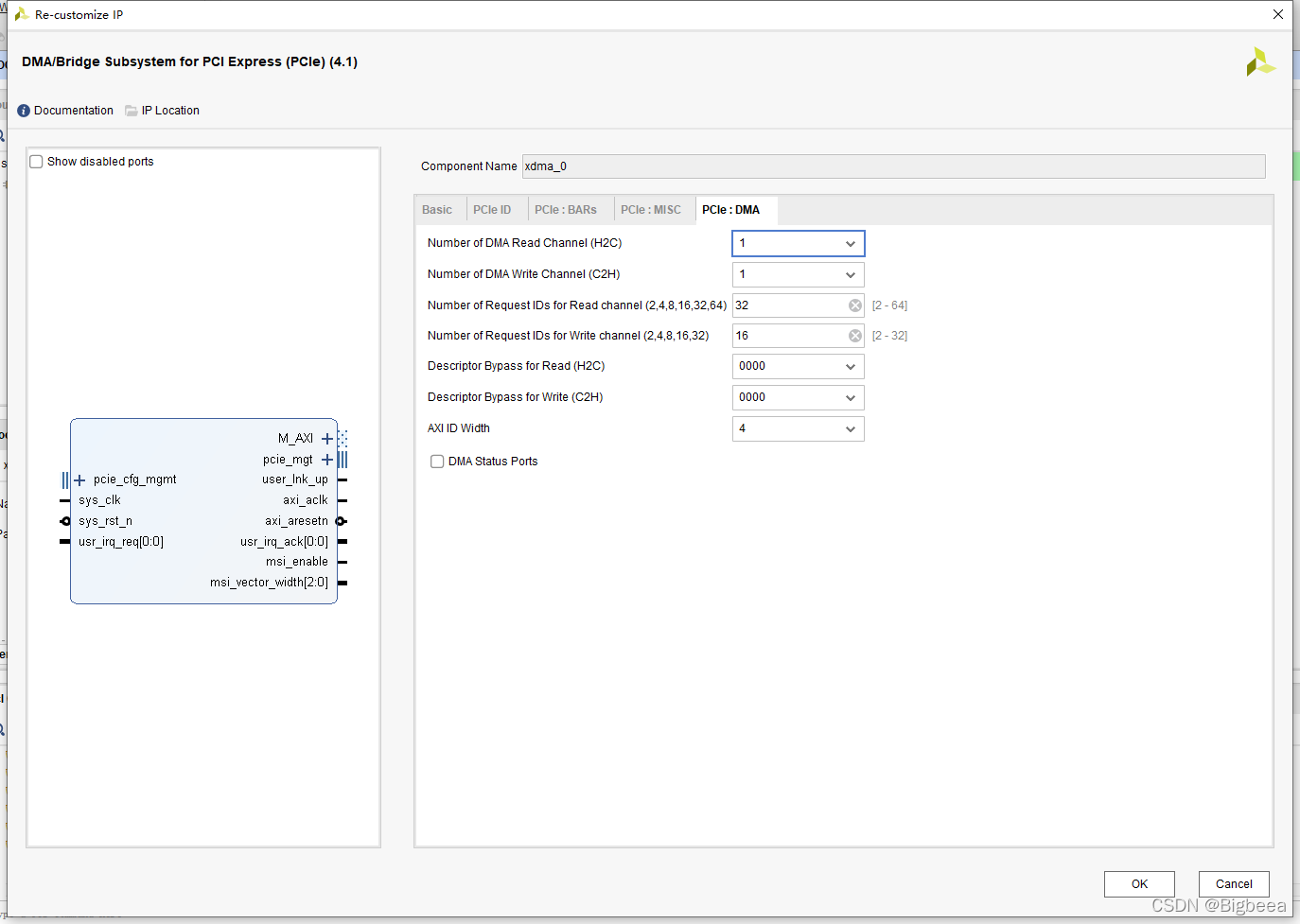

PCIe:DMA

DMA通道数,一般选择一个就够了,按照需求来吧

三、实现过程

工程搭建

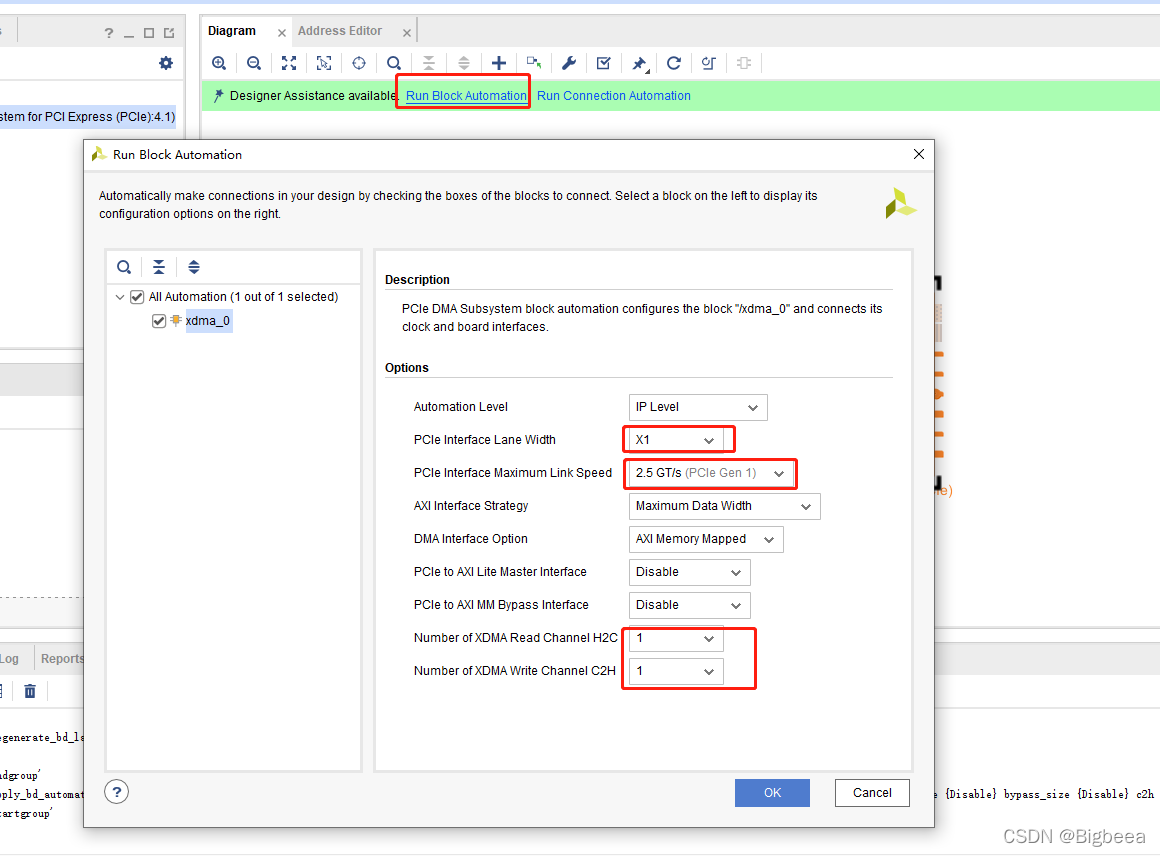

点击Run Block Automation ,按照IP配置再次配置一次。

为了进行测试可以添加一个BRAM进行存储数据,当然在实际的工程中这里可能需要用到DDR,反正就做一个简单的测试,把DDR挂在AXI总线上即可。

测试

测试要实现的话可以在官网下一个xdma的软件支持包,里面会包括驱动和能够访问PCIe总线的xdma_rw.exe文件,可以测试读写,将数据写进去或者读出来,当然在这个操作的过程中你可以可以在AXI总线上加一个debug进行监测。

四、参考资料分享

总结

文章讲的很简单,遇到了问题害得与硬件工程师协调处理。

1337

1337

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?