SystemVerilog中,为了是代码简洁、易记,允许用户根据个人需要使用typedef自定义数据类型名,常用的使用方法可参见“define和typedef区别”。但是在SystemVerilog引入面向对象编程后,经常会遇到在编写某个类或者类型的定义之前需要先使用对变量进行声明,往往这种情况下编译都会报错,为此本文示例typedef的另外一种用法,可以称之为“forward typedef”。

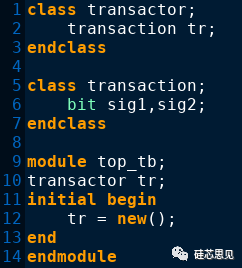

【示例】未使用forward typedef

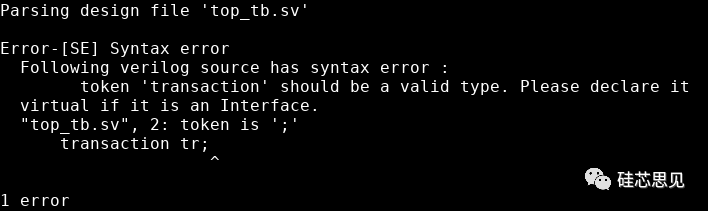

【仿真结果】

示例中,因为transaction的定义出现在使用该类型的transactor之后,所以在编译时,仿真器编译到transactor中的transaction时&

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8753

8753

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?