SystemVerilog的OOP编程中,经常需要使用super这个关键字,主要用于子类访问父类中的属性和方法。当然并不是在所有情况下都需要使用super,一般情况下如果子类对于父类中的属性或者方法进行overriden,那么此时如果要引用父类中被overriden的属性或者方法时,就需要明示super。下面通过示例说明super在SystemVerilog中非new方法(super.new的使用和执行可参考之前的一篇短文:【59】new的初始化顺序)中的使用。

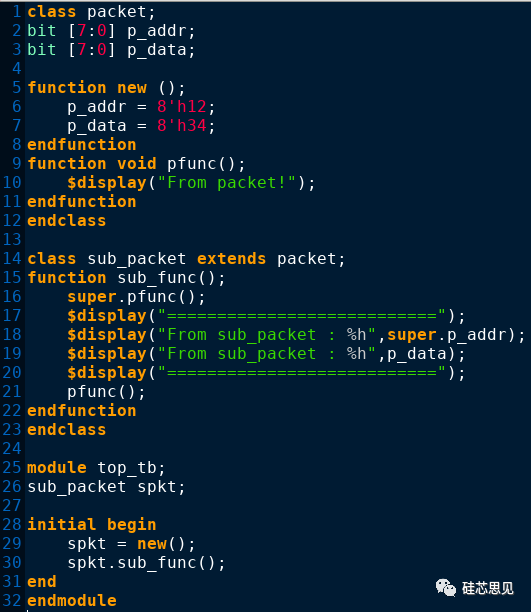

【示例】引用父类中未被overriden的属性和方法

【仿真结果】

示例中,父类中p_addr、p_data、pfunc分别在子类中被引用,因为子类中没有对于p_addr、p_data、pfunc的overriden,所以在子类中即可以像16行和18行那样直接使用也可以像19行和21行那样子不使用,即对于父类中在子类中没有overriden的属性和方法可以选择性的使用super关键字进行引用。

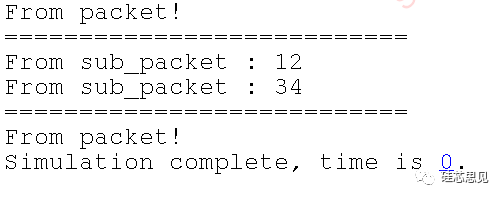

【示例】

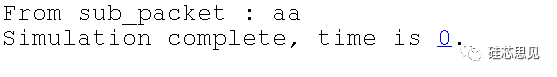

【仿真结果】

示例中子类sub_packet对于父类中packet中的p_addr、p_data、pfunc均进行了overriden,所以从仿真结果可以看出,在28行使用super.pfunc()调用的实际上是父类中的pfunc(),30行调用的p_addr实际上也是父类中的p_addr(即’h12),31行显示的p_data不是父类中p_data,因为子类对于父类中的p_data进行了overriden,所以此时在没有使用super关键字时,p_data为子类overriden后的。33行的原因同31行,这里不再赘述了。

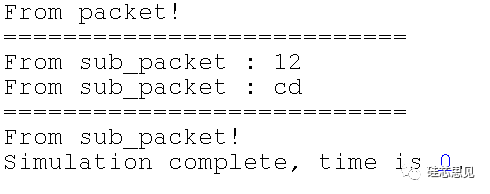

那么,有朋友可能会问,super如果访问的属性在父类中没有,在父类的父类中存在,还可以使用吗,我们一起看下例。

【示例】

【仿真结果】

示例中,16行访问的p_what定义于父类packet的父类base中,通过示例结果我们可以看到,通过super关键字可以访问未被重写的属性或者方法,不局限于当前类的父类,当然如果两个或者多个类之间不存在父子关系,那么是不能通过super关键字进行访问的。

更多内容请关注下面公众号!

本文纯属学习之用,欢迎指正文中不足,封面图片若有侵权,请及时沟通!

1259

1259

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?