本节熟悉axi的接口和通道信号。

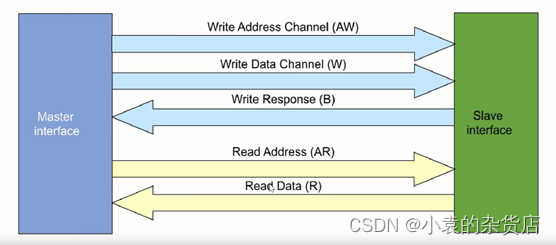

Axi有五个通道,每一个通道有不同的信号。读写分离,这是axi带宽高于ahb的根本原因。

图1描述了5个通道的信号流向,下面的完整的列出了axi每个通道的各个信号。

建议大家首先熟悉需要实现的信号,之后再了解其他复杂信号。

图 1

下面的表格详细说明了每个通道里面包含了哪些具体信号。如果这个信号需要在最后的RTL里面实现我会打上实现两个字,这些信号需要完整了解,不然代码会有难度。下表中红色的信号表示AXI3独有,蓝色的信号表示AXI4独有。

| B 通道信号列表 | ||

| 信号名 | 来源 | 描述 |

| BID[X:0] (实现) | slave | slave返回的写transaction的ID号 |

| BRESP[1:0] | slave | 从机响应类型 00 OKAY 正常访问成功。表示正常访问成功。还可以指示独占访问失败。 01 EXOKAY 独占访问。指示独占访问的读或写部分已经成功。 10 SLVERR slave的错误。 11 DECERR 解码错误。 |

| BUSER[X:0] | slave | 用户自定义信号 |

| BVALID (实现) | slave | B通道valid信号 |

| BREADY (实现) | master | B通道ready信号 |

| AW 通道信号列表 | ||

| 信号名 | 来源 | 描述 |

| AWID[X:0] (实现) | master | 写transaction的ID号 |

| AWADDR[31:0] (实现) | master | 写地址 |

| AWLEN[3:0]/ AWLEN[7:0] (实现) | master | 每次BURST或者一次transcation中传输的transfer次数,范围限制1~16(AXI3)(AXI4为1~256)。每次传输的突发长度为AxLEN[3:0] + 1(AXI4为 AxLEN[7:0] + 1) Burst传输有下面的规定: 对于wrap突发传输,突发长度仅能是2,4,8或16。 burst不能跨4KB边界。 所有的组件都不能提前终止一次突发传输。然而,主机可以通过STROBE来使非所有的写字节来减少写传输的数量。读burst中,主机可以忽略后续的读数据来减少读个数。也就是说,不管怎样,都必须完成所有的burst传输。 |

| AWSIZE[2:0] (实现) | master | 一个transaction中有多笔transfer,每笔transfer传输的最大字节数使用AWSIZE定义。每次的突发尺寸不能超过数据通道的宽度;若突发尺寸小于数据通道宽度,需要指定哪些位数是有效的。突发尺寸为2^AxSIZE[2:0],最大128byte。 |

| AWBURST[1:0] | master | 突发类型: FIXED(AxBURST[1:0]=0b00):固定突发模式,每次突发传输的地址相同,用于FIFO访问; INCR(AxBURST[1:0]=0b01):增量突发模式,突发传输地址递增,递增量与突发尺寸相关(传输过程中,地址递增。增加量取决AxSIZE的值。) WRAP(AxBURST[1:0]=0b10):回卷突发模式,和增量突发类似,但会在特定高地址的边界处回到低地址处(传输地址不会超出起始地址所在的块,一旦递增超出,则回到该块的起始地址),突发传输地址可溢出性递增,突发长度仅支持2,4,8,16。(和AHB差不多) 传输首地址和每次传输的大小对齐。最低的地址整个传输的数据大小对齐。地址空间被划分为长度[突发尺寸*突发长度]的块,即回环边界等于(AxSIZE*AxLEN)。 |

| AWCACHE[3:0] | master | AxCACHE[0]是可缓冲位,当该位置1时,可以延迟事务到达最终目的端的时间,可以决定响应是否可以来自中间端,或者必须来自终点从机。 AxCACHE[1]是AXI3中的cacheable,或者是AXI4中的可修改位。这个位表示终点的事务不必与源点的事务属性匹配。对于写操作,设置可修改位意味着多次不同的写操作可以合并,或者单次写操作可以分解成多个事务。对于读操作,设置可修改位意味这可以预取位置的内容,或者单次读取的值可以用于多个读取事务。 AxCACHE[2]为RA位。RA位表示在读操作时,建议进行事务分配,但不强制。如果AxCACHE[2]或AxCACHE[3]置位,那么事务必须从cache中查找,因为它被其他主机分配到了cache中。 AxCACHE[3]为WA位。WA为表示在写操作时,建议进行事务分配,但不强制。如果AxCACHE[2]或AxCACHE[3]置位,那么事务必须从cache中查找,因为它被其他主机分配到了cache中。 如果AxCACHE[1]没有置位,则AxCACHE[2]和AxCACHE[3]不能被置位。 |

| AWPROT[2:0] | master | AxPROT[0] ◦ 1 特权访问. ◦ 0 非特权访问 • AxPROT[1] ◦ 1 对非安全区访问 ◦ 0 对安全区访问 • AxPROT[2] ◦ 1 指令访问 ◦ 0 数据访问 |

| AWQOS[3:0] | master | QoS标识符 |

| AWREGION[3:0] | master | region标识符(当slave有多种逻辑接口时标识使用的逻辑接口) |

| AWUSER[X:0] | master | 用户自定义信号 |

| AWVALID (实现) | master | AW通道valid信号 |

| AWREADY (实现) | master | AW通道ready信号 |

| AWLOCK[1:0]/ AWLOCK | master | AxLOCK信号用于指示何时执行原子访问。 |

| W 通道信号列表 | ||

| 信号名 | 来源 | 描述 |

| WDATA[X:0] (实现) | master | 写数据 |

| WSTRB[X:0] (实现) | master | 当WSTRB的某个位为1时,说明对应wdata的一个Byte有效。 写数据总线的每8bit对应1bit的WSTRB,因此WSTRB[n]对应于WDATA[(8n)+7:(8n)]。 |

| WLAST (实现) | master | last信号(有效时表示当前为突发传输最后一个数据) |

| WUSER[X:0] | master | 用户自定义信号 |

| WVALID (实现) | master | W通道valid信号 |

| WREADY (实现) | slave | W通道ready信号 |

| WID[X:0] | ||

| AR通道信号列表(和AW描述一致,这里不赘述) | ||

| 信号名 | 来源 | 描述 |

| ARID[X:0] (实现) | master | 读地址ID |

| ARADDR[31:0](实现) | master | 读地址 |

| ARLEN[3:0]/ ARLEN[7:0] (实现) | master | 突发长度 |

| ARSIZE[2:0] (实现) | master | 突发尺寸(每次突发传输的byte数) |

| ARBURST[1:0] | master | 突发类型(FIXED,INCR,WRAP) |

| ARCACHE[3:0] | master | 存储类型 |

| ARPROT[2:0] | master | 保护类型 |

| ARQOS[3:0] | master | QoS标识符 |

| ARREGION[3:0] | master | 区域标识符 |

| ARUSER[X:0] | master | 用户自定义 |

| ARVALID (实现) | master | 读地址有效(有效时表示ARADDR上地址有效) |

| ARREADY (实现) | slave | 写有效信号(有效时表示从机准备好接收读地址) |

| ARLOCK[1:0]/ ARLOCK | ||

| R通道信号列表 | ||

| 信号名 | 来源 | 描述 |

| RID[X:0](实现) | slave | 读ID标签 |

| RDATA[X:0](实现) | slave | 读数据 |

| RRESP[1:0] | slave | 读响应 |

| RLAST(实现) | slave | 有效时表示为突发传输的最后一个 |

| RUSER[X:0] | slave | 用户自定义 |

| RVALID(实现) | slave | R通道valid信号 |

| RREADY(实现) | master | R通道ready信号 |

| 低功耗接口信号 | ||

| 信号名 | 来源 | 描述 |

| CSYSREQ | Clock controller | 该信号有效时,系统退出低功耗模式 |

| CSYSACK | Peripheral device | 退出低功耗模式应答信号 |

| CACTIVE | Peripheral device | 外设申请时钟信号 |

6812

6812

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?