前言

之前一直想要学习AXI协议,但是看到AXI协议那一堆的信号线和英文资料就望而却步。这里整理了自己学习AXI LIT协议和实现AXI LIT协议的记录,希望对和我一样想学习AXI协议的朋友有所帮助。

一、AXI LIT协议信号线介绍

AXI信号整体可以分为5大部分,分别是aw(write requset channel)、w(write data channel)、b(write response channel)、ar(read requset channel)、r(read data channel)。其中aw、w、b三个通道是写操作时使用,ar、r两个通道是读操作时使用。注意axi读写是可以独立工作的。

下面对AXI LIT各个信号线进行说明

| 名称 | 位宽 | 描述 |

| aw通道(write requset channel) | ||

| axi_awaddr | 根据自己设计存储大小定义 | AXI写操作的地址信息 |

| axi_awprot | 3bit | 访问的属性信息(access attributes)。协议中介绍:用于保护内存免受意外访问的影响。我的理解是每次写操作需要带上访问内存权限信息。具体详细使用可以参考axi完整协议。本设计没有使用 |

| axi_awvalid | 1bit | 与ready信号构成握手信号,axi通信的核心 表示写地址和写控制信息是否有效 |

| axi_awready | 1bit | 与valid信号构成握手信号 表示是否可以去接收地址和控制信息 |

| w通道(write data channel) | ||

| axi_wdata | 目前好像只有32bit/64bit | AXI写操作的数据信息 |

| axi_wstrb | data位宽/8 | 字节写信号。1字节=8bit 每一位表示一个字节数据是否有效 |

| axi_wvalid | 1bit | 与ready信号构成握手信号 表示写数据是否有效 |

| axi_wready | 1bit | 与valid信号构成握手信号 表示是否可以去接收数据 |

| b通道(write response channel) | ||

| axi_bresp | 2bit | 写响应信号(0表示不使用)表示此次写任务的传输结果。本设计没有使用 |

| axi_bvalid | 1bit | 与ready信号构成握手信号 表示写响应是否有效 |

| axi_bready | 1bit | 与valid信号构成握手信号 表示是否准备好去接收写响应 |

| ar通道(read requset channel) | ||

| axi_araddr | 根据自己实际设计定义 | AXI读操作地址 |

| axi_arprot | 3bit | 访问的属性信息(access attributes) |

| axi_arvalid | 1bit | 与ready信号构成握手信号 表示读地址和读控制信息是否有效 |

| axi_arready | 1bit | 与valid信号构成握手信号 表示是否可以去接收地址和控制信息 |

| r通道(read data channel) | ||

| axi_rdata | 32bit/64bit | AXI读操作的数据信息 |

| axi_rresp | 2bit | 读操作响应信号。标志此次读操作结果。本设计没有使用 |

| axi_rvalid | 1bit | 与ready信号构成握手信号 表示读数据是否有效 |

| axi_rready | 1bit | 与valid信号构成握手信号 表示是否可以去接收数据 |

注意:写操作时存在字节写,但读操作时不存在字节读的。我的理解写入存储可以指定某些位写入,但是读取存储本就可以全部读出来,然后选择需要位宽使用,没必要设计字节读。

二、握手机制介绍(AXI通信核心)

1.介绍三种常常使用的握手方式

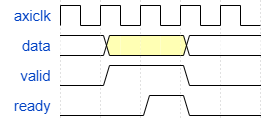

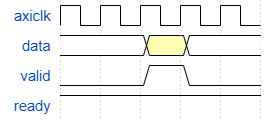

AXI握手的本质就是找valid和ready同时拉高的时间表示数据有效。valid和ready同时拉高几拍就表示有几次握手操作。个人不太推荐使用第三种握手方式,在实际使用中确实碰到过因为采用第三种握手方式而导致电路在某些情况下出现问题。

注意:AXI协议的五个通道是完全相互独立的,因此它们的握手其实是相互独立的,不存在依赖关系。

2.一次AXI LIT写操作流程

这里以一个取东西的过程说明我的理解:有这样一个情节,a需要让b帮忙去一个东西,a需要告诉b东西在哪里(addr),同时告诉b东西是什么(data);b在明白东西在那里后要告诉a表示已经知道东西在那里,b在知道东西是什么后也需要告诉a知道东西是什么了;当b在相应地方拿到东西后也需要告诉a自己已经拿到东西了。

这个过程设计了三次握手,对应了写操作的aw、w、b三个通道。a和b沟通地址的过程就是aw通过握手过程,a和b沟通东西是什么的过程就是数据握手的过程,b拿到东西告诉a的过程就是响应通道握手的过程。

继续这个例子,b如果要知道东西到底在那里,需要同时知道东西在那里并且知道东西是什么才行;而他先知道东西在哪里还是东西是什么其实并不重要,但必须是都知道才能正确取出东西。

因此在写操作时,其实无论是数据先握手还是地址先握手是没有关系的。但是响应通道(b通道)一定是在前两者同时握手之后才能握手。

三、AXI LIT协议实现

1.slave端设计

写操作

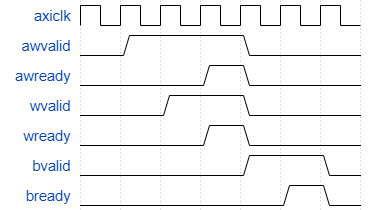

一次完成写操作包括aw,w,b三个通道的握手;其中aw和w通道是接收master端的valid信号,成功接收到valid信号后,产生ready信号,完成一次握手;而b通道则是需要在slave端产生valid信号,等待master端的ready完成一次握手并完整的完成一次写操作。(注意slave端在b通道产生valid信号前提一定是数据地址和数据信息已经正确接收。对于axi lit每一次写操作都需要b通道的握手)。本设计三个通道握手时序如下:

说明:这里做了一个小的偷懒,对于aw和w通道的valid握手,我是在awvalid和wvalid同时有效时,同时对两者握手,之后产生响应有效信号bvalid信号等待master端握手。这样控制起来相对简单一些。

假设把aw通道和w通道握手完全独立起来,这时,对地址信息,数据信息可能就需要一个fifo来存储每次握手信息,这样才不会导致数据错乱。

读操作

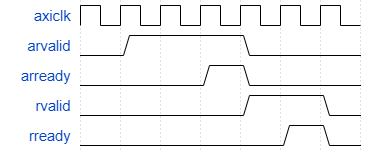

读操作在slave端相对简单一些,只需要得到地址相关信息并握手,正确取出数据后产生rvalid信号等待master端握手。握手时序如下:

2.master端设计

写操作

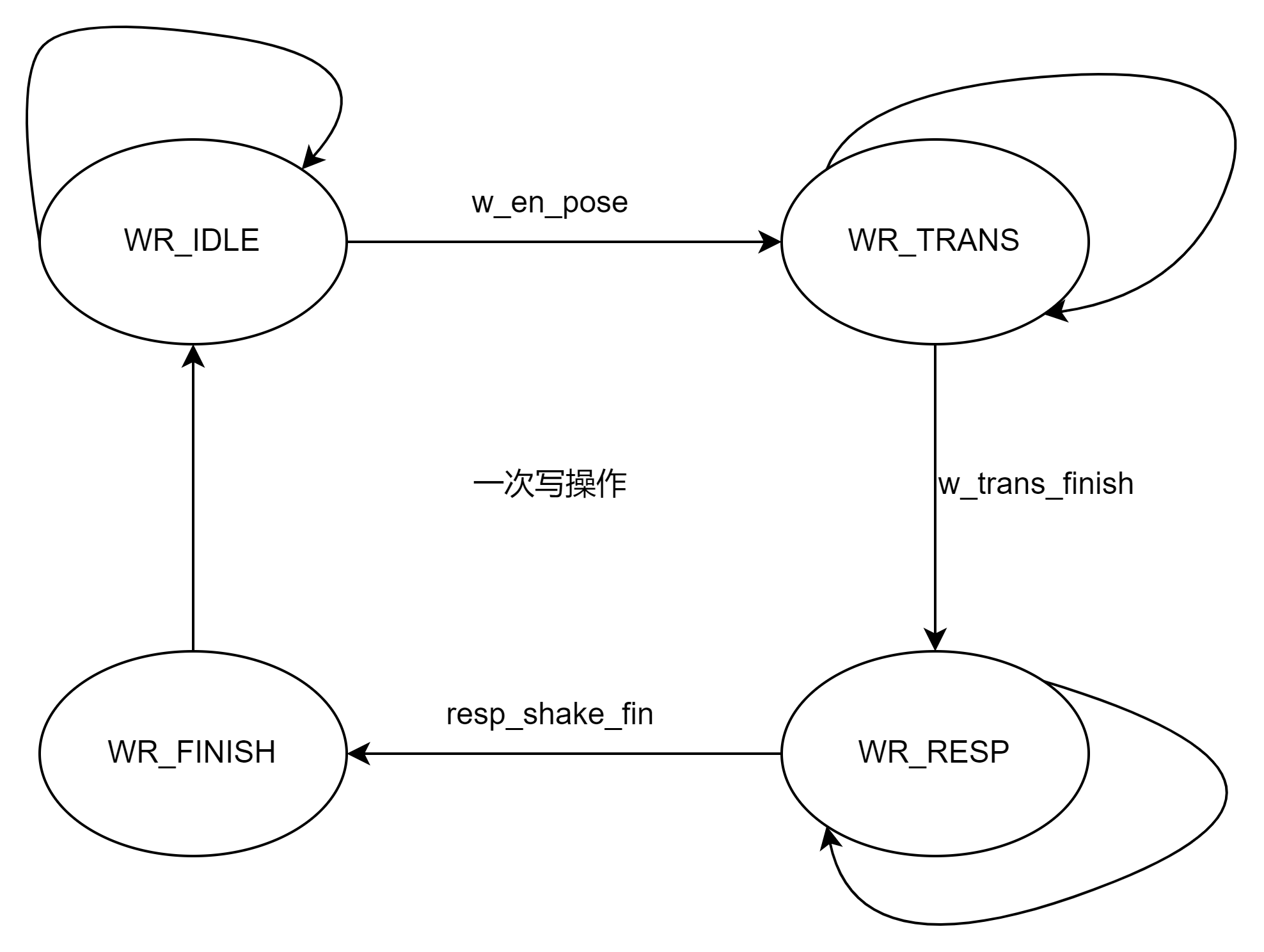

作为master端时关于AXI握手机制和作为slave端本质是一样的。这里设计了一个简单的状态机来控制一次完成的写操作。状态机如下:

WR_IDLE:空闲状态;WR_TRANS:数据地址传输状态;WR_RESP:等待响应状态;WR_FINISH:传输完成状态。

重点是从WR_TRANS状态跳转到WR_RESP状态状态需要aw,w两个通道都完成握手才行。

读操作

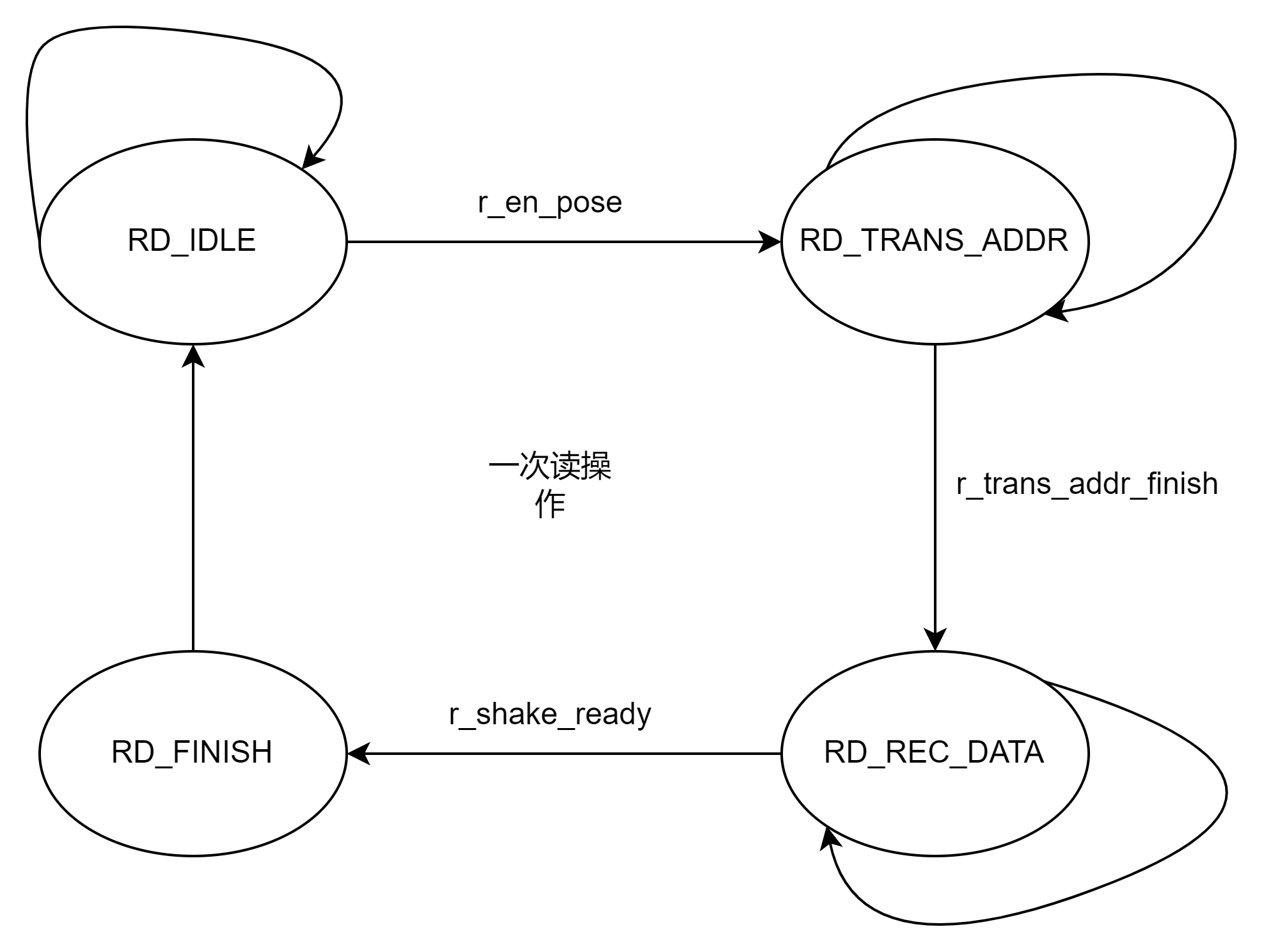

同样这里也设计了一个简单的状态机,如下:

这个状态机与写操作状态机类似,这里不做说明,具体可以参考工程。

整体代码工程如下,欢迎大家下载学习:【免费】使用Xilinxverificationip验证自己设计的axilitslavemaster端资源-CSDN文库

总结

了解AXI协议首先一定要理解它的握手机制和五个基本的通道。AXI LIT是最简单的AXI,每个通道的信号少了很多,我觉得很适合入门AXI协议学习。在这个基础上再去了解AXI4、AXI4-Stream会相对容易一些。

本文是我自己学习AXI LIT协议的一些总结,希望对大家学习axi协议有所帮助。同时文中可能存在一些错误,欢迎大家指正。

4574

4574

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?