微信公众号上线,搜索公众号小灰灰的FPGA,关注可获取相关源码,定期更新有关FPGA的项目以及开源项目源码,包括但不限于各类检测芯片驱动、低速接口驱动、高速接口驱动、数据信号处理、图像处理以及AXI总线等

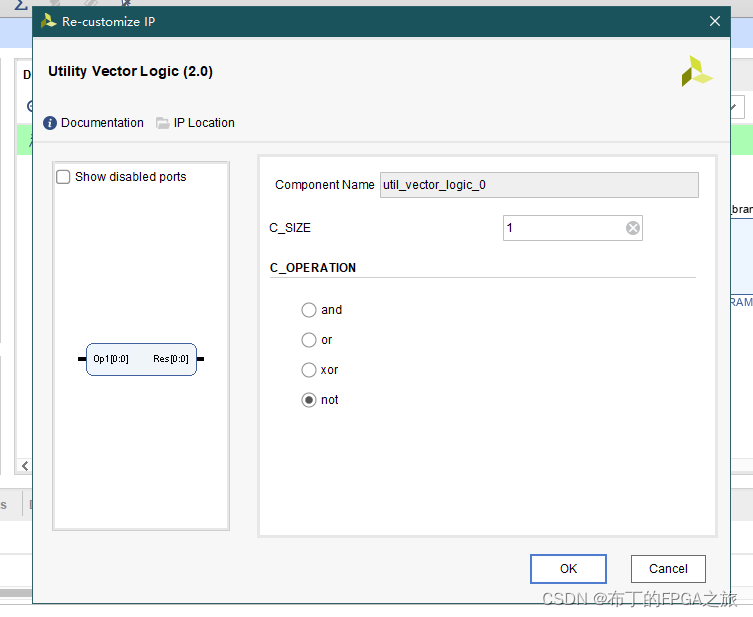

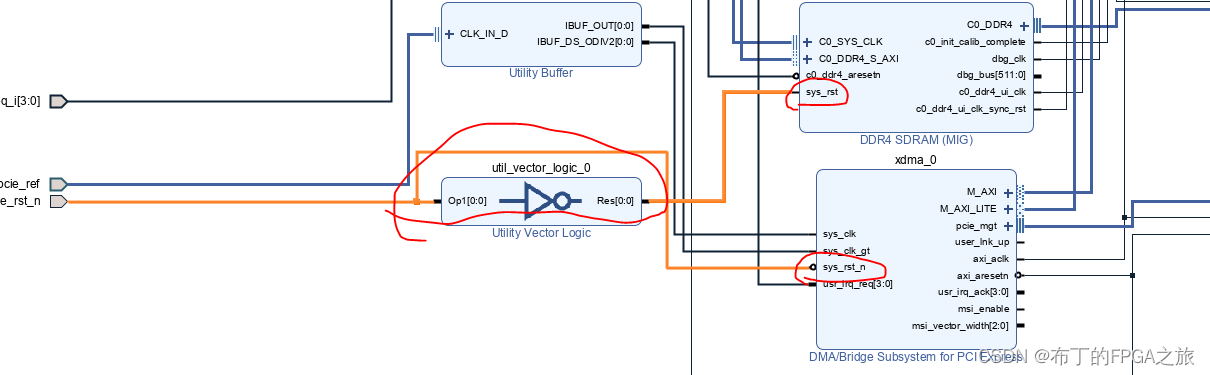

1、Utility Vector Logic在Block design

可用于向量的与、或、异或、非。

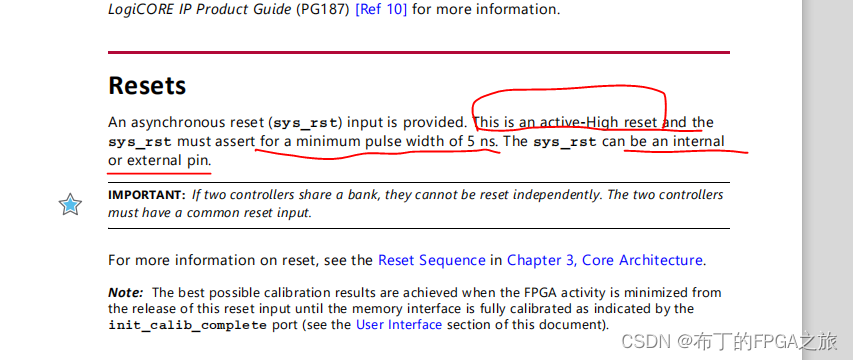

比如:复位信号,外部提供低有效的信号,DDR MIG IP复位高有效,可使用此IP转换输入MIG

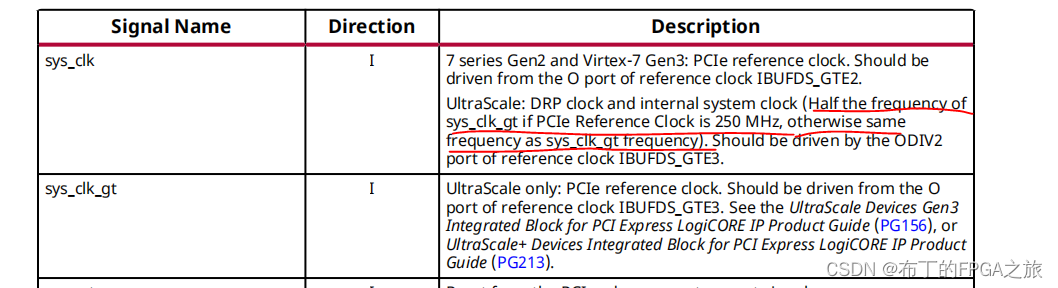

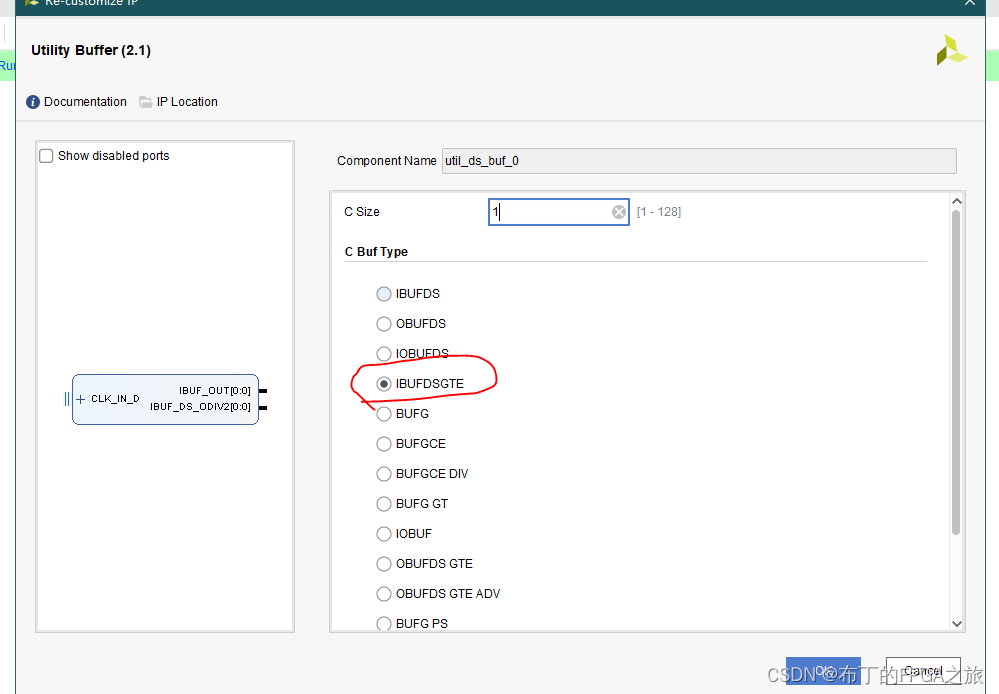

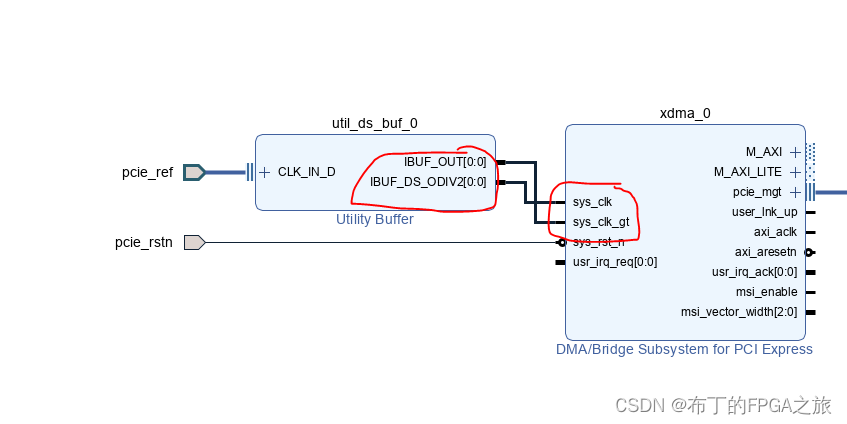

2、Utility Buffer

在Block Design中可以用作IBUFDSGTE,千兆收发器缓冲器

可用于PCIe XDMA的差分时钟的输入处理

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?