了解HLS的第一步是熟悉FPGA的构造,因为很多HLS的优化都是和这些构造特点息息相关的。过去几十年来,FPGA变得越发大而复杂,也加入了片上内存、自定义数据路径,高速I/O,和多核处理器等等精密结构。

FPGA由一个可编程逻辑模块的矩阵和与之相连的内存组成,通常这些模块是以查找表(LUT)的形式存在,也就是说把地址信号输入进去,对应内存位置的内容会直接被输出出来。 一个N位查找表可以以一个N位输入真值表的方式来表示。

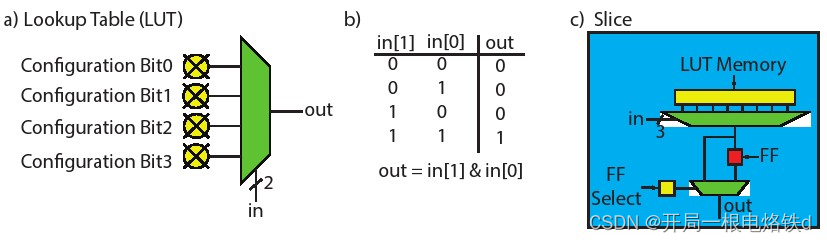

上图中的a)部分是一个2位输入查找表,共有2^2配置比特。使用者通过编写程序来控制这些比特以实现某种功能。b)部分是一个2位输入AND门的真值表,通过对应4个可能的结果产出(out一列),我们可以把a中的2位查找表编写成b中的AND门,即四个查找表输入依次对应b中的00,01,10,11。按照这个模式编写查找表,我们可以轻松的改变它的功能,让它充当我们需要的部件。对于小的布尔逻辑(Boolean),这样的编写方式更加的灵活高效。实际中的FPGA大多使用4-6位输入的查找表作为运算基础,一些大型FPGA内甚至有几百万个这一级别的查找表。

触发器(FF) 是FPGA最基本的内存单位,通常触发器是配有查找表的,这样是为方便查找表之间的复制与组合。在这基础上再加入一个规定它们的函数(例如全加器),就可以创建一个更为复杂的逻辑单位,称为可配置逻辑块(CLB) 或 逻辑矩阵块(LAB)。有些设计工具中还会把它称作片(Slice)。为避免歧义,我们将在下文中用slice作描述,这样读者可以对在Vivado设计工具中出现的Slice更加熟悉。一个slice是几个查找表,触发器,和多路复用器(MUX)组合到一起而形成的更强大的可编程逻辑单位。 每个slice需要的小部件数视FPGA的架构而变,但总体来说每个slice真的只包含不多的几个部件。图1.1中的c部分就是由1个三位输入查找表和1个触发器组成的slice。slice可以变得更加复杂一点,比如加入全加器。FPGA内部通常有一些定义好的全加器slice,这看起来有点违背FPGA的"可编写性"–它只可以执行加法操作。但实际上使用全加器在硬件设计中太过于常见,把所有的全加器每次重新编写成一个slice会降低效率。灵活性和高效综合考虑,一些被配置好的slice是一个对整个系统有益的设计。

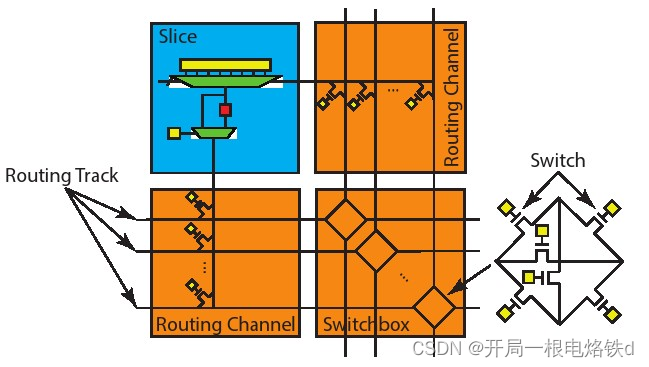

可编写的互联是FPGA最关键的特性之一,它能提供一个slice之间更灵活的连线网络。slice的输入与输出全都与连线通道相连,连线通道也是通过配置比特来决定每个slice的输入输出通向哪里,而通道本身则与开关盒相连。开关盒由很多传输晶体管充当的开关所组成,它的工作便是连接通道与通道。

图1.2展示了一个slice,连线通道和开关盒之间的连接方式。slice的每个输入输出都应与通道中的一条路线相连。所谓路线,我们可以简单的把它想成一跟比特层级的跳线,在物理层级上这条线路是由传输晶体管构成的,同样具有可编写性。

开关盒像是一个连接矩阵,沟通不同连接通道中的各个路线。FPGA一般有一个2D的形式,能给使用者一个大概的2D计算模型,我们称之为岛状结构。在岛状结构里,每个slice都是一个逻辑岛,岛与岛之间通过连线通道和开关盒相连。在这里每个开关盒在上下左右四个方向连接了四个连线通道。连线通道和开关盒中的所有开关都通过使用者的编写控制着逻辑部件之间的联系。

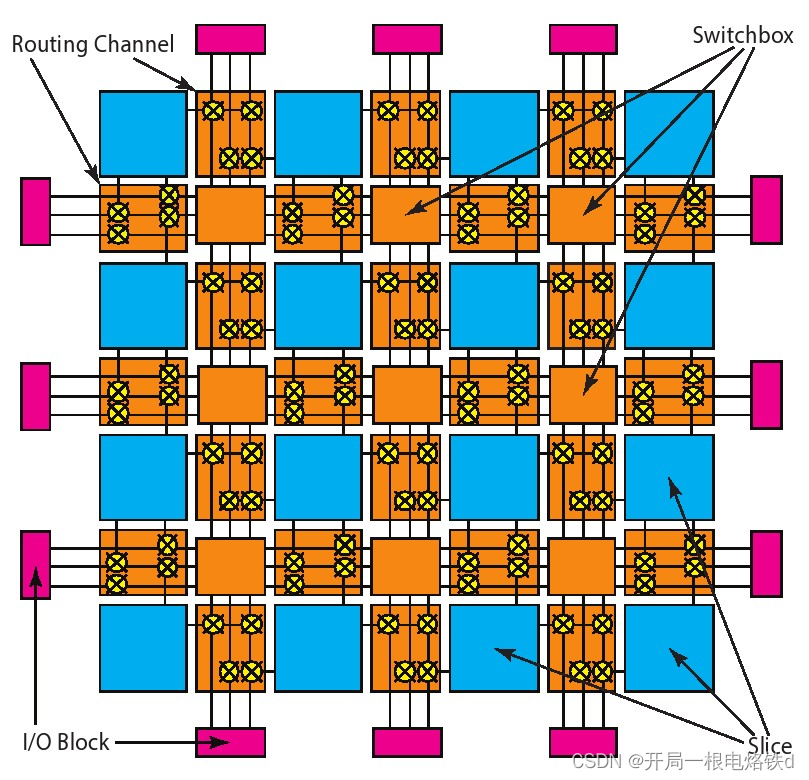

图1.3提供的是一个更概括性的结构互联,可以比较清楚的看到各部分之间的物理连接方式。FPGA的逻辑部分通过一些IO模块与外部设备相联系,像微控制器(通过AXI接口连接片上ARM处理器 ),传感器(通过A/D接口连接天线),作动器(通过D/A接口连接电机)都是可以实现的。近来发展的FPGA又集成了自定义片上I/O处理器,像内存控制,无线收发,模拟与数字转换器这类的装置。

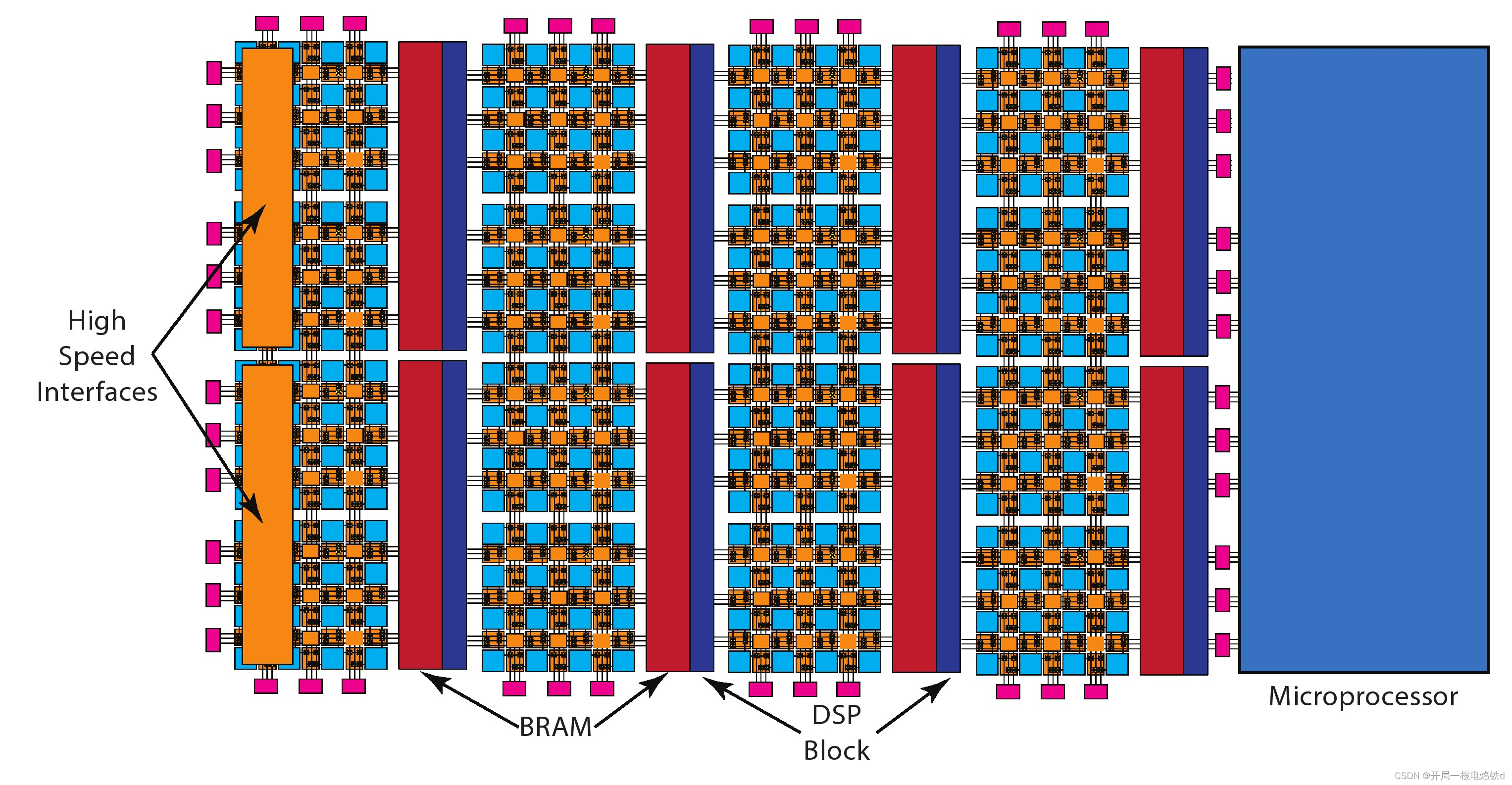

我们说到FPGA上要承载的晶体管变得越来越多,这也是FPGA上多了很多预配好的资源的原因。这部分硬件用于完成特定工作。很多设计都需要大量的加法和乘法,因此FPGA厂商把这部分的内容预配好以直接使用。像DSP48数据路径已经被用一种高效的方法预配好,添加了乘法、加法、乘积、逻辑操作等一系列算数。对于DSP48这样的模块来说,它们依旧保留了一定的可编写性,但不像其他可编程逻辑那样完全灵活。这样综合而言,用户在DSP48这样的模块上进行乘法这样的操作会比重新编写高效的多。所以我们说灵活性和效率有时候是此消彼长的。现代FPGA会含有成百上千个DSP48模块,如图1.4所示。

块RAM(BRAM)是另一个预配好的模块。BRAM是一个支持多种内存形式和接口的可配置随机储存器,可以储存字节,对字,全字,双字等等等。BRAM还可以把这些数据传给本地片上总线(与可编程逻辑交流)或处理器总线(与片上处理器交流)等等接口。总体来说它有两个功能,一是芯片上各部分的数据转移,二是储存大一些的数据集。slice经过编写也可以储存数据(通过触发器),但这样做会增加额外消耗。

| 属性 | 外部内存 | BRAM | 触发器 |

|---|---|---|---|

| 数量 | 1-4 | 几千 | 几百万 |

| 单个大小 | GB级 | KB级 | bit级 |

| 总量 | GB级 | MB级 | 100KB级 |

| 宽度 | 8-64 | 1-16 | 1 |

| 总带宽 | GB每秒 | TB每秒 | 100TB每秒 |

表1.5:三种形式内存存储比较。外部内存存储密度最高但带宽有限,触发器拥有最好的带宽但储存容量太小,BRAM则像是两者之间的中间值。

一块BRAM通常有大约32000比特的储存容量,可以以32000 x 1比特,16000 x 2比特,8000 x 4比特等等形式存在。串联在一起可以拥有更大的容量,Vivado工具可以完成这方面的配置,而Vivado HLS的优势也在于这里,设计者不再需要考虑这一层级的细节。通常BRAM和DSP48放置在一起,对于HLS设计来说,我们可以直接把BRAM想成一个寄存器堆,它可以直接输出到一个自定义的数据路径(DSP48),可以与处理器交流,也可以像可编程逻辑上的数据路径传输数据。

表1.5是一个不同内存形式比较的表格。如表格所示,所有触发器最后可以形成一个几百KB的储存,它们每个周期都可以被读写所以总带宽非常的大,但很显然他们的储存容量不尽如人意。BRAM在不牺牲很大带宽的前提下,提供了更大的储存密度。带宽的牺牲主要在于每个周期BRAM只有1-2个入口可以被接通。外部内存对于带宽的牺牲更大,但提供了最大的容量。把应用数据放在哪里是非常关键的一个设计决定。Vivado HLS工具也允许设计者清楚指明到底要将这段数据放在哪里。

片上晶管的繁多也丰富了我们的预配资源,片上的处理器其实就是一个很好的代表。现如今的高端FPGA会含有4个甚至更多的微处理器(比如ARM核心),小型的FPGA上附有一个处理器也变得很常见。处理器使芯片有了运行操作系统(比如Linux)的能力,它可以通过驱动和外部设备交流,可以运行更大的软件包比如OpenCV,可以运行更高级的语言(比如python)并以更快的速度运行。处理器经常成为了整个系统的控制者,协调了各方之间的数据转移,也协调了各个IP核心(包括用HLS自定义的IP核和第三方IP核)和板上资源的关系。

注:本文摘自FPGA并行编程,仅供学习参考

本文深入介绍了FPGA的基本构造,包括查找表、触发器、可配置逻辑块和可编程互联。FPGA的灵活性源于其可编程逻辑模块和内存,如查找表和触发器,以及预配置的资源如DSP48和BRAM。BRAM提供了介于触发器和外部内存之间的存储能力,而DSP48优化了乘法和加法等计算。FPGA的优化往往涉及到这些结构的高效利用。此外,现代FPGA还集成了处理器,增强了芯片的计算和控制能力。

本文深入介绍了FPGA的基本构造,包括查找表、触发器、可配置逻辑块和可编程互联。FPGA的灵活性源于其可编程逻辑模块和内存,如查找表和触发器,以及预配置的资源如DSP48和BRAM。BRAM提供了介于触发器和外部内存之间的存储能力,而DSP48优化了乘法和加法等计算。FPGA的优化往往涉及到这些结构的高效利用。此外,现代FPGA还集成了处理器,增强了芯片的计算和控制能力。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?