目录

在介绍DDR的PCB设计之前给大家介绍一下T点拓扑和菊花链拓扑。

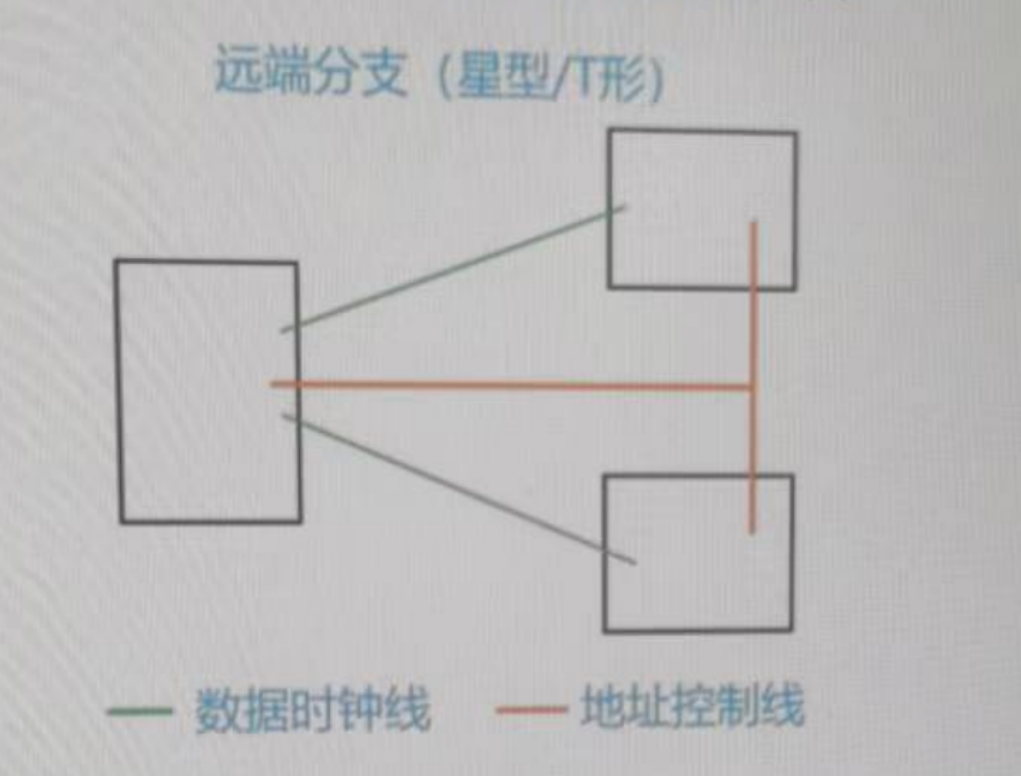

T点拓扑(T-Topology)

T点拓扑是一种经典的DDR布线结构,常用于多负载(如双Rank或四Rank内存)场景。其核心思想是将主控(Controller)的信号线通过一个中心点(T点)对称分支到多个内存颗粒,形成类似“T”字的布局。

特点与优势:

- 对称性:T点两侧的分支走线需保持长度和阻抗严格匹配,减少信号反射和时序偏差。

- 高兼容性:适用于高密度、多负载的DDR设计,如多Rank配置,确保信号同步性。

- 阻抗控制:T点附近需优化阻抗匹配,通常要求分支长度不超过信号波长的1/4,避免信号完整性(SI)问题。

局限性:

布线复杂度高,需精确计算分支长度差异(如±50mil以内)。高频(如DDR4/5)下,T点容性负载累积可能影响信号边沿速率。

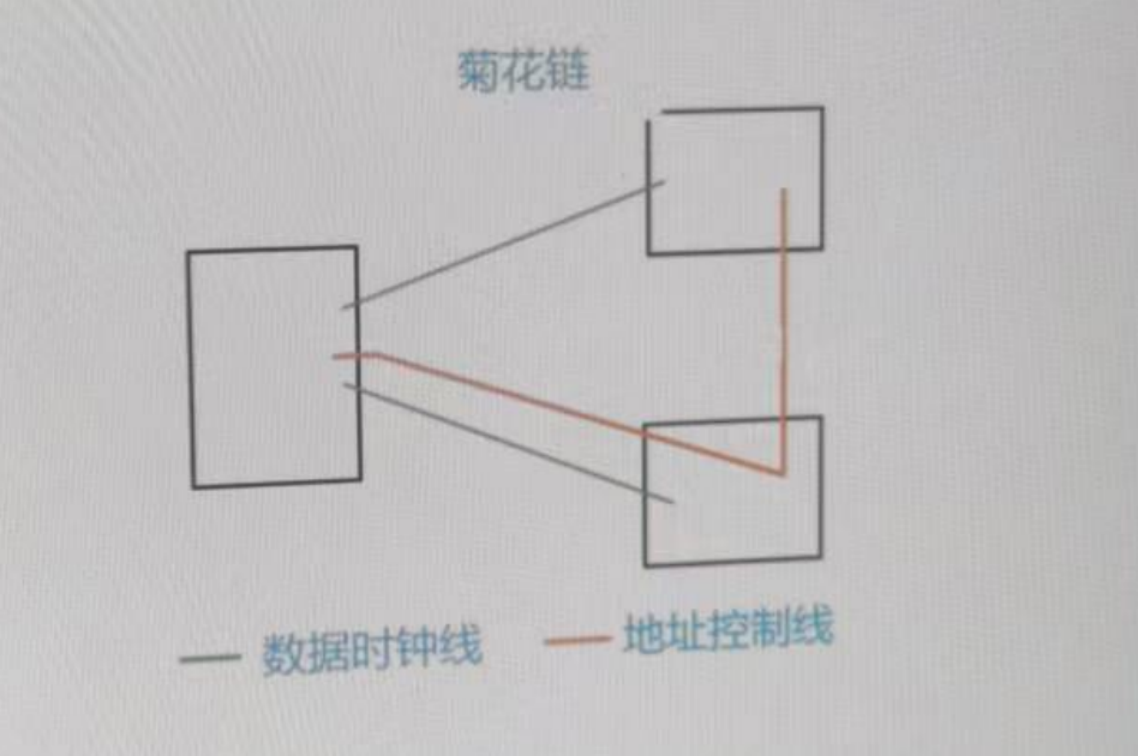

菊花链拓扑(Daisy Chain)

菊花链拓扑是一种串联型布线方式,主控信号依次穿过多个内存颗粒,最终通过末端电阻(Termination)完成阻抗匹配。

特点与优势:

简化布线:走线路径连续,减少分支,适合单Rank或低负载场景(如LPDDR设计)。

低延时:信号路径单一,时延一致性较好,适用于高速信号(如DDR5)。

空间节省:无需对称分支,布局更紧凑,适合小型化PCB设计。

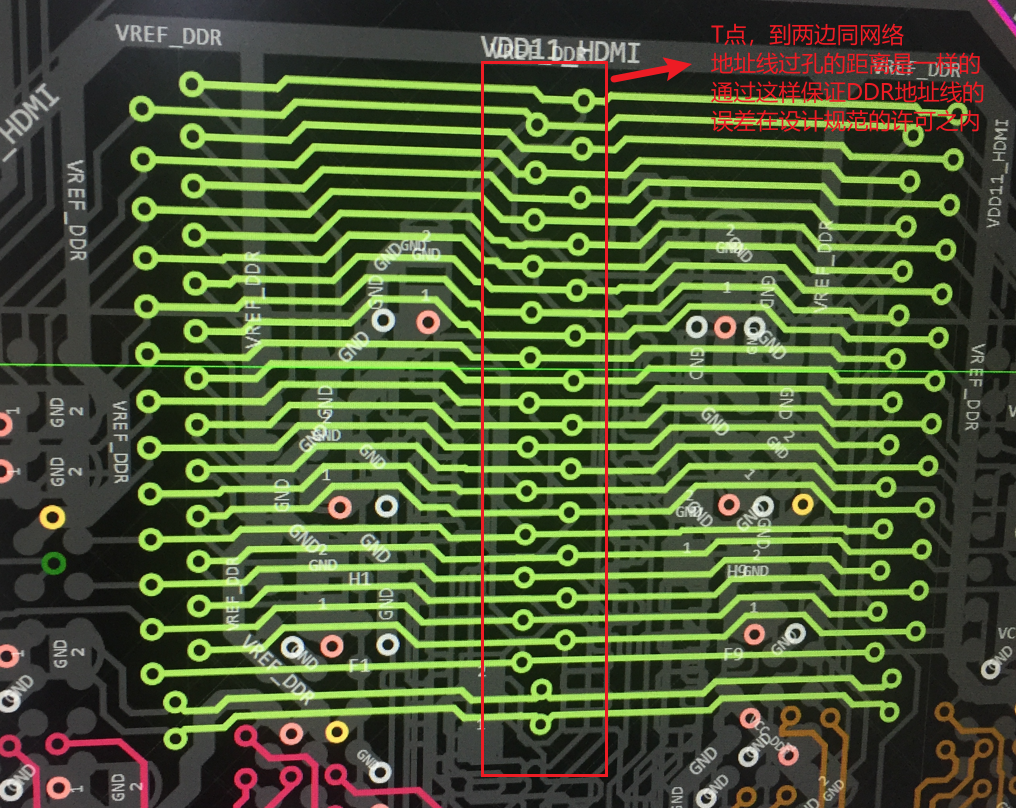

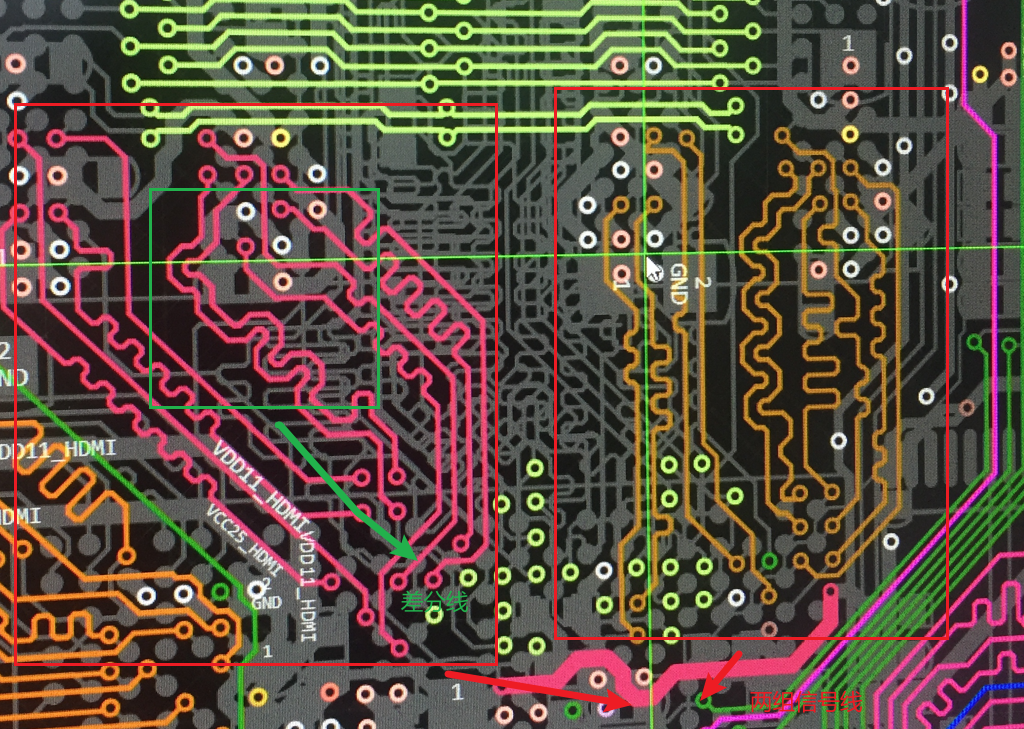

两片DDR的T点设计

在了解了这些之后,我们来一起看一下两片DDR的T点应该怎么设计,下面按照绘制的顺序介绍。

首先,先对DDR进行扇孔,对地址线架小天梯。

然后拉两组信号线,需要注意的是,数据线一定要同组同层进行走线,一般和小天梯在同一层处理。这里说的地址线和数据线都属于高速信号线,需要控3W进行走线,结束之后需要等长,等长误差需要控制在mil以内。一般每组信号线中都有一对差分线,差分线距离其他的线要有15mil以上的间隔。

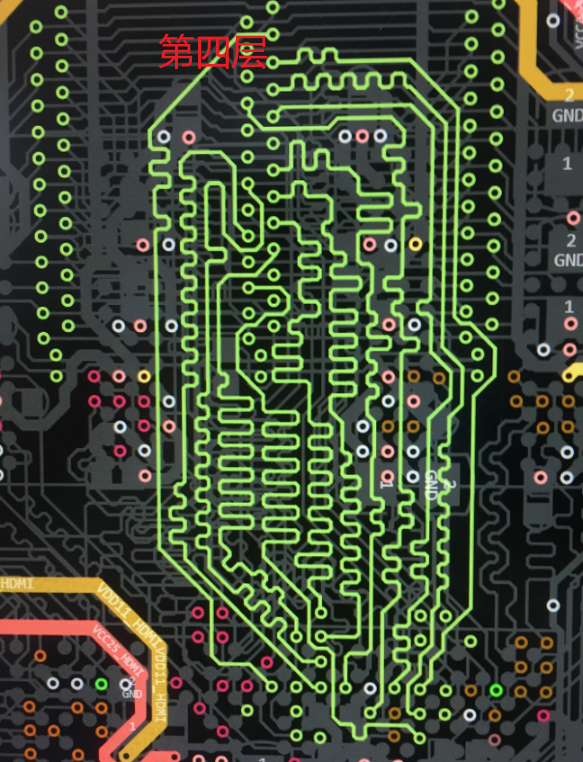

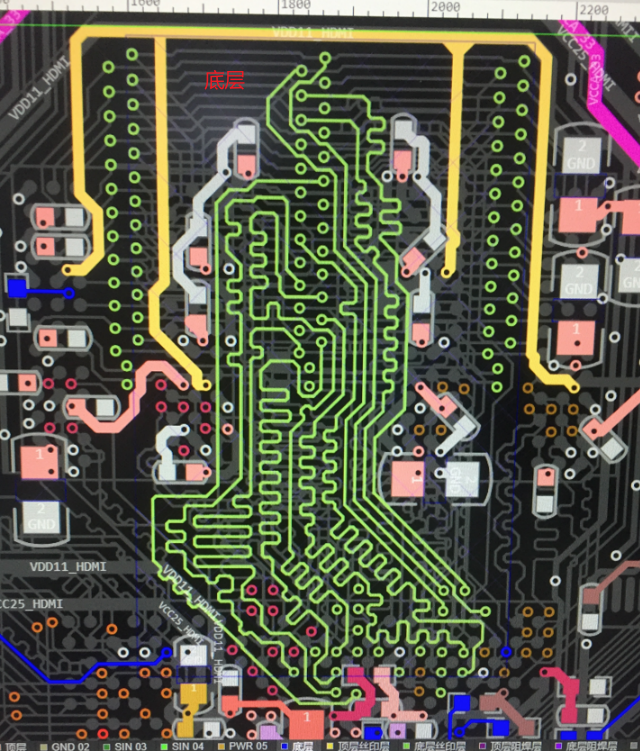

一般来说,两片DDR至少需要6层的叠层设计,如果叠层设计按照顶层-地层-信号层-信号层-电源层-底层(假八)这样来设计的话,地址线需要在顶层,第四层和底层走完(因为第三层走了信号线和小天梯)

1509

1509

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?