ROM只读存储器IP核的使用

实验简介

本文纯属学习笔记,使用的FPGA是Xilinx的XC7A35TFGG484-1,使用Vivado调用ROM IP核来实现读取数据已经存储的波形数据的效果。使用软件生成波形数据后将数据文件加入工程中,然后在工程中使用ROM读取文件中的数据并观察读取后的波形数据。

操作方法

一、在IP Catalog中搜索RAM选择Block Memory Generator

二、波形数据生成

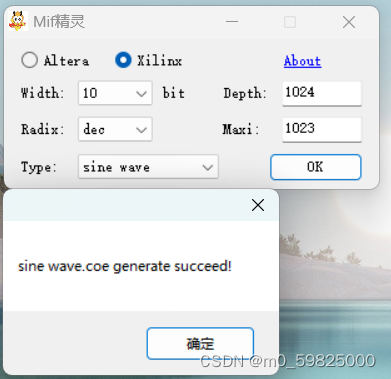

这里使用Mif精灵生成一个位宽为10bit 数据长度为1024个的正弦波波形数据为.coe文件,将其放在工程目录下

三、配置过程

Basic

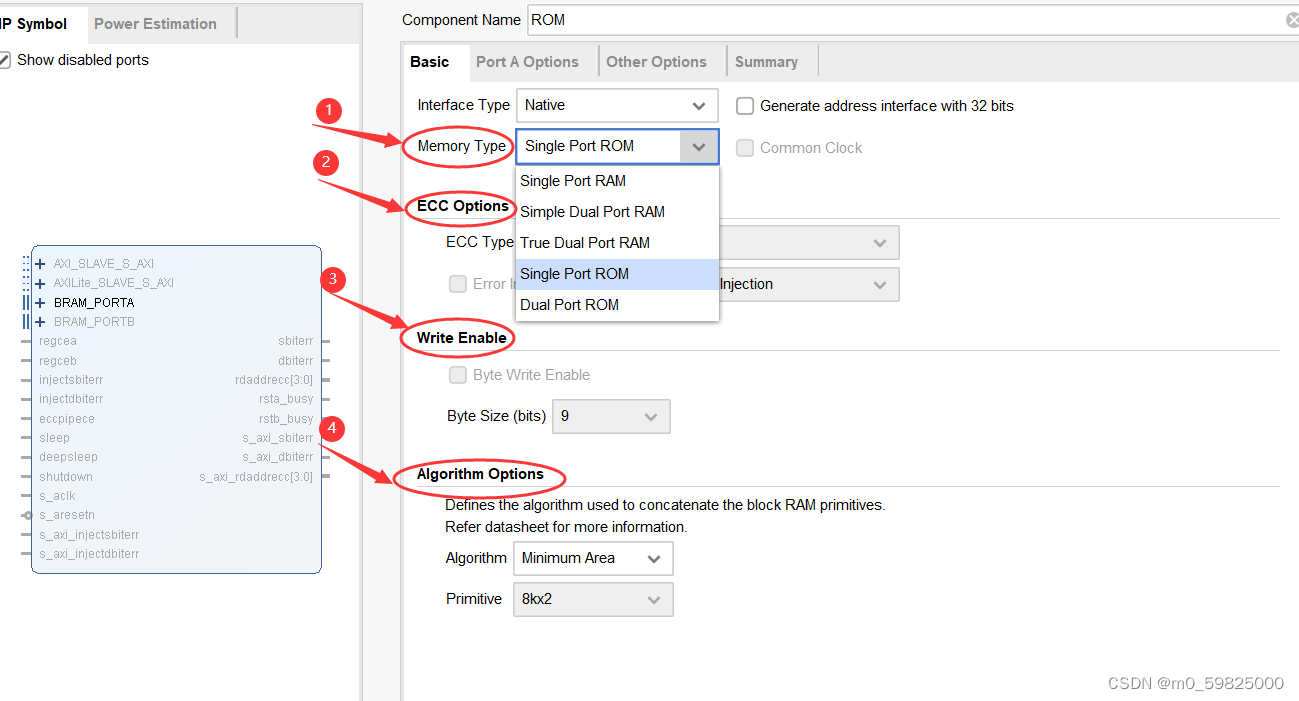

①在Memory Type中选择Single Port ROM

Memory Type中的Signal Port ROM为单口ROM

Dual Port ROM为双口ROM,在勾选为双口ROM时右侧Common Clock会被点亮,及两个端口读取数据是否使用相同的时钟。

②ECC Option为校验设置:保持默认

③Write Enable为写使能(在ROM时不可用):及使能后一帧数据变为选择的9位,最高位一帧变为数据使能,若为1则同意写入ROM 为0则不写入

④Algorithm Options为算法设置:根据不同场景对ROM使用的块进行组合,这里保持默认

Port A Options

①Port A Width端口A位宽:位宽的大小与上文生成的数据时的每一帧数据的宽度大小是一致的,这里是10位的宽度

②Port A Depth端口A深度:深度就是数据的长度,上文生成的数据有1024个数据,所以这里是1024

③Enable Port Type使能引脚:使能引脚及在读取之前需要将En引脚置1,这里直接选Always ENabled就行

④Primitives Output Register输出寄存器:勾选此选项及数据在从ROM读出来之后需要先到寄存器然后再从寄存器中读出来,及时钟需要再多一拍。读数据给出地址后的第一个时钟数据从ROM传输到寄存器中,第二个时钟才会再从寄存器中读出来

其他的保持默认即可

Other Options

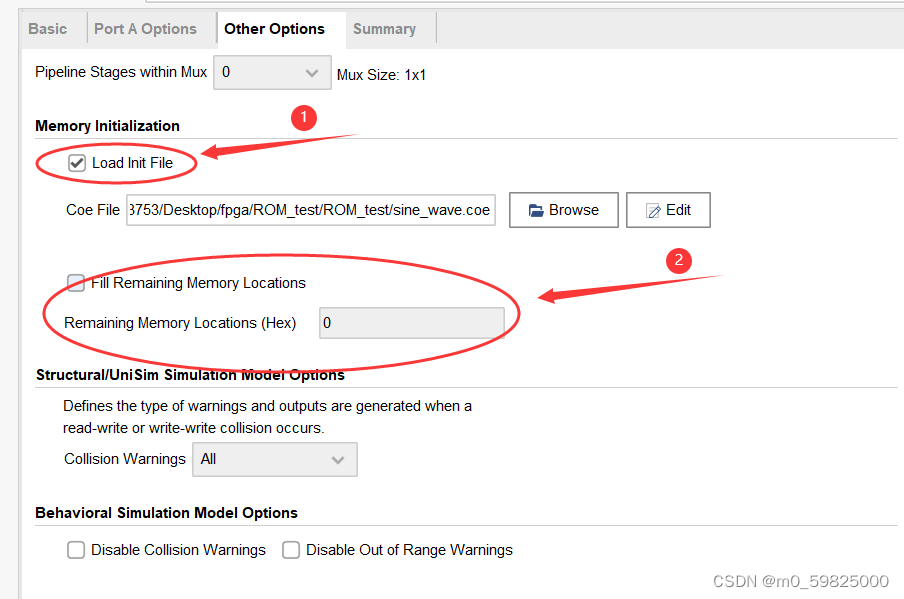

ROM为只读存储器,读取的数据来源①Load Init File的方式一个是读取已经生成好的数据文件,还有一个就是自己编写需要读取的文件。这里我们已经生成好了文件,所以直接Browse就可以了

②Fill Remaining Memory Locations填充剩余内存位置:该选项为功能为若IP设置中的Deep长度大于生成文件中的数据的长度,可以选择对其他未定义的数据进行填充,填充值可以随意设置,默认为0

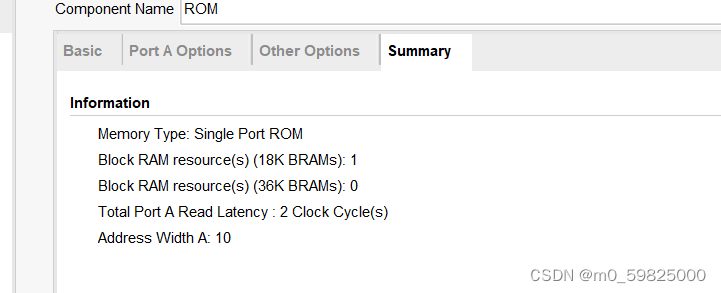

Summary

该模块总结你已经使用的资源情况,从该模块中也可以看出从开始读数据到读出来需要有两个时钟周期的延时

之后点击OK然后点Generate就可以了

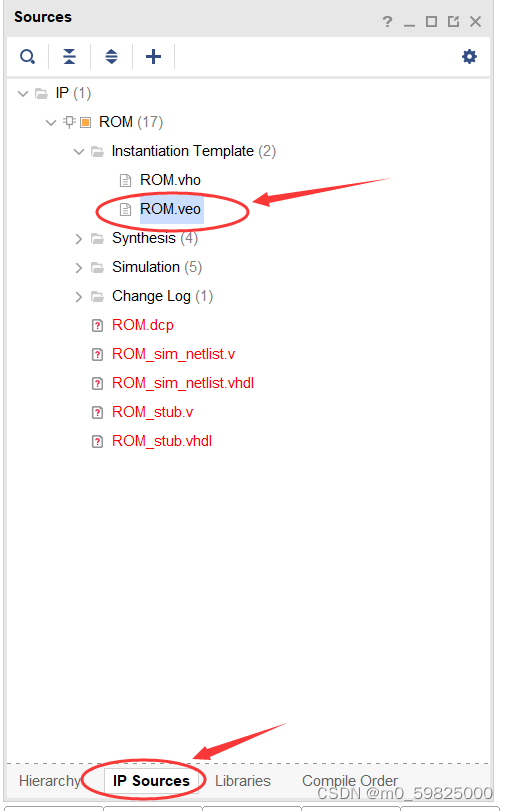

四、调用方法

点开下面的IP Sources然后查看ROM目录下的文件,从第一个文件夹中找到.veo文件并打开

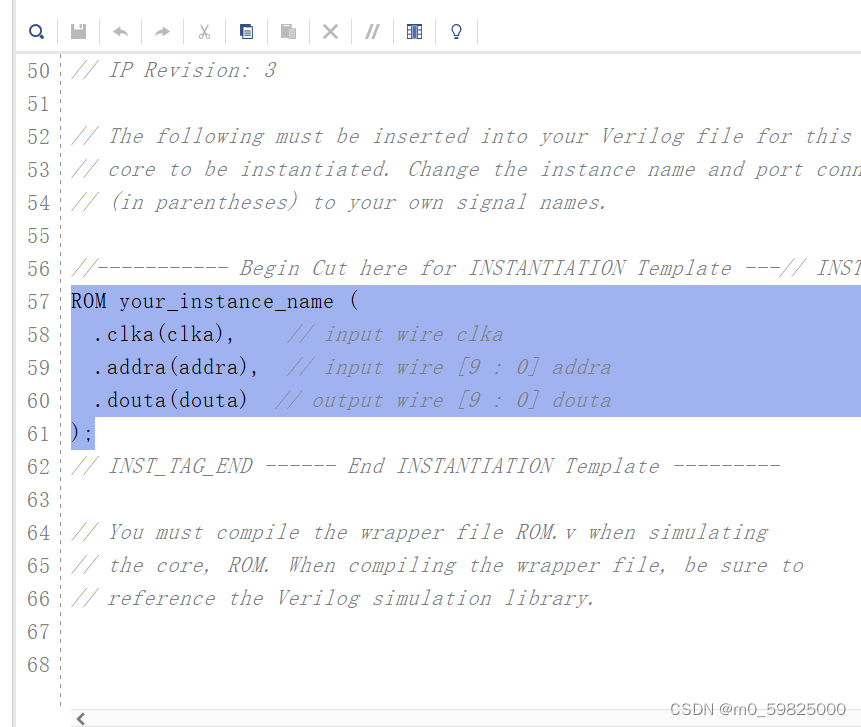

然后找到例化模块直接粘贴到要调用的层去例化,这里我直接粘贴到testbench文件中去例化

五、仿真验证

testbench代码:

`timescale 1ns / 1ps

module ROM_tb();

reg clka;

reg [9:0]addra;

wire [9:0]douta;

ROM ROM (

.clka(clka), // input wire clka

.addra(addra), // input wire [9 : 0] addra

.douta(douta) // output wire [9 : 0] douta

);

initial clka = 1;

always #10 clka = ~clka;//50Mhz时钟

initial begin

addra = 100;//初始地址为100

#500;

repeat(30000)begin//重复执行30000次

addra = addra + 1;//每执行一次地址+1

#20;

end

#2000;

$stop;

end

endmodule

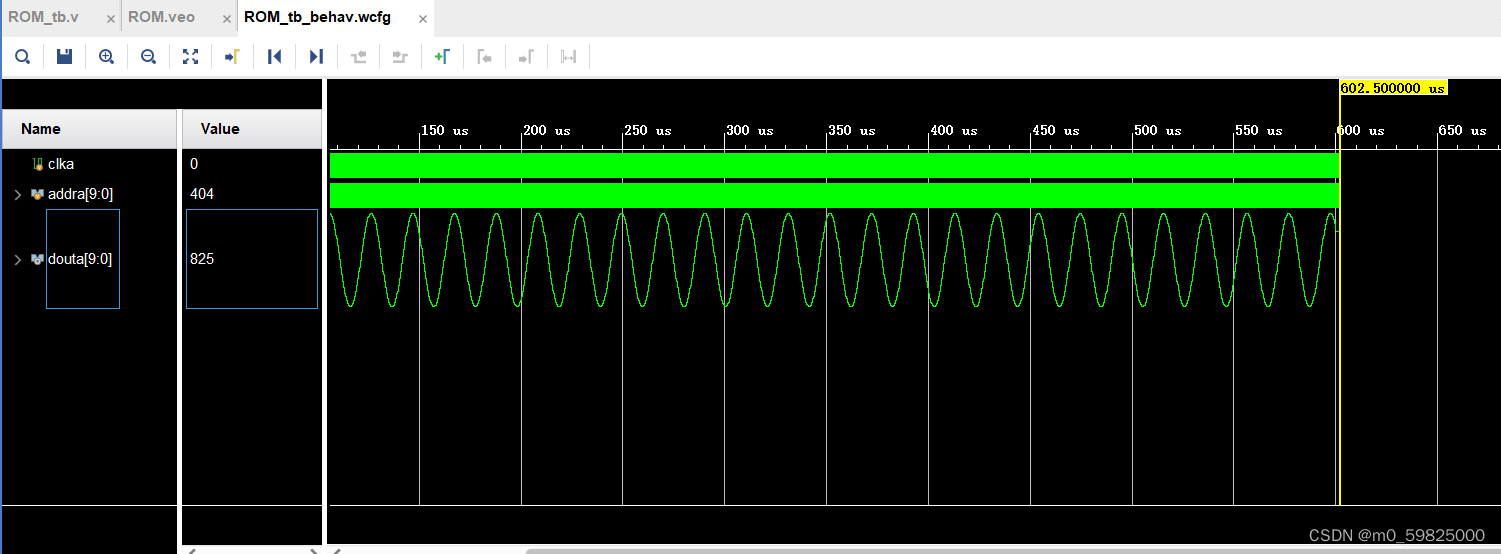

仿真结果:

这里对变量douta显示类型改为了analog型,方法为右键选择Wavefor Style然后选择analog

537

537

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?