好好告别,离开是一种新的开始,今天也是一年一度的高考,突然发现人生的转折点总在某个特别的夏天呢。那,就让我把这一年的呆在OneNote发霉的知识都慢慢整理出来晒一晒吧。偷偷的在这里,感谢我优秀的同门,让我这个喜欢纸笔的老古董也爱上了电子笔记,还有把心得记录到博客里,原来跟优秀的人在一块我也会变得更好!

Verilog基础学习笔记

前言

作为一名IC验证工程师,Verilog语言怎么能不会呢,搬来那句老套但有用的话术:不懂设计的验证不是一个好的验证师!这也是博主迈入岗位的第一课。但是学习过程中资料都比较分散,常常学完基础语法就陷入不知道要怎么实践了,本文主要根据博主的入职整个学习过程提供一些整体学习思路,从基础到后续设计等,由浅入深整合一些相关的内容,因此涉及很多细节和拓展的内容也需要自己花时间再深入学习的。

一、Verilog基础

1.学习心得

关于基础知识,CSDN中已经有比较详细的介绍博客了,我认为有一定编程基础的,不需要花太多时间,更没必要在学习视频上耗费很久时间

比如博主之前是自动化专业,接触过微机原理中的汇编语言,也接触过C语言和python等高级语言,尽管没有太多硬件基础,但是现有的编程基础还是很容易让自己理解并且有很多共通之处,所以博主认为代码还是要多上手才能学的更快。

这里贴上可以参考的博主博客链接:

Verilog学习笔记(1):Verilog基础知识

Verilog学习笔记(2):Verilog程序设计语句和描述方式

Verilog学习笔记(3):Verilog数字逻辑电路设计方法

Verilog学习笔记(4):仿真验证与Testbench编写

Verilog学习笔记(5):Verilog高级程序设计

2.笔记整理

基于我自己入职后的学习过程,在此整理一些自己的学习重点,主要提供一些思路和简单介绍,可以围绕这些重点展开进一步的学习。

1)组合逻辑和时序逻辑

- 组合逻辑电路:

只与当前输入有关,与过去输入和电路状态无关,没有内部存储器件。 - 时序逻辑电路:电路输出

不只与当前输入有关,还与过去的输入和电路状态有关,有存储元件,如触发器或者寄存器

2)两种最基本的数据类型,四种状态逻辑

- wire类型:常用的

连线型数据类型,顾名思义,我理解是模块内和模块间的数据连线。 - reg类型:

寄存器型数据类型,数据储存单元的抽象类型,对应的硬件电路元件具有状态保持作用,能够存储数据。

| 状态逻辑 | 含义 |

|---|---|

| 0 | 低电平,逻辑0或假 |

| 1 | 高电平,逻辑1或真 |

| x或者X | 不确定或者未知的逻辑状态 ,仿真过程中没有初值或者多驱会造成x态 |

| z或者Z | 高阻态 |

3)连续赋值语句

只能针对wire类型,用assign语句进行赋值。 assign语句不能出现在过程块中,过程语句包括always和initial

4)阻塞与非阻塞

只能针对reg类型,并且只能在always语句块中。

- 阻塞赋值:=

- 在串行语句中,顺序执行

- 非阻塞赋值:<=

- 在串行语句中,并行执行

5)模块的声明和调用

博主认为模块在Verilog语言中是一个基石般的存在,一般能实现一些基本功能,初学的时候我一直对标高级语言中的函数,都起到了一种封装的作用。module有两种调用方式:

- 端口位置对应方式,就是按照顺序,例如

module_name module_inst(a,b) - 端口名对应方式(.端口名(对应信号)),例如

module_name module_inst(.a(a1),.b(b1)) - 模块中带有实例参数parameter,在调用的时候是可以改变参数值的,例如

module_name #(4,3) module_inst(.a(a1),.b(b1))

6)initial块和always块

- initial块:只执行一次,不可综合,我一般常用在testbench中

- always块:只要满足敏感事件列表就可以执行,可综合,always块中敏感列表触发和电平触发不能混用

这里不得不提到博主作为一个软件思维者刚入行时很困惑的概念:什么是可综合什么是不可综合?这就是硬件和软件语言的区别了,可综合一般就是能够综合为器件,可以理解为能对应到实际的门级网表的,不可综合的一般是仿真过程需要一些语句,包括方便调试的打印语句等,这样说是不是比较能理解了。

3.拓展

还好小编喜欢拓展一下(狗头),要不然培训考试的时候就不能压中考点啦!(提供一些思路,部分涉及知识较多不做详细介绍啦,大家感兴趣可以自己查找资料学习)

1)锁存器、触发器、寄存器

贴上学习链接:

锁存器、触发器、寄存器区别

2)跨时钟域传输

话不多说直接上链接(搬运者狗头):

跨时钟域传输及解决办法

3)异步复位同步释放

这里一定要明白异步复位、同步复位、异步复位同步复位的区别以及优缺点,贴上链接:

异步复位,同步释放

4)毛刺与亚稳态

毛刺:组合逻辑毛刺消除(竞争冒险)

亚稳态:亚稳态介绍、危害及如何避免亚稳态

5)状态机

状态机是一个比较重要的内容,会画状态转换图和两段式和三段式编码是最主要的,这里就不拓展了,只介绍几种状态编码的方式:

状态编码的几种方式:

1、顺序码:000,001,010,011……

2、格雷码:000,001,011,010(异或,相同为0相异为1)

3、独热码(onehot):只有一位是1

6)常见电路设计(包括FIFO设计)

这里我推荐一个同事推荐的优秀博主总结的一些常见设计题链接,不管是备战考试还说秋招春招都好使,值得关注哟!

IC验证面试之手撕verilog常用的电路

7)RAM建模

具体建模有考到,这里不详细介绍,介绍一下三种类型:

- 1wr:单端口实现,读写不同时

- 1w1r:两端口实现,读写同时

- 2wr:双端口实现,读写同时

8)APB简单设计作业

学完基础可以了解常用的协议,基础的就是APB协议,可以进行一个简单的设计来巩固自己对于APB协议的理解和Verilog基础知识。

9)AXI设计作业

相对于APB协议,AXI协议更难,但也是很基础常用的协议,大家可以详细去学习。

二、做题笔记和心得

1.做题网站

推荐的Verilog刷题网站:

- HDLBits(入职前在家就已经做了一些题,带教老师也说这个网站每次刷都有新的体会)

- 牛客网(常见的刷题网站,校招的时候很多人都会在这上面做题)

2.做题心得

时间有点久远了,只简单记录一点吧~

1)为什么要避免锁存

首先:仅在组合逻辑中(电平触发)产生锁存。产生的情况主要有:

- 组合逻辑中的if else语句不全,没有else

- case语句分支不全而没有default

2)按位与和逻辑与

两个N bit的向量按位与会输出一个N bit位宽向量,但是逻辑与是把整个向量看作布尔值,零就是true,非零就是false,然后产生一个1bit的向量输出。

3)区分等于和全等还有===

需要注意:===一般用于可能存在x态的情况。

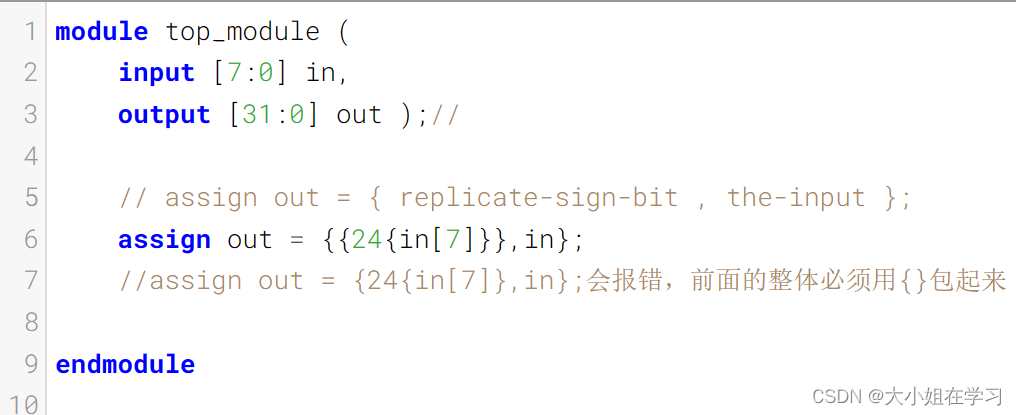

4)复制运算符{}

5)generate语句

用于多次实例化某个模块,是一个常用的语法。

Verilog中generate用法

6)其他

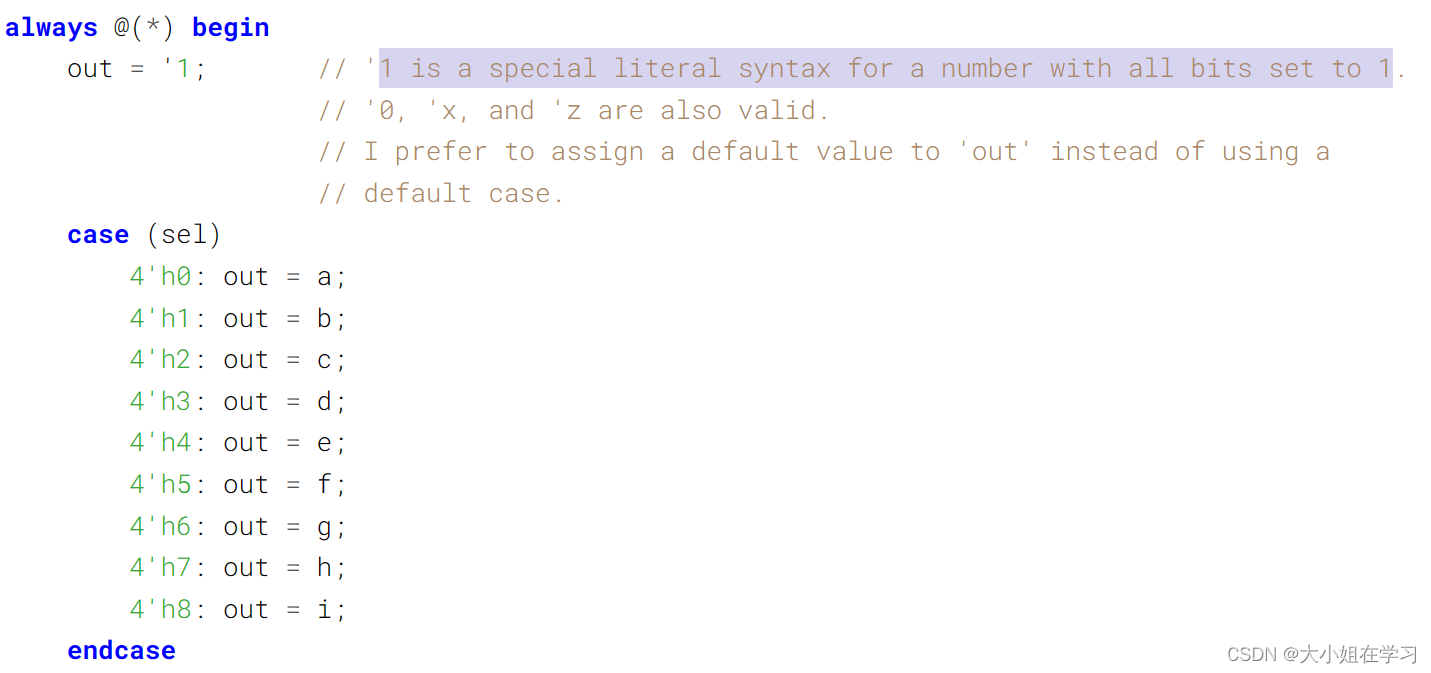

$bits()返回信号的长度,这是一个系统函数- 一个特殊的语法:

‘1,是将所有bit置1,例如:

总结

以上就是我的大致Verilog学习的思路,从基础知识到一些常见电路设计以及APB、AXI协议的拓展,提供了一定的由浅入深的学习思路供大家一起参考学习,学无止境,更详细的点还需要自己多多搜集和动手学习,一起加油!

1656

1656

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?