此文只用来记录在刷题时的一些需要注意的知识点

VL1 四选一多路选择器

制作一个四选一的多路选择器,要求输出定义上为线网类型。

1、线网类型 :wire 应用assign关键词。

2、四选一多路选择器:使用case语句:判断条件为SEl输入端

VL2 异步复位的串联T触发器

用verilog实现两个串联的异步复位的T触发器的逻辑

先了解T触发器:T触发器是一种边沿敏感的存储单元。只有一个信号输入端T,在时钟有效边沿到来时,T端输入有效信号,则触发器翻转,否则触发器保持不变。T触发器逻辑功能为:当T=0时,触发器状态不变Qn+1=Qn;而当T=1时,在脉冲有效边沿到来时翻转。

1、在每个时钟周期的时钟有效沿判断 当前T触发器的输入是否有效;有效状态翻转;无效保持。

VL3 奇偶校验

现在需要对输入的32位数据进行奇偶校验,根据sel输出校验结果(1输出奇校验,0输出偶校验)。

奇校验:原始码流+校验位 总共有奇数个1;偶校验:原始码流+校验位 总共有偶数个1

按位异或得到奇校验,去奇校验取反得到偶校验结果。

assign odd=^bus;

assign check=sel? odd:~odd;

VL4 移位运算与乘法

已知d为一个8位数,请在每个时钟周期分别输出该数乘1/3/7/8,并输出一个信号通知此时刻输入的d有效(d给出的信号的上升沿表示写入有效)。

1、首先在每个时钟有效沿进行计数,当输入数据开始计数,在计数为0、1、2、3时分别输出1/3/7/8,可以使用case语句,判断条件为当前计数器数值,同时在计数器为0 的时候输出input_grant。

2、分别输出该数乘1/3/7/8:左移一位*2,1/3/7/8分别为 :左移一位减去自身 ;左移二位减去自身 ;左移四位减去自身 ;左移四位 ;分别在计数器的不同时刻输出

cnt<=cnt+1’b1;

case(cnt)

0:begin

din<=d;

input_grant<=1;

out<=d;

end

1:begin

input_grant<=0;

out<=(din<<2)-din;

end

2:begin

input_grant<=0;

out<=(din<<3)-din;

end

3:begin

input_grant<=0;

out<=(din<<3);

end

endcase

VL5 位拆分与运算

现在输入了一个压缩的16位数据,其实际上包含了四个数据[3:0][7:4][11:8][15:12],

现在请按照sel选择输出四个数据的相加结果,并输出valid_out信号(在不输出时候拉低)

0: 不输出且只有此时的输入有效

1:输出[3:0]+[7:4]

2:输出[3:0]+[11:8]

3:输出[3:0]+[15:12]

1、case语句,根据SEl信号的不同 进行不同位置的拆分

VL6 多功能数据处理器

根据指示信号select的不同,对输入信号a,b实现不同的运算。输入信号a,b为8bit有符号数,当select信号为0,输出a;当select信号为1,输出b;当select信号为2,输出a+b;当select信号为3,输出a-b

1、case语句 根据SEL的不同值 操作。

VL7 求两个数的差值

根据输入信号a,b的大小关系,求解两个数的差值:输入信号a,b为8bit位宽的无符号数。如果a>b,则输出a-b,如果a≤b,则输出b-a

1、判断大小输出

VL8 使用generate…for语句简化代码

在某个module中包含了很多相似的连续赋值语句,请使用generata…for语句编写代码,替代该语句,要求不能改变原module的功能。

使用Verilog HDL实现以上功能并编写testbench验证。

module template_module(

input [7:0] data_in,

output [7:0] data_out

);

assign data_out [0] = data_in [7];

assign data_out [1] = data_in [6];

assign data_out [2] = data_in [5];

assign data_out [3] = data_in [4];

assign data_out [4] = data_in [3];

assign data_out [5] = data_in [2];

assign data_out [6] = data_in [1];

assign data_out [7] = data_in [0];

endmodule

1、generate…for 语句 循环变量必须由特定关键字genvar声明。

genvar i; //声明循环变量为非负整数

generate

for(i = 0; i < 8; i = i + 1) //循环条件

begin : bit_reverse //begin…end块中为待生成的代码原型

assign data_out[i] = data_in[7 - i];

end

endgenerate

其中 bit_reversr 便是 generate…for语句块的名称,可根据需要修改。

VL9 使用子模块实现三输入数的大小比较

请编写一个子模块,将输入两个8bit位宽的变量data_a,data_b,并输出data_a,data_b之中较小的数。并在主模块中例化,实现输出三个8bit输入信号的最小值的功能。

1、模块例化格式

sub_mod mod1(

.clk(clk),

.rst_n(rst_n),

.data_a(a),

.data_b(b),

.c(m)

);

clk、rst_n、data_a、data_b、c为模块的信号端口名。

clk、rst_n、a、b、c例化后模块,可理解为接线。

VL10 使用函数实现数据大小端转换

在数字芯片设计中,经常把实现特定功能的模块编写成函数,在需要的时候再在主模块中调用,以提高代码的复用性和提高设计的层次,分别后续的修改。

请用函数实现一个4bit数据大小端转换的功能。实现对两个不同的输入分别转换并输出。

函数的声明模板:

function [range-1:0] function_name ;

input_declaration ;

other_declaration ;

procedural_statement ;

endfunction

例如本题 function [3:0] data_rev;

input [3:0] data_in;

begin

data_rev[0] = data_in[3];

data_rev[1] = data_in[2];

data_rev[2] = data_in[1];

data_rev[3] = data_in[0];

end

endfunction

VL13 优先编码器电路①

casex语句:其中对X,Z是不关心状态、

casez语句:对z是不关心状态。

VL14 用优先编码器①实现键盘编码电路

请使用优先编码器①实现键盘编码电路,可添加并例化题目中已给出的优先编码器代码。

10个按键分别对应十进制数0-9,按键9的优先级别最高;按键悬空时,按键输出高电平,按键按下时,按键输出低电平;键盘编码电路的输出是8421BCD码。

1、模块的例化和调用

VL15 优先编码器Ⅰ

下表是8线-3线优先编码器Ⅰ的功能表。

①请根据该功能表,用Verilog实现该优先编码器Ⅰ。

1、输出为线网型。应该用assign语句

2、根据逻辑功能表,列写表达式

VL16 使用8线-3线优先编码器Ⅰ实现16线-4线优先编码器

请使用2片该优先编码器Ⅰ及必要的逻辑电路实现16线-4线优先编码器。优先编码器Ⅰ的真值表和代码已给出。

可将优先编码器Ⅰ的代码添加到本题答案中,并例化。

1、对8线-3线优先编码器Ⅰ进行调用例化。

VL17 用3-8译码器实现全减器

请使用3-8译码器和必要的逻辑门实现全减器,全减器接口图如下,A是被减数,B是减数,Ci是来自低位的借位,D是差,Co是向高位的借位

1、3-8译码器包含了A2、A1、A0、的所有最小项,因为全减器的所有最小项也包含其中,因此可用3-8译码器来实现全减器,将符合条件的最小项 或 起来输出。

VL18 实现3-8译码器①

可以用赋值语句,根据逻辑功能表用基本逻辑门来实现

也可以用 case…endcase语句来实现

VL19 使用3-8译码器①实现逻辑函数

请使用3-8译码器①和必要的逻辑门实现函数L=(~A)·C+A·B

1、首先将函数L=(~A)·C+A·B 转换成为最小项的形式。

2、例化3-8译码器,根据最小项表达式,将符合条件的输出

VL20 数据选择器实现逻辑电路

请使用此4选1数据选择器和必要的逻辑门实现下列表达式。

L=A∙B+A∙~C+B∙C

1、根据逻辑表达式,列写真值表,将AB接入选择端,将变量C分配在数据输入端,根据输出L与C的关系分配数值

VL21 根据状态转移表实现时序电路

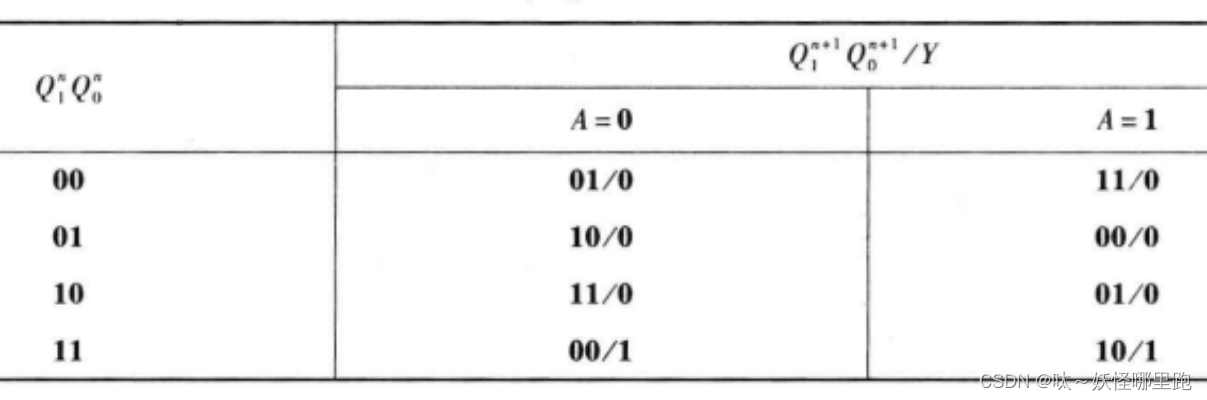

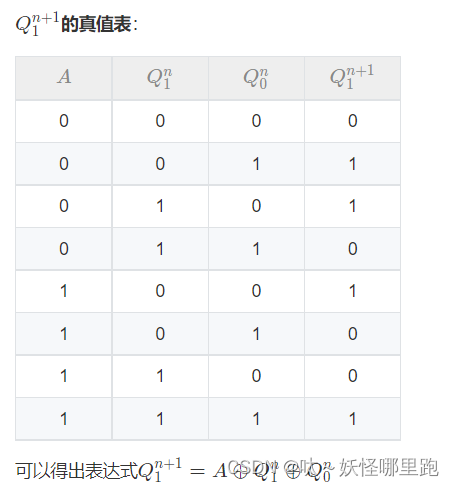

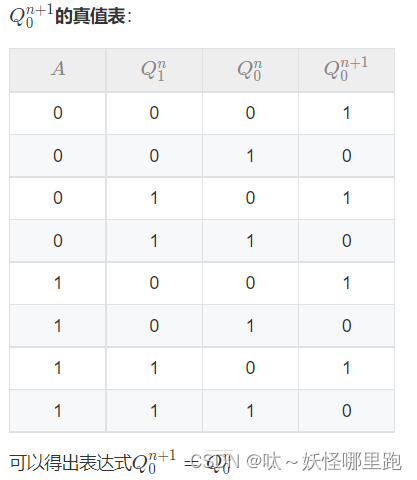

某同步时序电路转换表如下,请使用D触发器和必要的逻辑门实现此同步时序电路,用Verilog语言描述。

1、可将电路转换表分开来看,分成三部分

2、根据表达式在每个时钟的有效沿进行判断输出

1209

1209

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?