【FPGA】IP的封装及调用(Vivado)

一、Vivado中IP的概念

Vivado中的IP核:

Vivado中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。

二、Vivado中IP的封装

1、编写需要封装成IP的程序

首先先编写一个简单的程序并对该程序进行IP的封装,这里编写的是简单的按键消抖模块进行封装。

代码实例:

`timescale 1ns / 1ps

module Key(

input clk ,

input rst_n ,

input key ,

output flag

);

parameter DELAY = 5_000;

reg [31:0] cnt;

//---------------COUNT----------------------//

always@(posedge clk)

if(rst_n)

cnt <= 0;

else if(key == 0)

begin

if(cnt == DELAY - 1)

cnt <= cnt;

else

cnt <= cnt + 1;

end

else

cnt <= 0;

//---------------------flag------------------------//

assign flag = (cnt == DELAY - 2) ? 1 : 0;

endmodule

2、开始封装

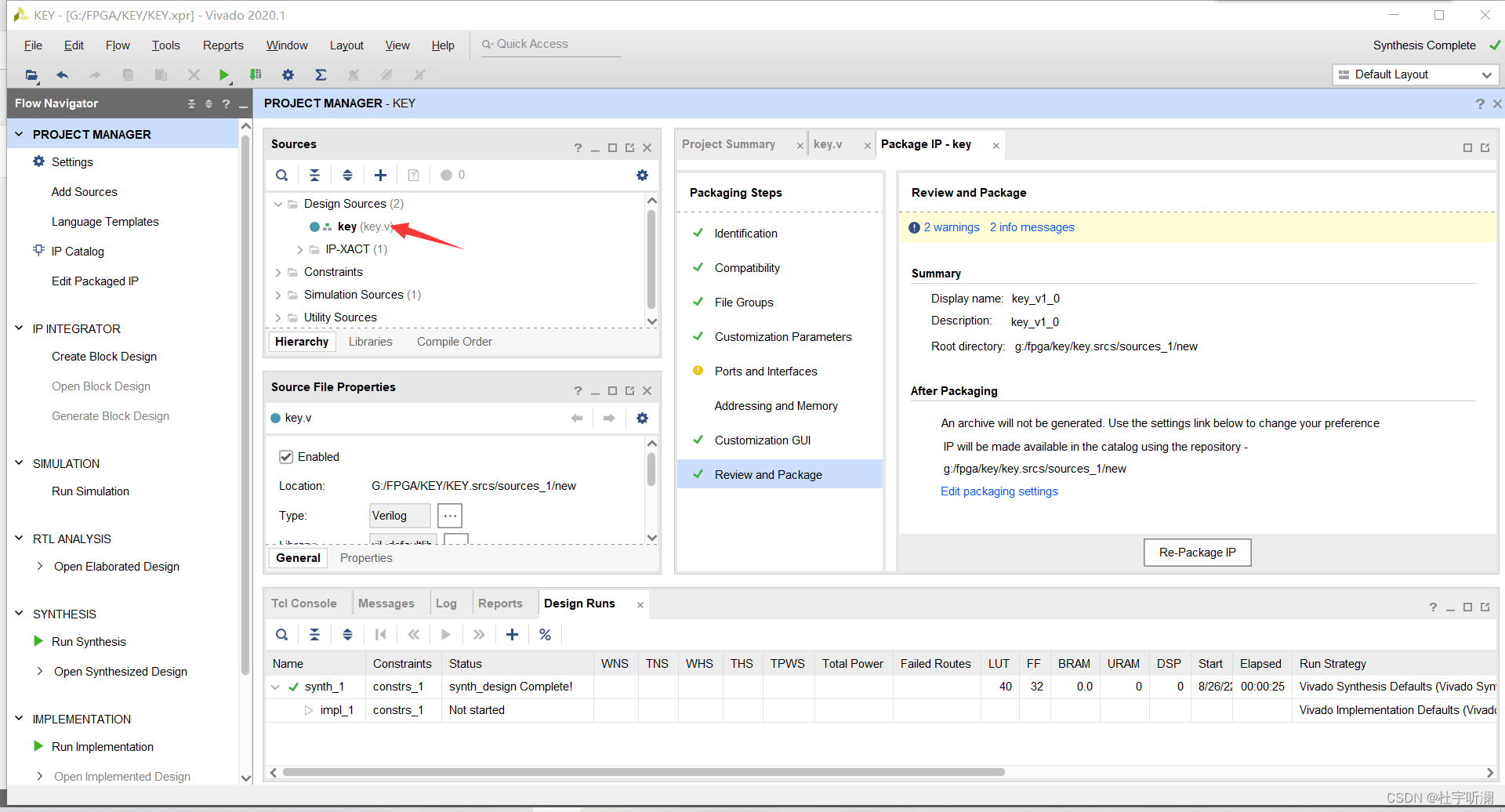

(1)将想要进行封装的模块设置为头部文件

将key模块设置为头部文件

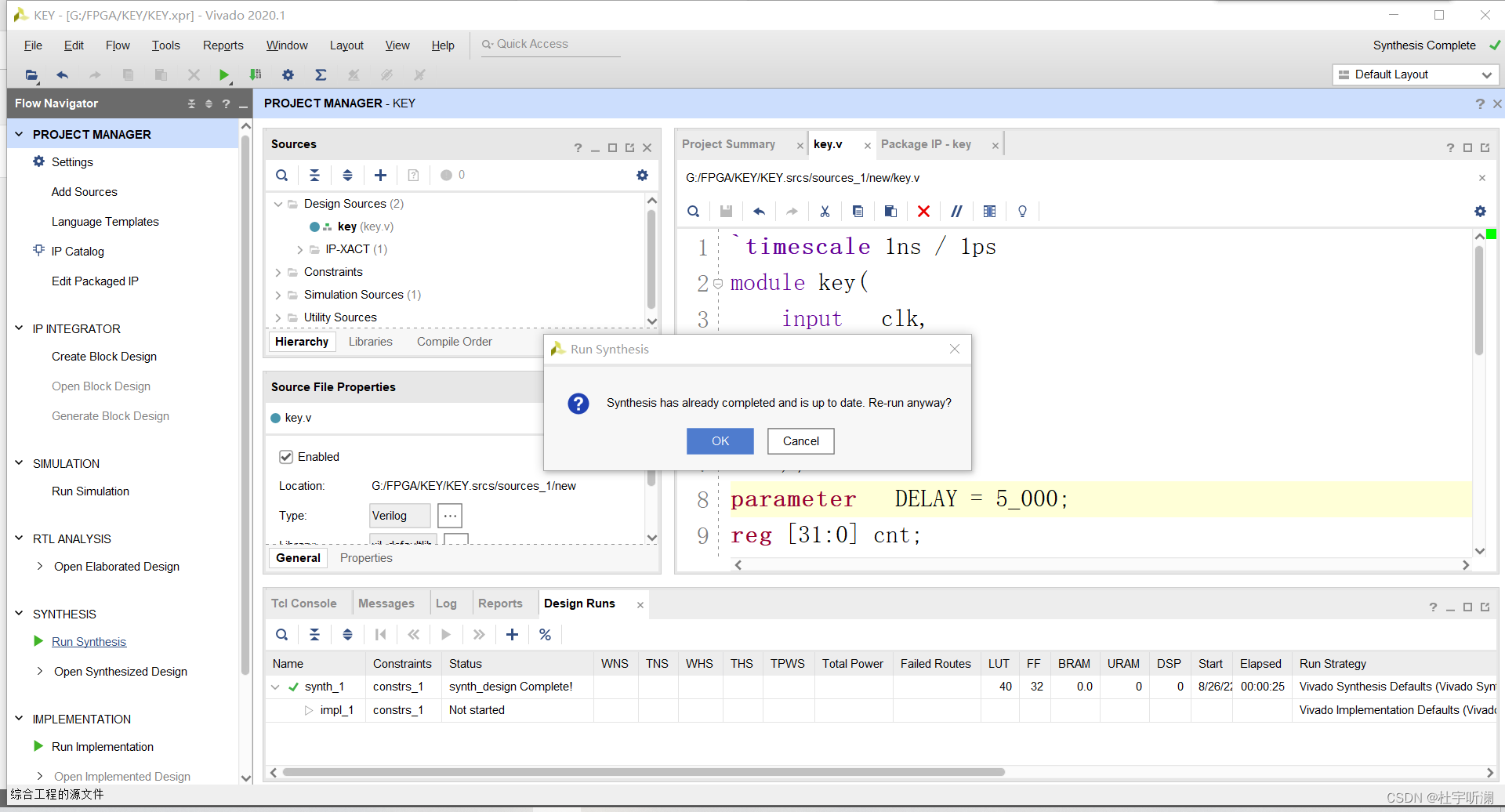

(2)进行综合

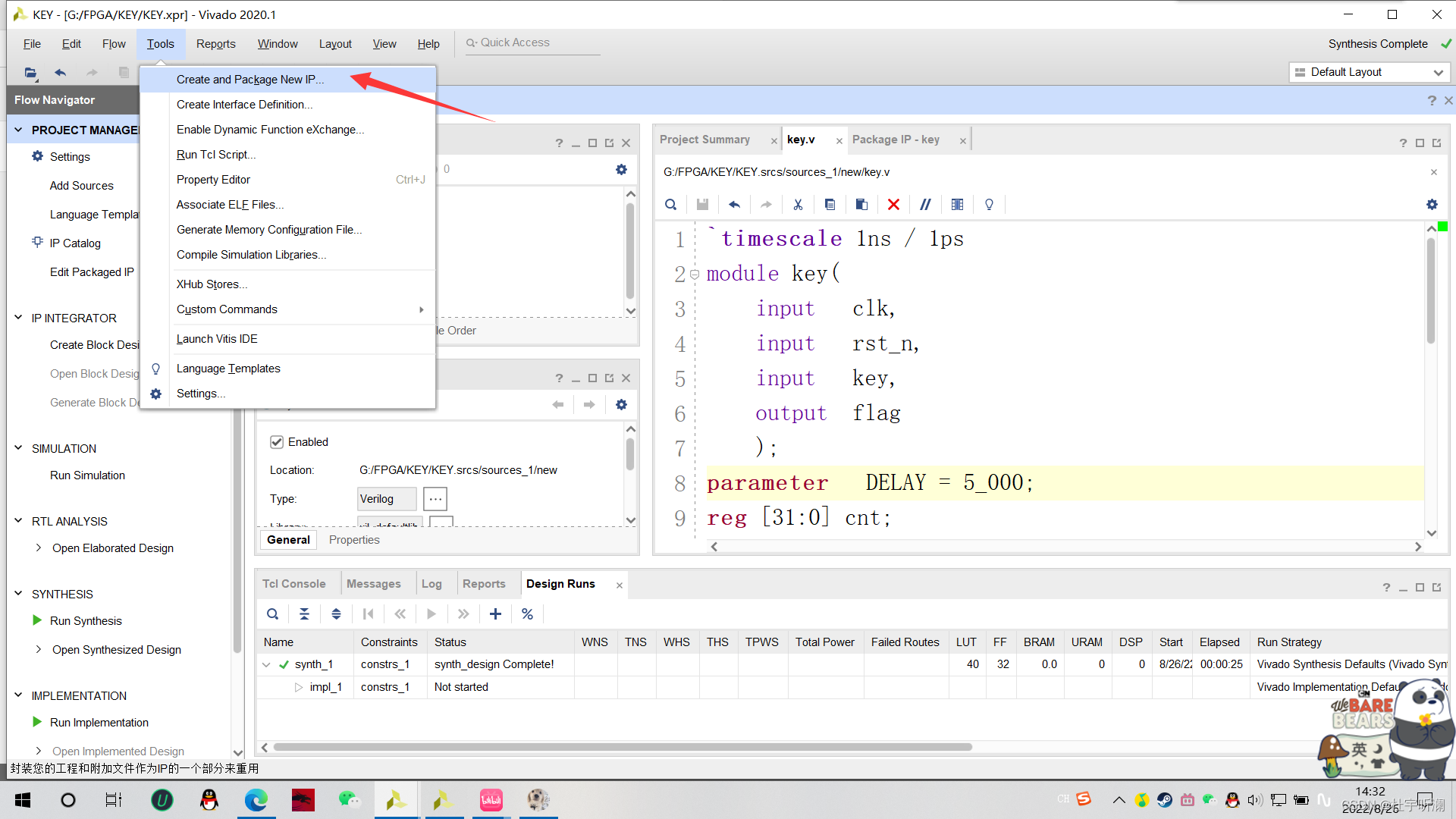

(3)点击创建IP

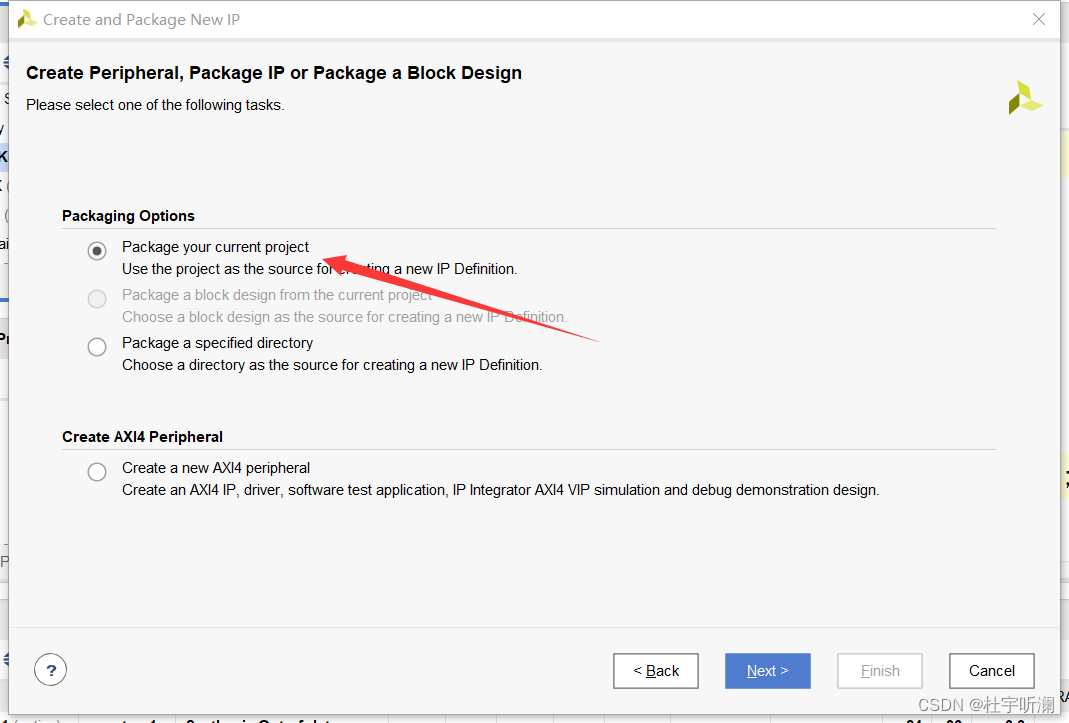

(4)创建IP

这里选择第一项

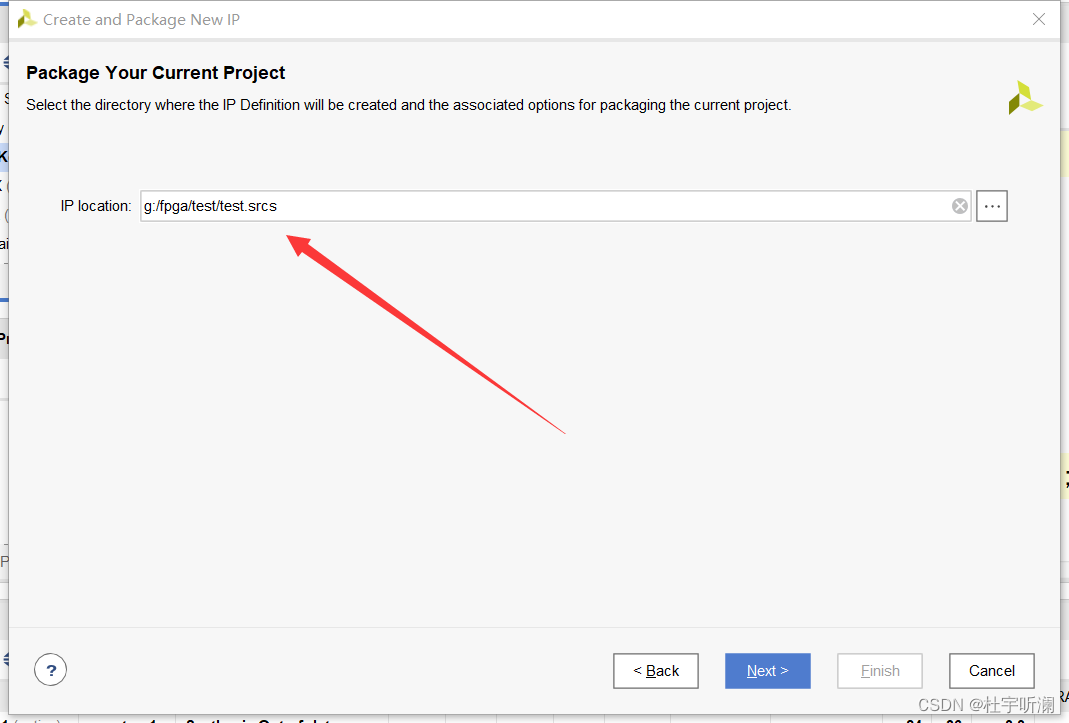

(5)选择存放路径

这里选择默认路径

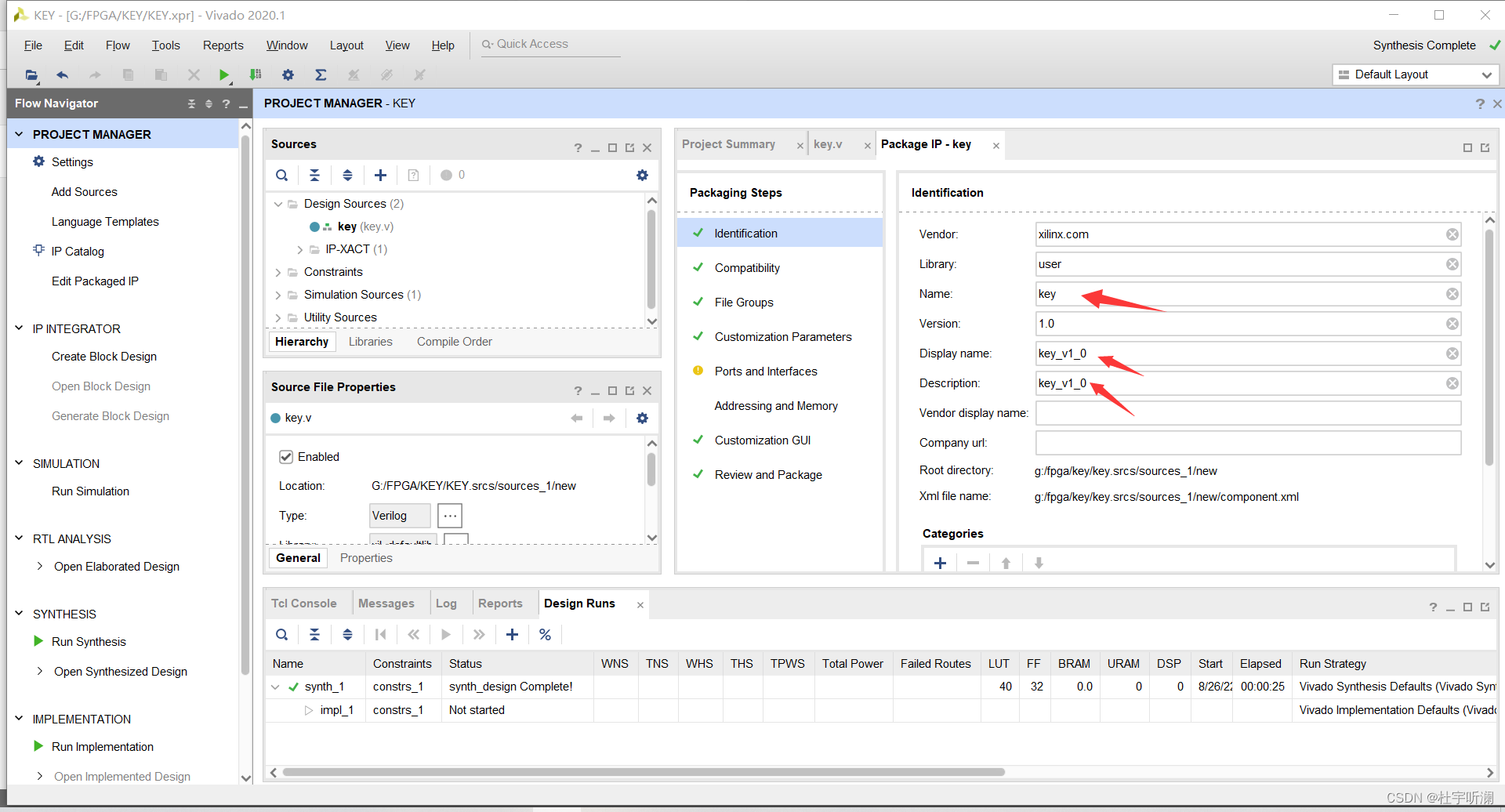

(6)更改IP名称

对IP进行重命名方便下一次对IP进行查询并调用

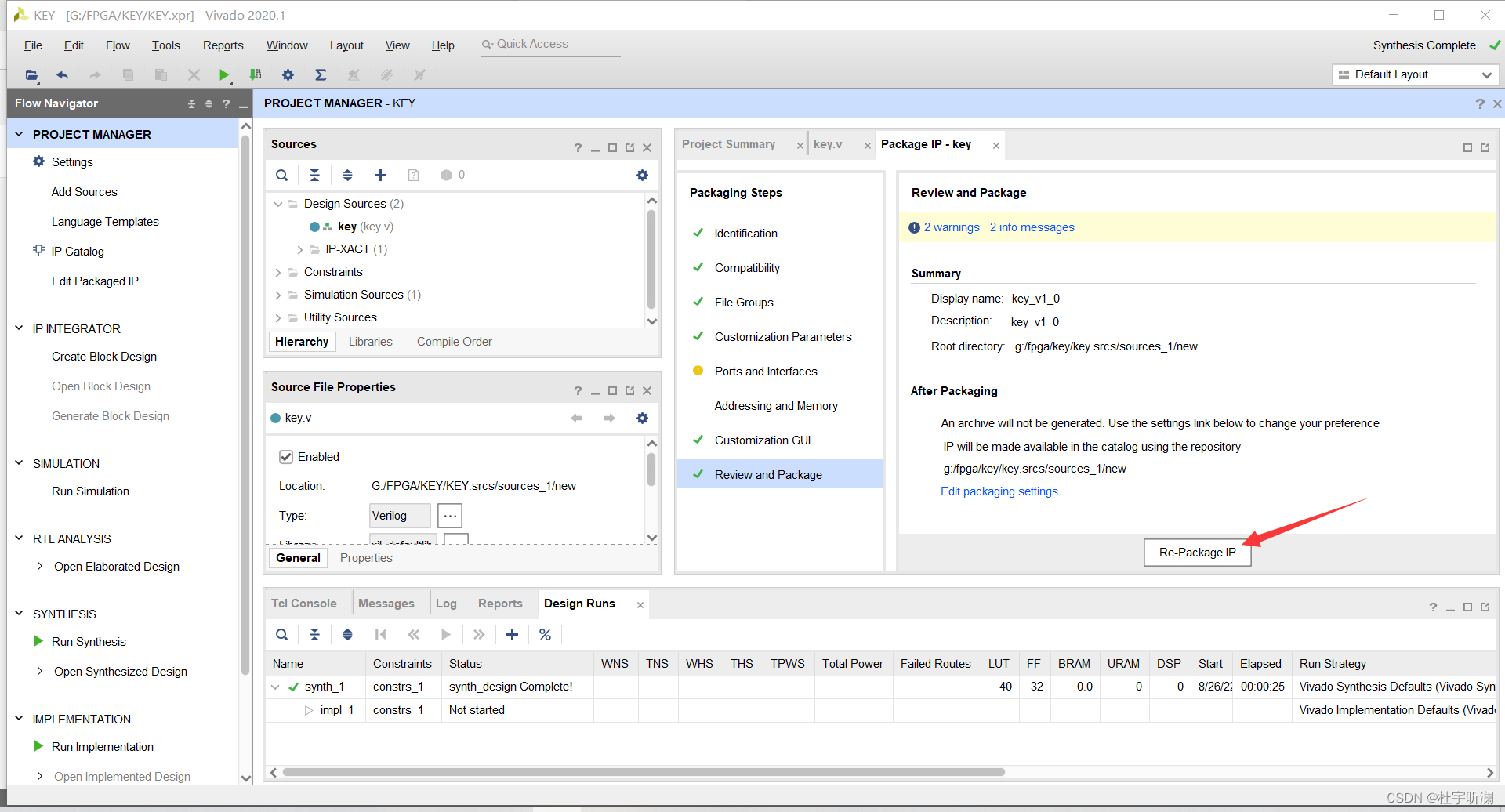

(7)生成IP

如图所示:

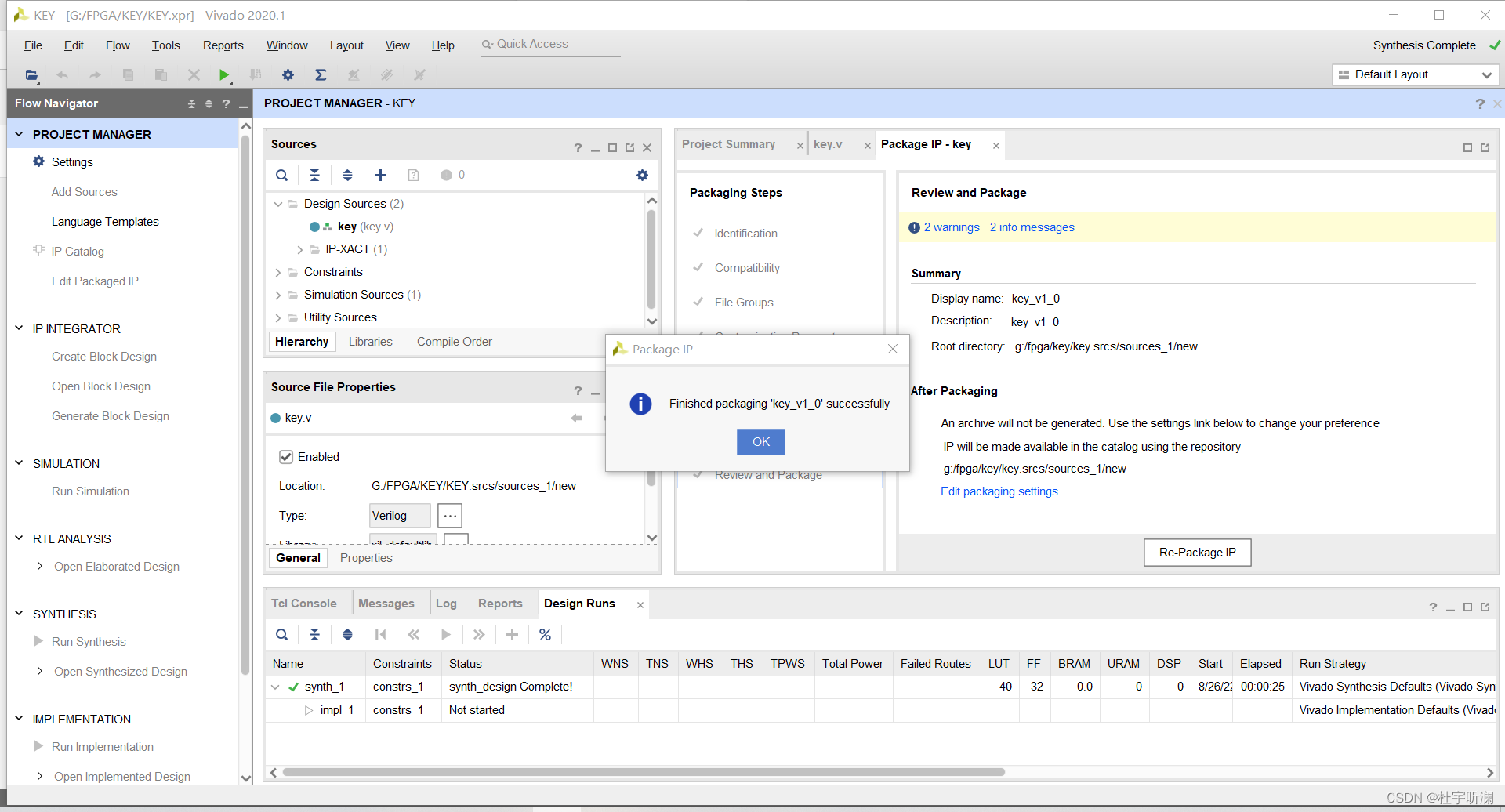

若出现下图中文本框则生成成功

三、Vivado中IP的调用

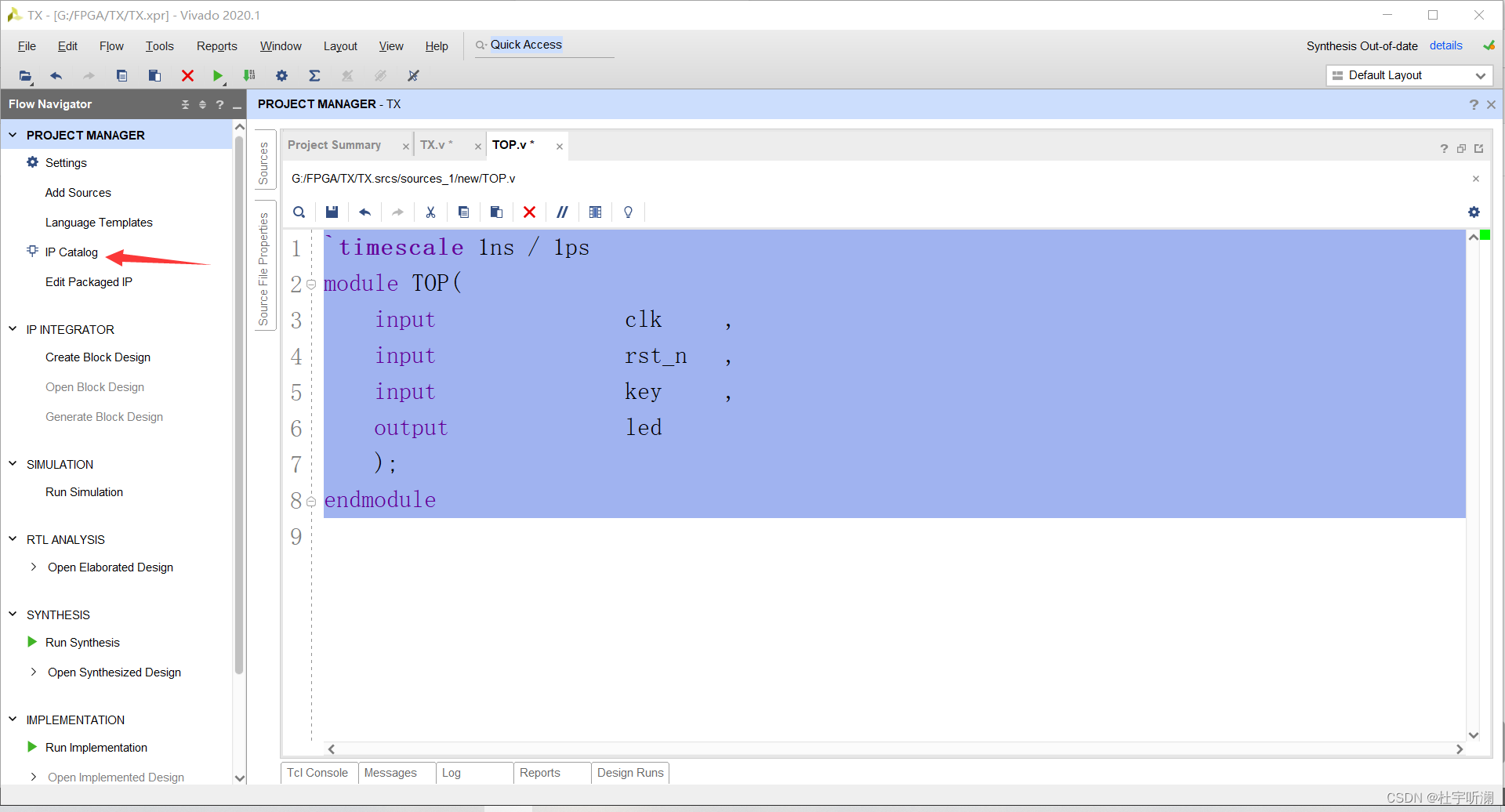

1.新建项目创建TOP模块

新建项目并创建TOP模块

代码如下:

`timescale 1ns / 1ps

module TOP(

input clk ,

input rst_n ,

input key ,

output led

);

endmodule

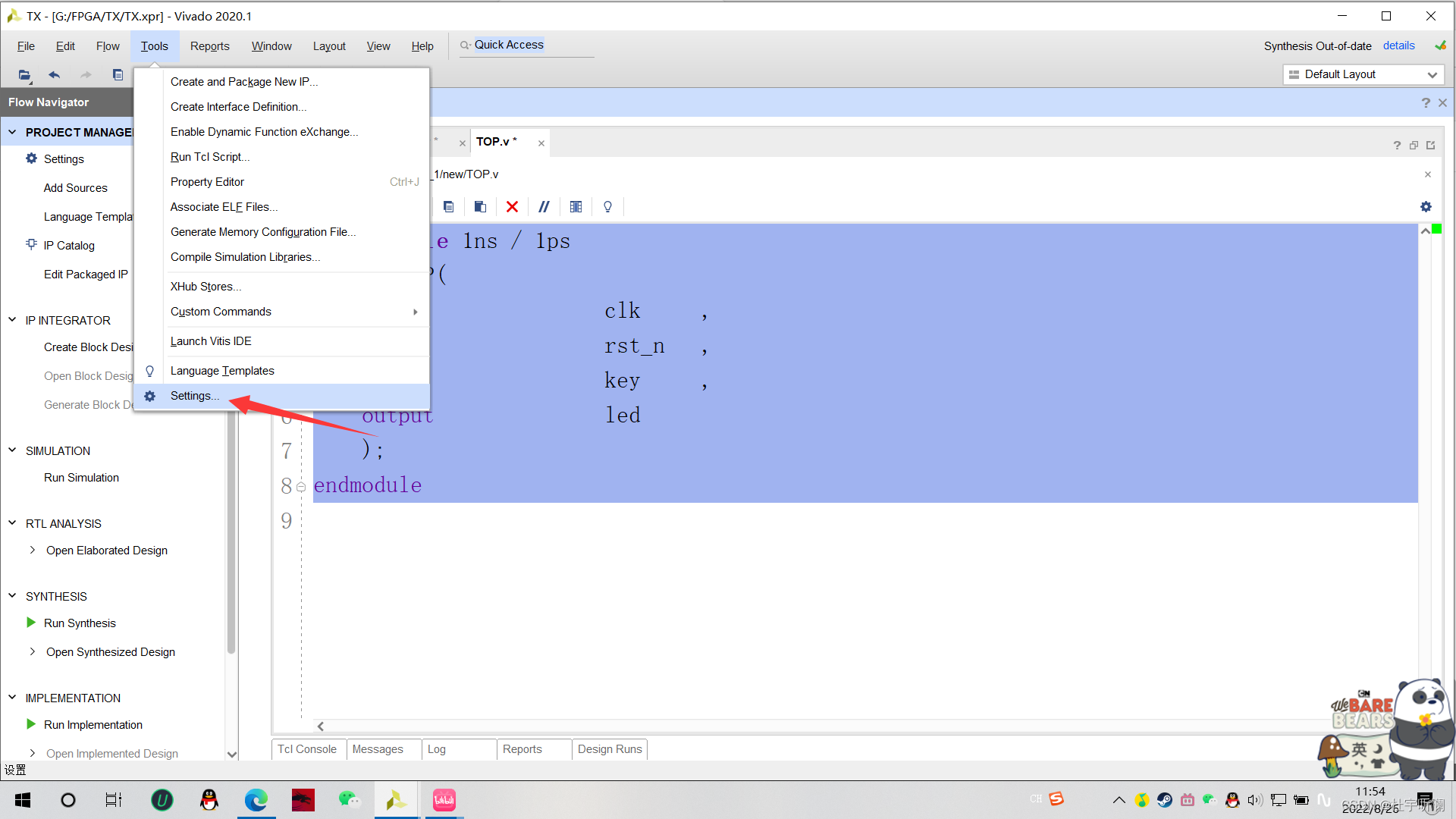

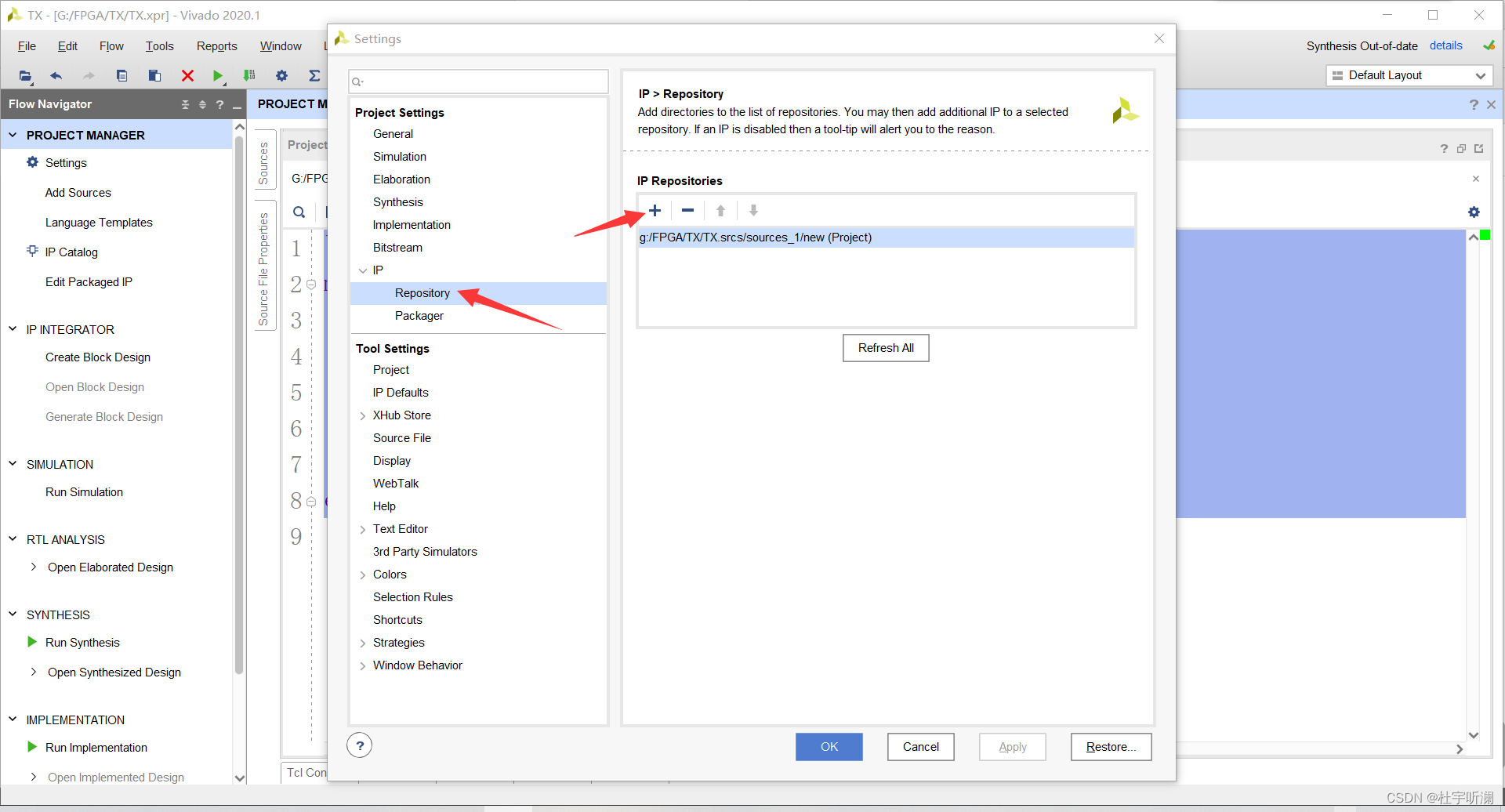

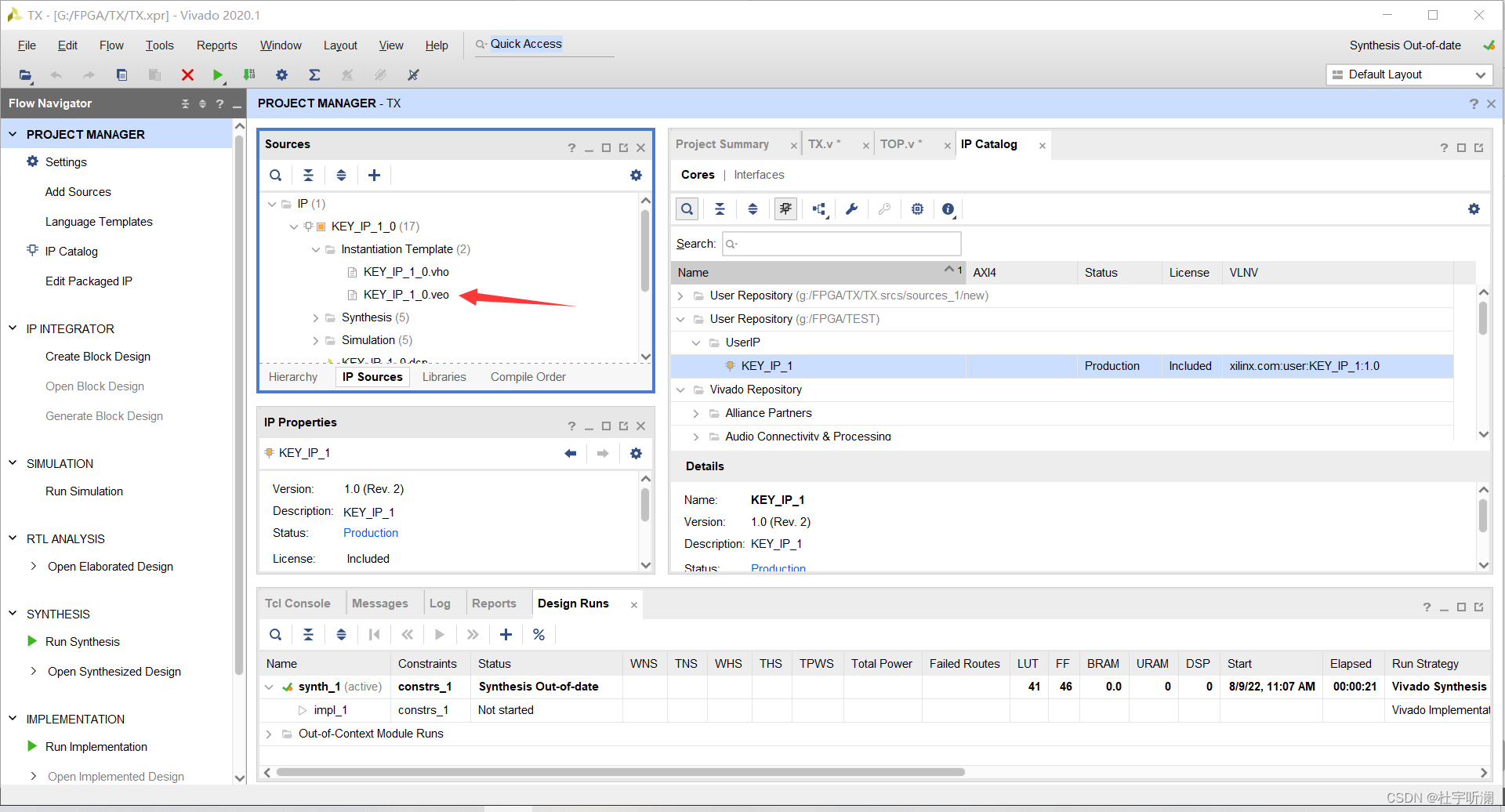

2、查找已封装IP

点击如图所示的加号进行IP的添加(手动寻找需要调用的IP的位置)。

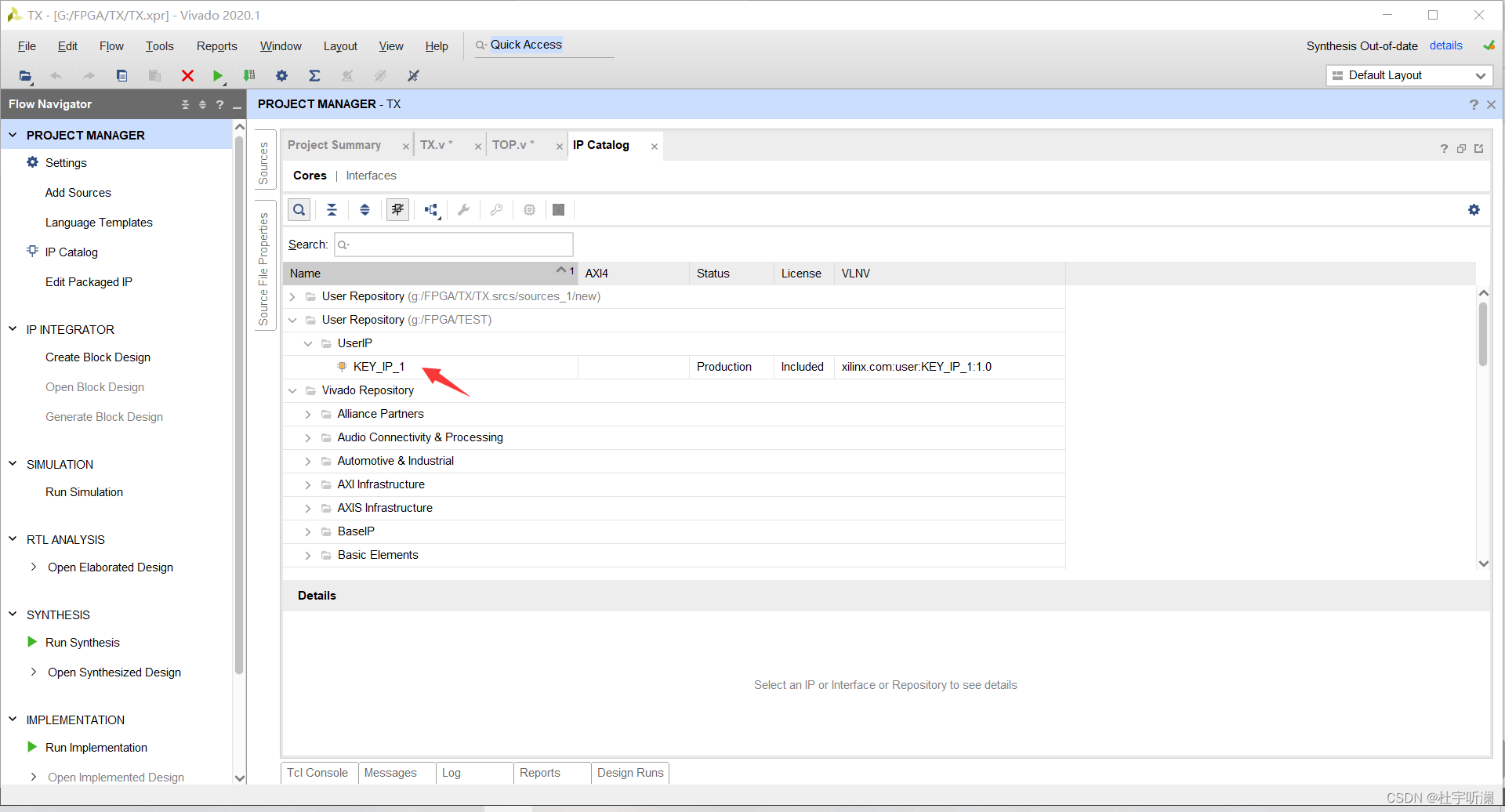

如图所示为查找到IP的结果。

3、IP配置

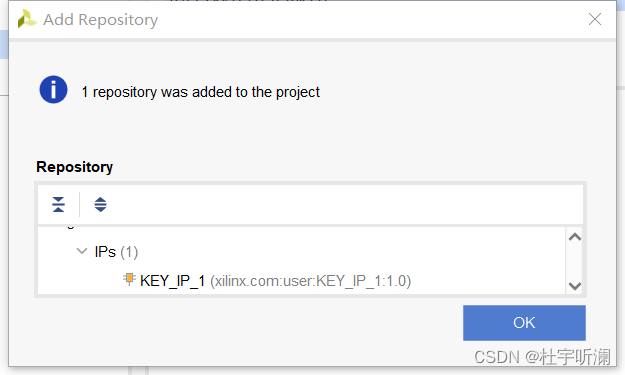

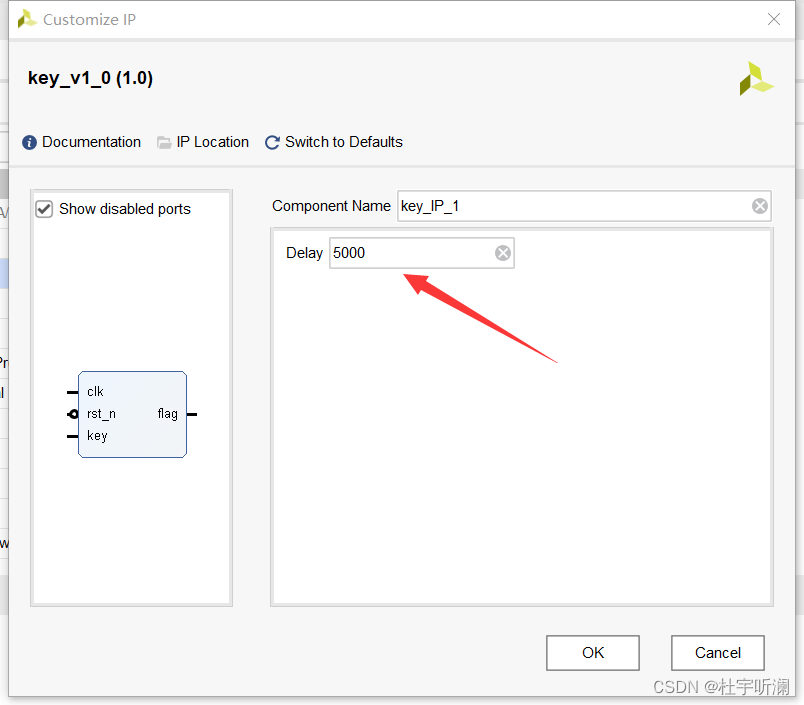

- 在左侧工具栏找到IP Catalog并进行IP的配置与生成。

如图所示可以在箭头指向的位置进行参数修改

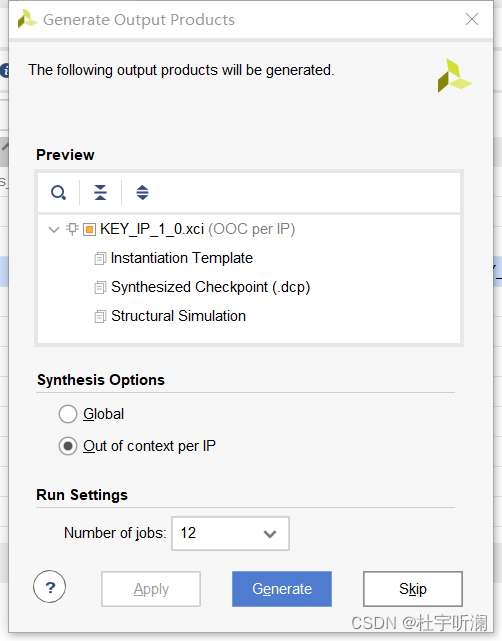

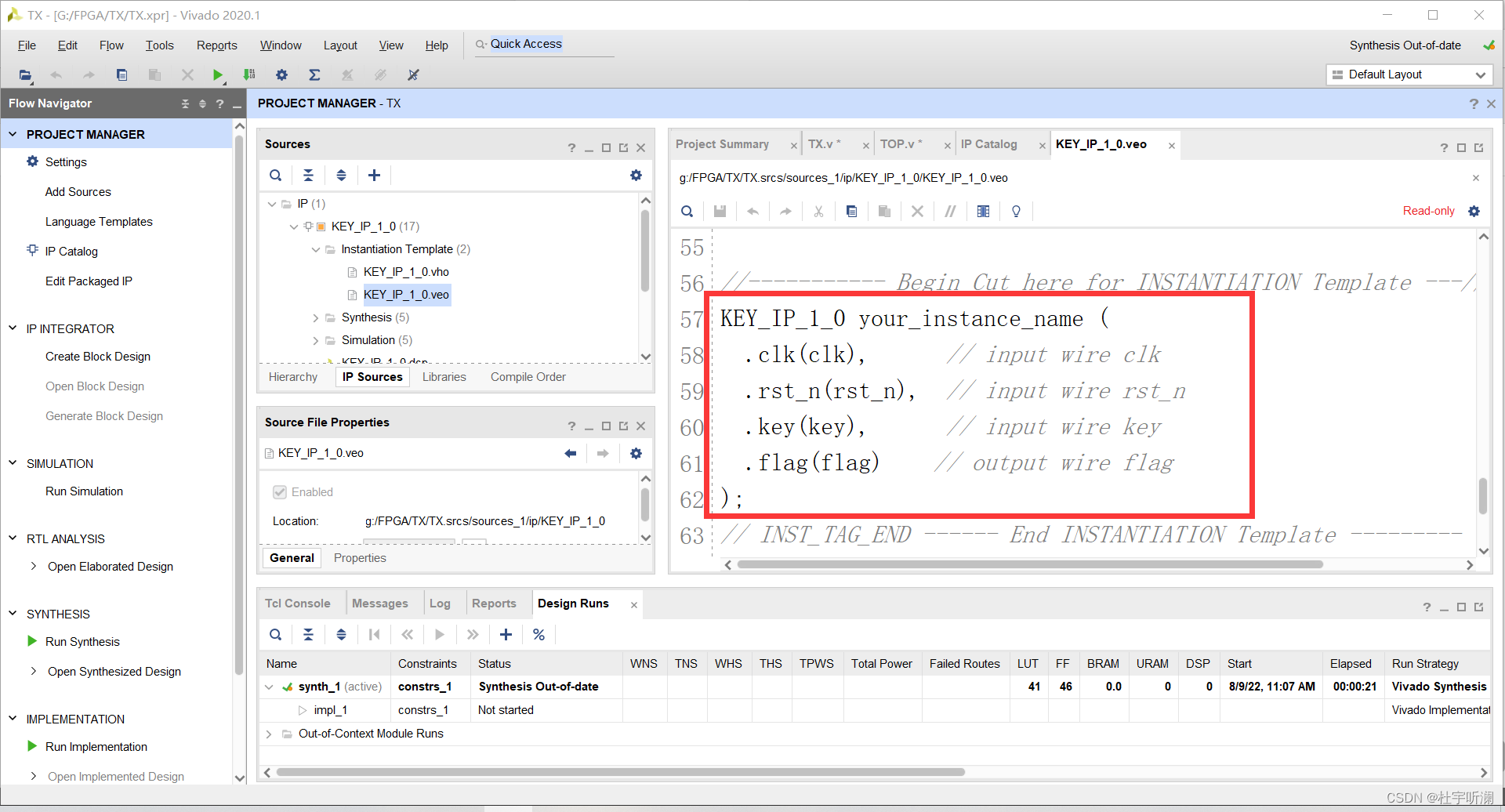

4、调用IP

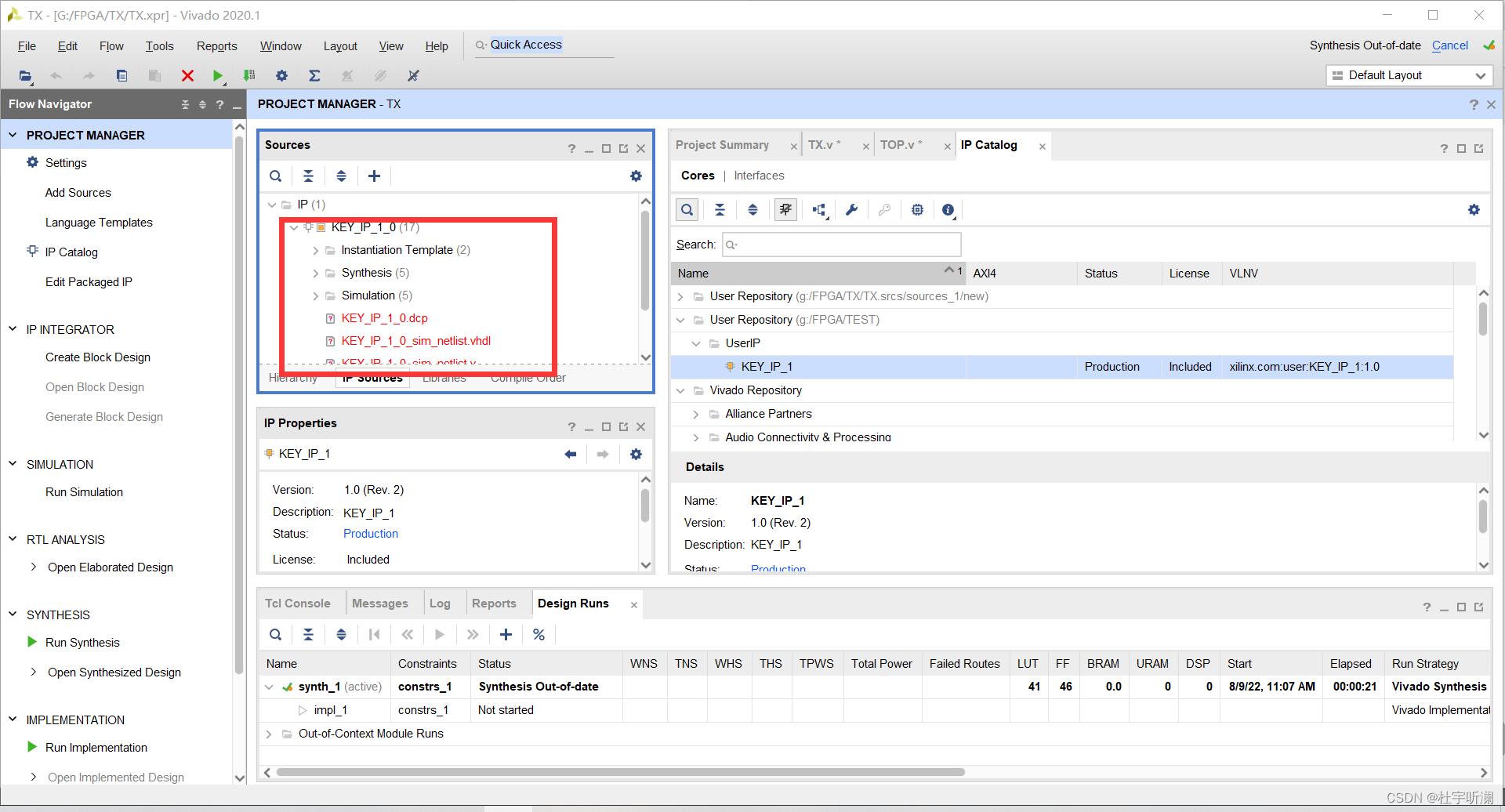

- 生成IP完成后可以在如图所示位置看到所有IP

- 双击打开该文件,则出现下图所示内容:

将该部分复制粘贴到TOP模块中进行例化

5、调用结果

IP调用结果如下:

当按键按下时若上一个状态的led为点亮状态则led熄灭,若上一个状态的led为熄灭状态则led点亮。

代码示例:

`timescale 1ns / 1ps

module TOP(

input clk ,

input rst_n ,

input key ,

output led

);

wire flag ;

KEY_IP_1_0 u1(

.clk (clk ), // input wire clk

.rst_n (rst_n ), // input wire rst_n

.key (key ), // input wire key

.flag (flag ) // output wire flag

);

always@(posedge clk)

if(!rst_n)

led <= 0;

else if(flag == 1)

led <= ~led;

else

led <= led;

endmodule

四、结果

1、编写仿真文件

代入实例:

`timescale 1ns / 1ps

module TEST();

reg clk;

reg rst_n;

reg key;

TOP u2(

.clk (clk ),

.rst_n (rst_n),

.key (key ),

.led (led )

);

initial

begin

clk = 1;

rst_n = 0;

#10 rst_n = 1;

key =1;

#200 key = 0;

end

always #10 clk = ~clk;

endmodule

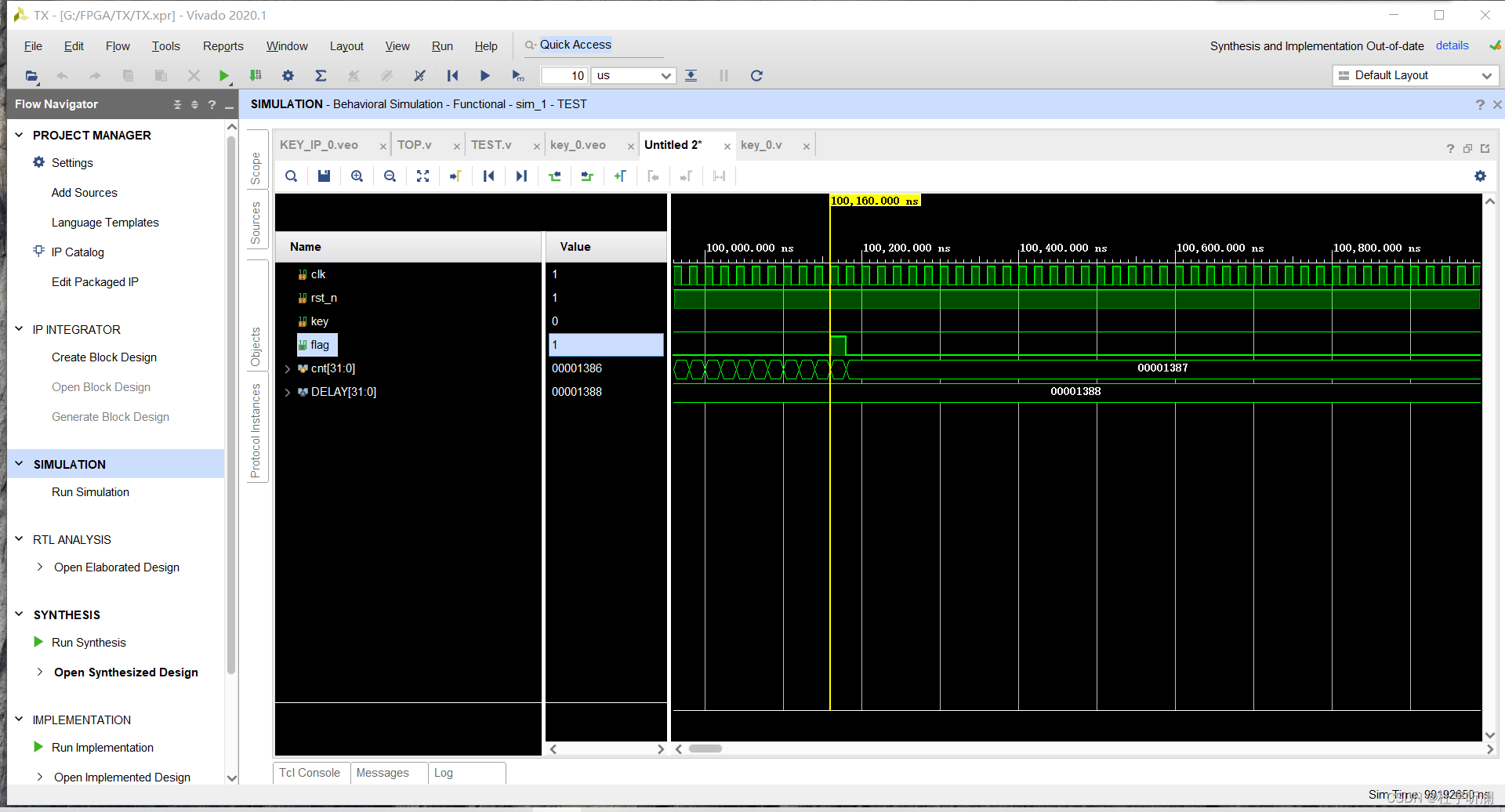

2、查看仿真结果

仿真截图如图:

当按键按下时flag为1同时cnt不再计数,仿真结果与理论相同,IP调用成功。

本文介绍Vivado中IP核的概念及其封装过程,包括编写程序、综合、创建及调用IP,并通过按键消抖模块的具体实例,展示了如何在TOP模块中调用所封装的IP。

本文介绍Vivado中IP核的概念及其封装过程,包括编写程序、综合、创建及调用IP,并通过按键消抖模块的具体实例,展示了如何在TOP模块中调用所封装的IP。

1943

1943

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?