半加器

任务描述

本关任务:利用在Logisim中的“组合逻辑分析”工具自动生成半加器电路。

相关知识

实验截图:

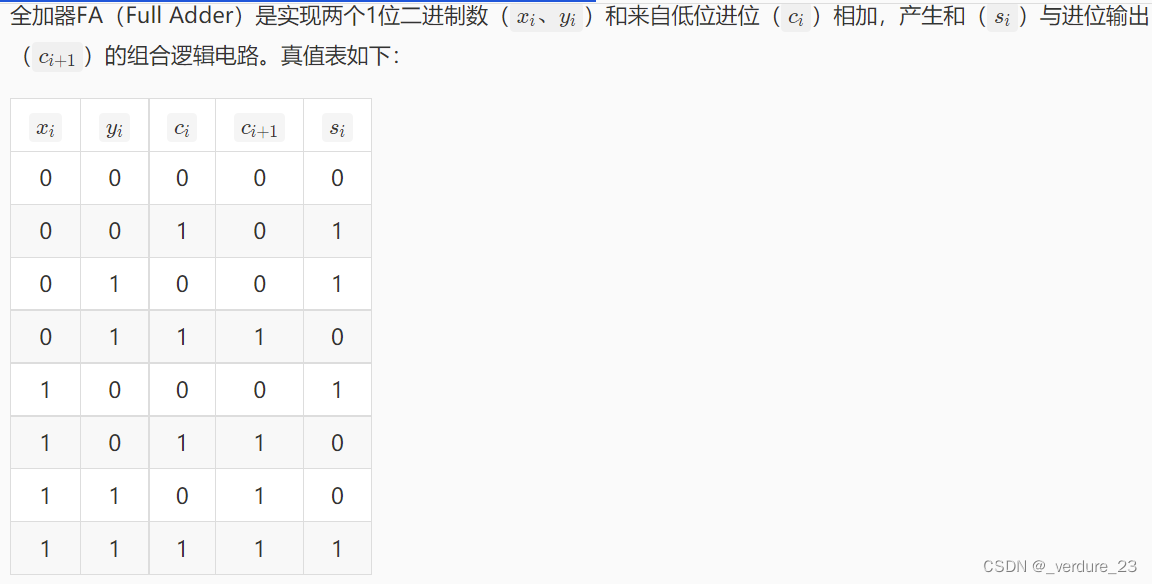

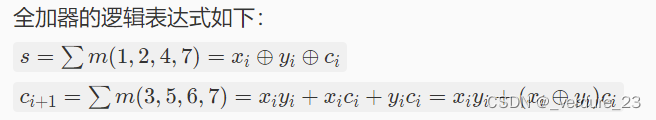

全加器设计

任务描述

本关任务:请根据教材中的全加器原理图在Logisim中手工绘制全加器电路。

相关知识

实验截图:

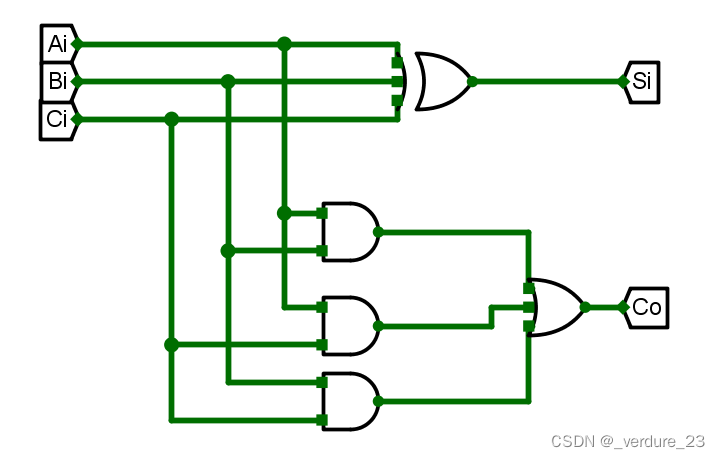

行波进位加法器

任务描述

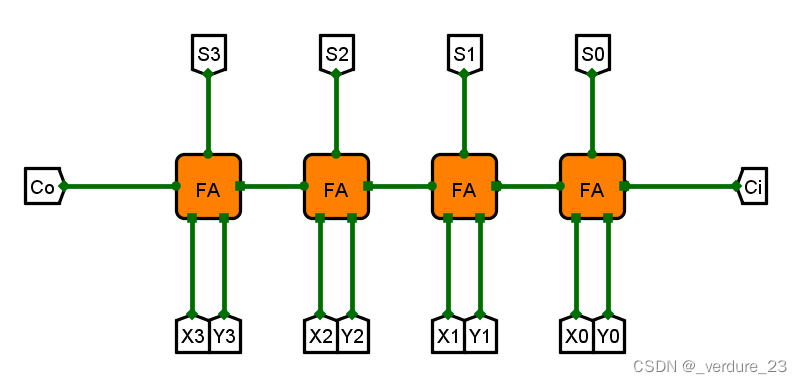

本关任务:在Logisim中,利用上一关设计的全加器FA级联设计一个4位的行波进位加法器。

相关知识

行波进位是指进位信号从低位逐位向高位传递,特点是结构简单,但速度比较慢。原理示意图如下

实验内容

实验电路框架与第一关相同。

在Logisim中打开实验电路框架,在工程中的“4位行波进位加法器”子电路中,利用全加器模块级联设计一个4位的加法器。

实验截图:

一位十进制加法器设计

任务描述

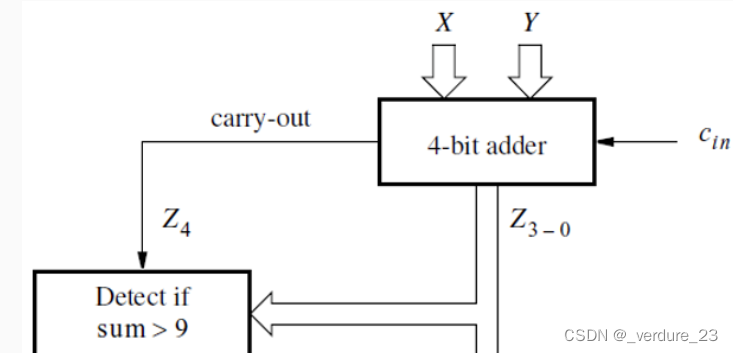

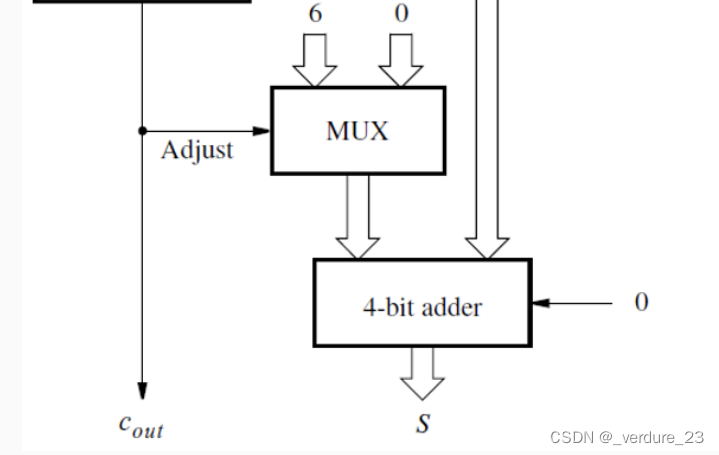

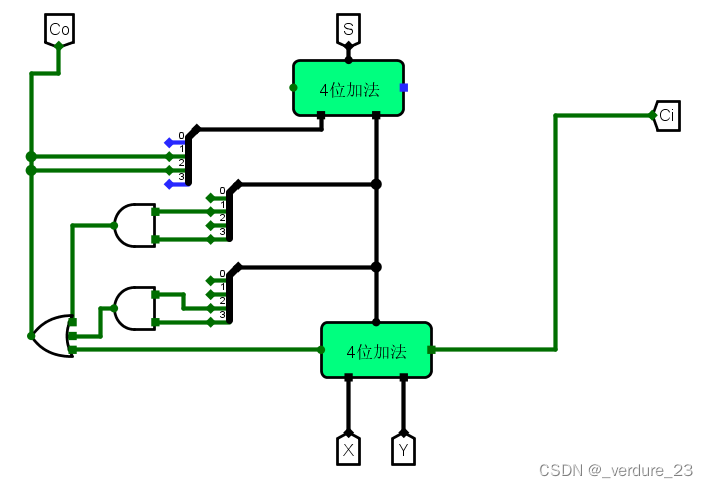

本关任务:在Logisim中,利用上一关的4位加法器来设计一个1位十进制数(8421BCD)加法器电路。

相关知识

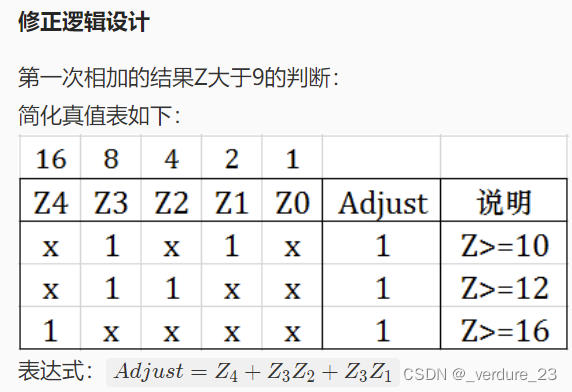

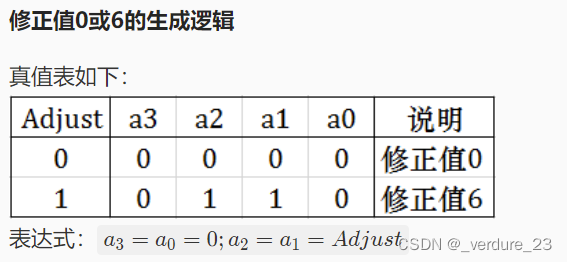

BCD码加法原理

1位十进制数(8421BCD码)加法原理图如下

实验内容

实验电路框架与第一关相同。

在Logisim中打开实验电路框架,在工程中的“1位十进制加法器”子电路中,利用4位加法器和适当的门电路来设计完成1位BCD码加法器电路。

本实验要用到线路库(Wiring)中的“分线器(Splitter)”!

本实验禁止使用比较器和多路选择器MUX!

拓展设计建议

完成上述实验后,可以在本地尝试多位十进制加法器设计、8421码到余3码的转换电路设计等。

实验截图:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?