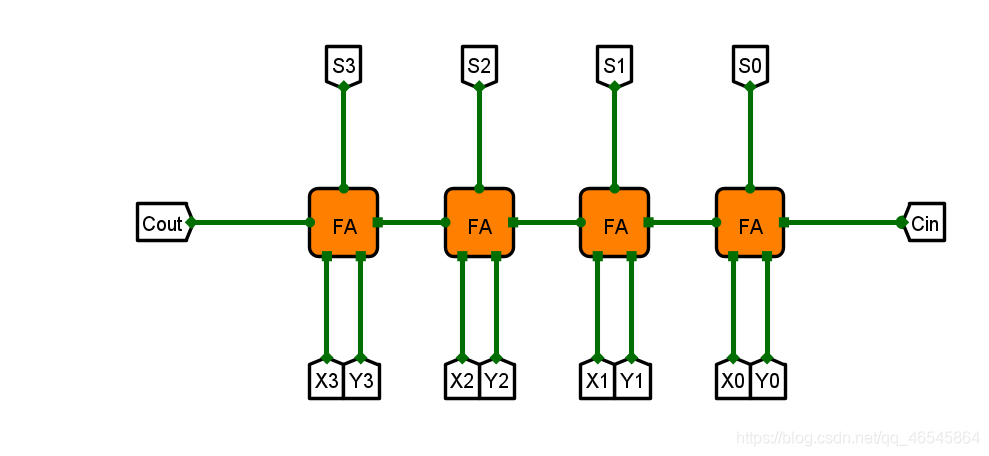

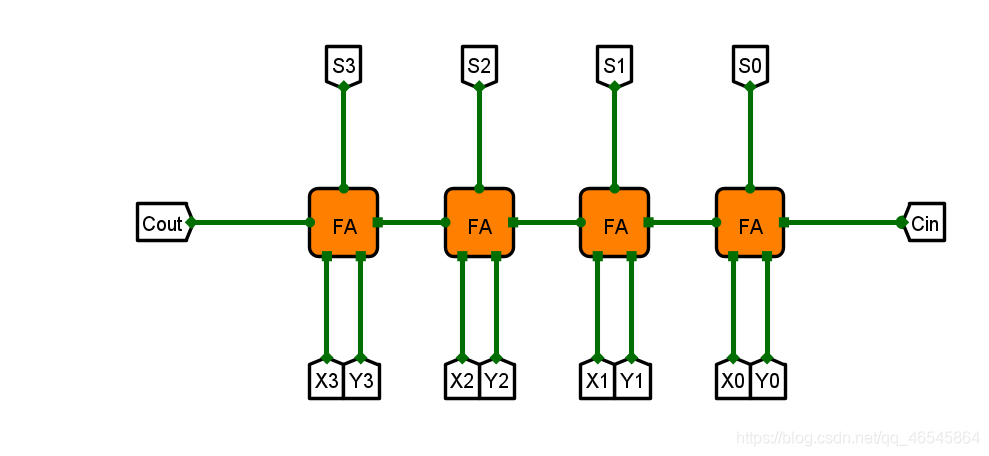

在Logisim中,利用上一关设计的全加器FA级联设计一个4位的行波进位加法器。

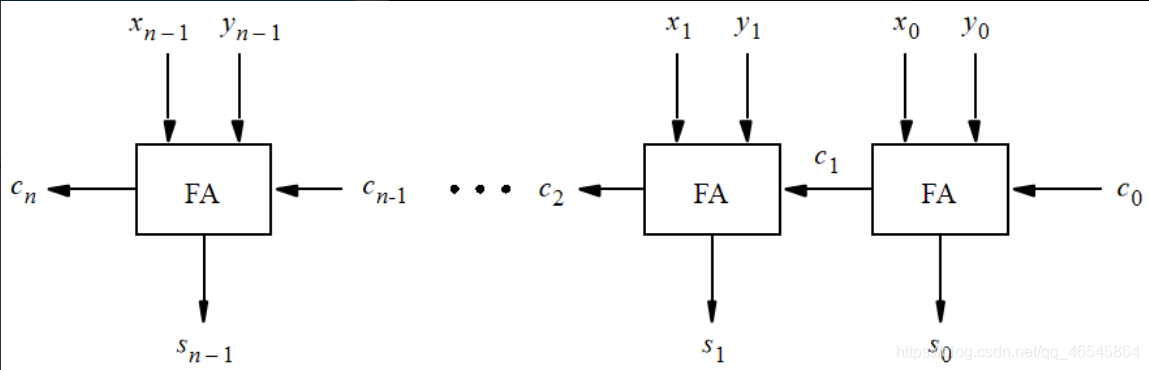

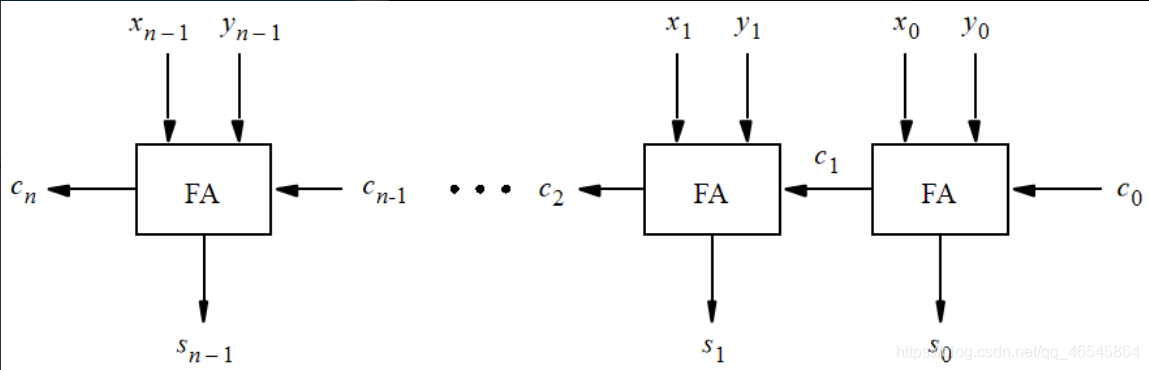

行波进位是指进位信号从低位逐位向高位传递,特点是结构简单,但速度比较慢。原理示意图如下:

在Logisim中,利用上一关设计的全加器FA级联设计一个4位的行波进位加法器。

行波进位是指进位信号从低位逐位向高位传递,特点是结构简单,但速度比较慢。原理示意图如下:

4846

4846

557

557

1847

1847

6004

6004

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?