Verilog 递减运算符(缩减运算符)(Reduction operator ),以及$display系统函数 ModelSim 仿真

更多操作符请参考这篇:

https://blog.csdn.net/malcolm_110/article/details/107784776

递减运算符(Reduction Operators)为单目运算符,运算符紧跟变量,结果为1bit值。

如“&C”表示将C的第一位与第二位相与,再将结果与第三位相与,再与第四位…一直到最后一位。

| Operator | Description |

|---|---|

| & | and |

| ~& | nand |

| | | or |

| ~| | nor |

| ^ | xor |

| ^~ or ~^ | xnor |

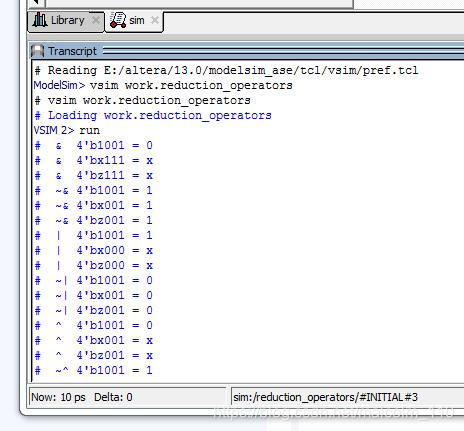

仿真:

1.打开modlesim, File – new – source ,输入如下代码。

2. Saveas

3. 点击compile,找到刚才存储文件的路径,选中文件。

4. 点击simulate,在弹出串口中,点击最上面work前面的加号,选中跟module相同名字的选项,点右下角OK。

5. 在下面的transcript串口输入run命令,即可看到$display 函数的效果。

拷贝如下代码:

module reduction_operators();

initial begin

// Bit Wise AND reduction

$display (" & 4'b1001 = %b", (& 4'b1001));

$display (" & 4'bx111 = %b", (& 4'bx111));

$display (" & 4'bz111 = %b", (& 4'bz111));

// Bit Wise NAND reduction

$display (" ~& 4'b1001 = %b", (~& 4'b1001));

$display (" ~& 4'bx001 = %b", (~& 4'bx001));

$display (" ~& 4'bz001 = %b", (~& 4'bz001));

// Bit Wise OR reduction

$display (" | 4'b1001 = %b", (| 4'b1001));

$display (" | 4'bx000 = %b", (| 4'bx000));

$display (" | 4'bz000 = %b", (| 4'bz000));

// Bit Wise OR reduction

$display (" ~| 4'b1001 = %b", (~| 4'b1001));

$display (" ~| 4'bx001 = %b", (~| 4'bx001));

$display (" ~| 4'bz001 = %b", (~| 4'bz001));

// Bit Wise XOR reduction

$display (" ^ 4'b1001 = %b", (^ 4'b1001));

$display (" ^ 4'bx001 = %b", (^ 4'bx001));

$display (" ^ 4'bz001 = %b", (^ 4'bz001));

// Bit Wise XNOR

$display (" ~^ 4'b1001 = %b", (~^ 4'b1001));

$display (" ~^ 4'bx001 = %b", (~^ 4'bx001));

$display (" ~^ 4'bz001 = %b", (~^ 4'bz001));

#10 $finish;

end

endmodule

可以看到如下效果:

& 4'b1001 = 0

& 4'bx111 = x

& 4'bz111 = x

~& 4'b1001 = 1

~& 4'bx001 = 1

~& 4'bz001 = 1

| 4'b1001 = 1

| 4'bx000 = x

| 4'bz000 = x

~| 4'b1001 = 0

~| 4'bx001 = 0

~| 4'bz001 = 0

^ 4'b1001 = 0

^ 4'bx001 = x

^ 4'bz001 = x

~^ 4'b1001 = 1

~^ 4'bx001 = x

~^ 4'bz001 = x

7239

7239

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?