一、实验任务及要求

1. 设计要求

设计一个模10的计数器,其变换规律为:1、3、5、7、9、0、2、4、6、8,间隔时间为1S,如此反复,并将数字显示在一个数码管上。要求电路具有:

1)启动开关,当该开关断开时,数码管没有显示,当开关闭合后,电路开始运行;

2)暂停键,在电路运行过程中按下此键,数码管显示停在此时正在显示的某一个数值上并保持,当再按下此键,电路继续计数显示;

3)复位按钮,当按下此按钮时,数码管显示初值为1,合上启动开关后,电路按照要求的顺序进行显示。

二、思考题

1. 设计过程中遇到过哪些问题?是如何解决的?

2. 通过此次时序逻辑电路实验,谈谈你对时序逻辑电路设计的认识

三、模10的计数器设计

第一种思路:

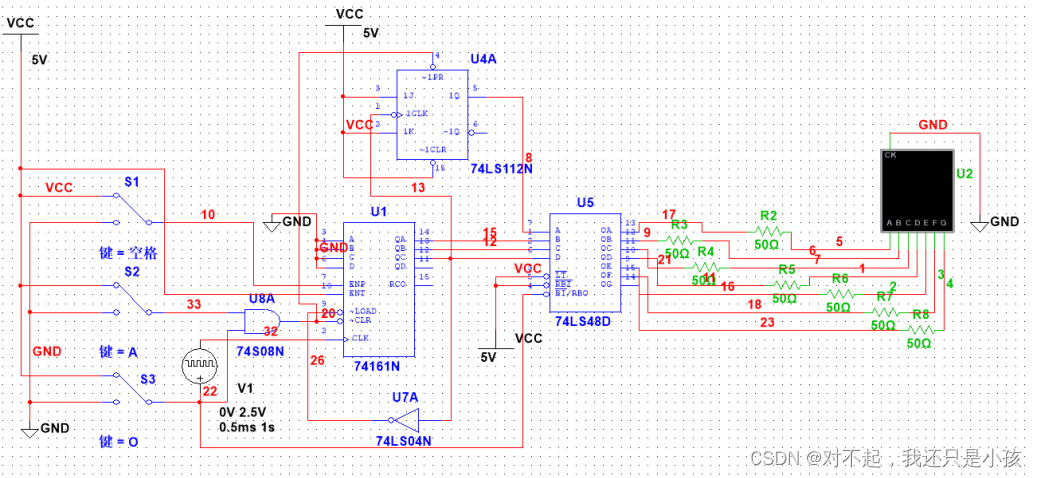

实验电路仿真如下 :

(1)此次实验主要用到的芯片有74161N计数器,74LS48D和JK触发器。

(2)其变换规律为:1、3、5、7、9、0、2、4、6、8。写出二进制可知,13579末位都为1,前三位按000,001,010,011,100排列。02468也一样,只是末位为0.所以末位从0到1可用触发器的计数功能来实现。当时钟信号(由计数器计数到0100时翻转)实现翻转,即8->1,9->0。

(3)74161N计数器设置从0000到0100计数,当0100时重新置数0(返回load端)。

(4)启动开关(O)后接RBO灭0,使得当该开关断开时,时钟断开,而且数码管没有显示(RBO灭零),当开关闭合后,电路开始运行。

(5)暂停键(空格)是利用74161N的ENP端,当低电平时,计数保持。

(6)复位(A)是异步清零实现的,同时利用JK触发器的PR端置1,使其初始状态为0。

(7)另外加上了启动开关与上复位开关,使得启动开关每次打开都是以1为初始态。

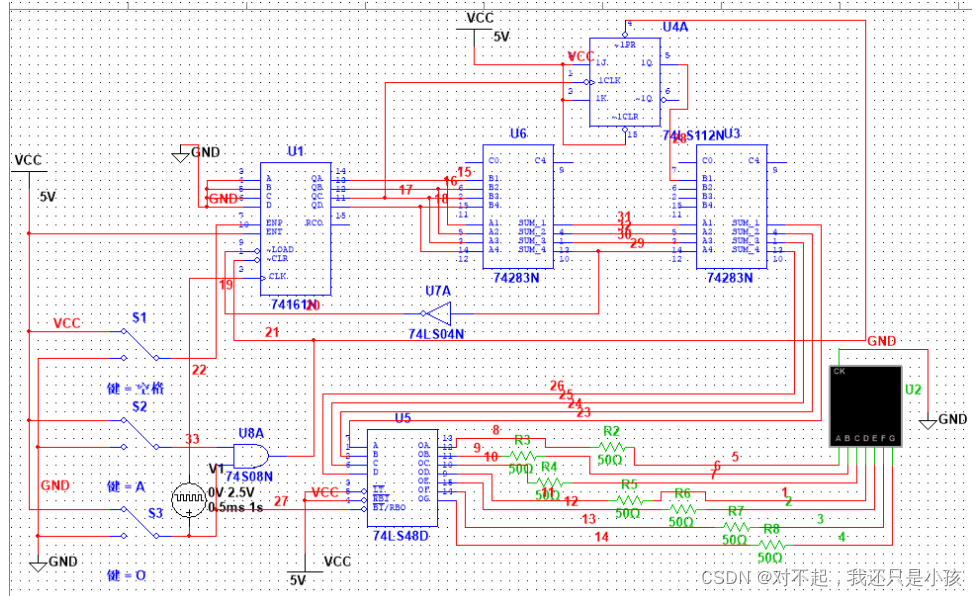

另一个思路

所有开关与前面设计一致,只是在计数方面前面的移位变成用了加法器(自身加法器,如0+0=0,1+1=2),而此时的JK触发器变成了一个加数,即图中有两个加法器。其他设计基本与前面一样。

总结

由于仿真器材完善,所以此次两个小实验均无悬空的无用输入端,基本上都是现有芯片和门电路构成。

1.对于高电平有效输入的与门,可以将该端置1

2.对于高电平有效输入的或门,可以将该端置0

3.计数器控制端的异步清零不需要时钟,而置数需要等到下一个时钟。

Multisim仿真文件(仅供学习参考):

链接:百度网盘 请输入提取码

提取码:6666

本文介绍了设计一个模10计数器的实验,包括使用74161N计数器、JK触发器实现数字变换,并结合启动、暂停和复位按键控制。作者分享了遇到的问题及解决方案,探讨了时序逻辑电路设计的理解。附有Multisim仿真文件供学习参考。

本文介绍了设计一个模10计数器的实验,包括使用74161N计数器、JK触发器实现数字变换,并结合启动、暂停和复位按键控制。作者分享了遇到的问题及解决方案,探讨了时序逻辑电路设计的理解。附有Multisim仿真文件供学习参考。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?