目录

1.2 那什么是HP Bank,HR Bank,甚至HD Bank呢?

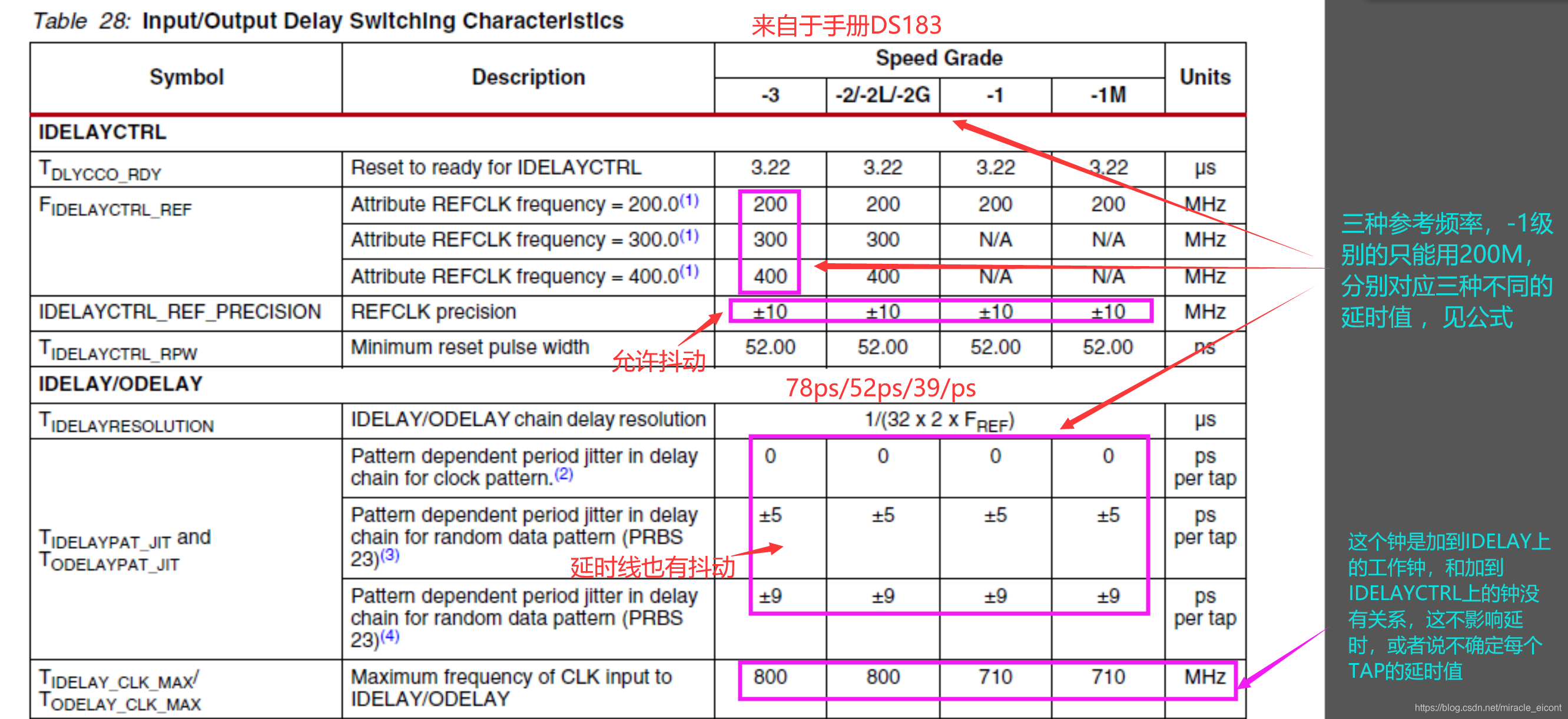

2.4 IDELAY2到底可以延时多长时间?(以V7 T 系列为例,IDELAY是IDELAY2)

摘要:为了调整项目中的时钟与数据的时序关系,常常需要用到IDELAY这样的PRIMITIVES,如何更好的来开发使用IDELAY,到底它是如何工作的,它和IDELAYCTRL又是如何连动的呢,这里做了一点探讨,本文以V7的IDELAY2和IDELAYCTRL来整理,对基本的东西没有展开,如果使用过这类SelectIO Primitives的,希望有所帮助。

1.xilinx 7系列的SelectIO逻辑资源

1.1SelectIO基本情况

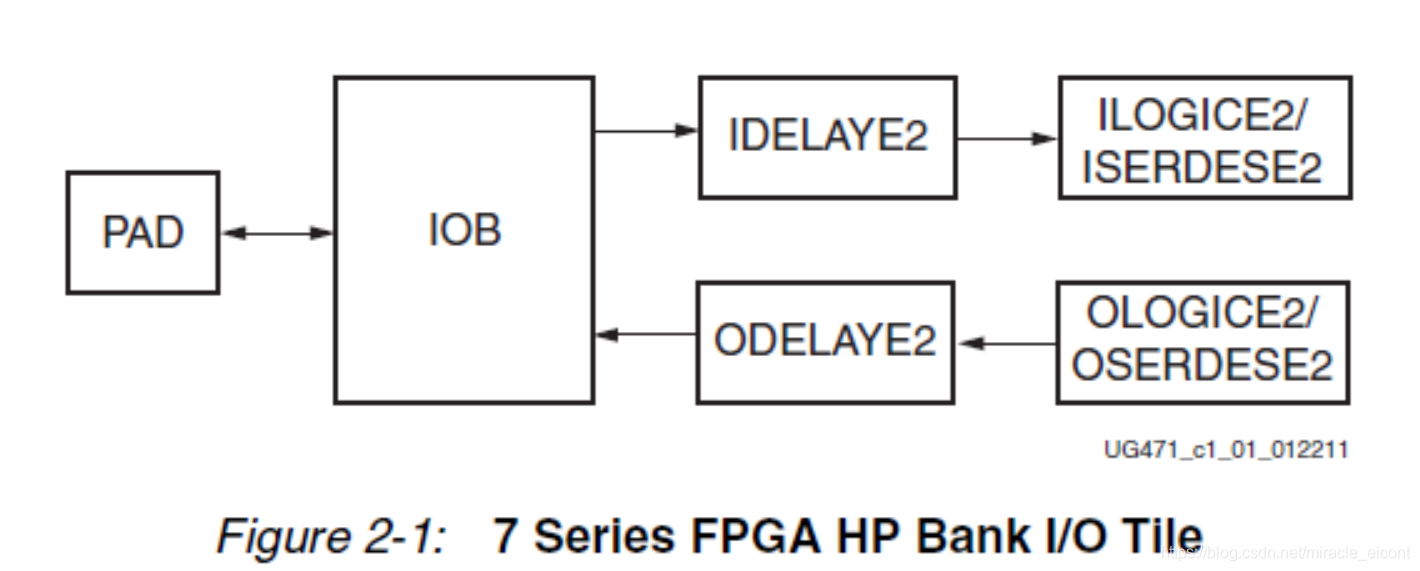

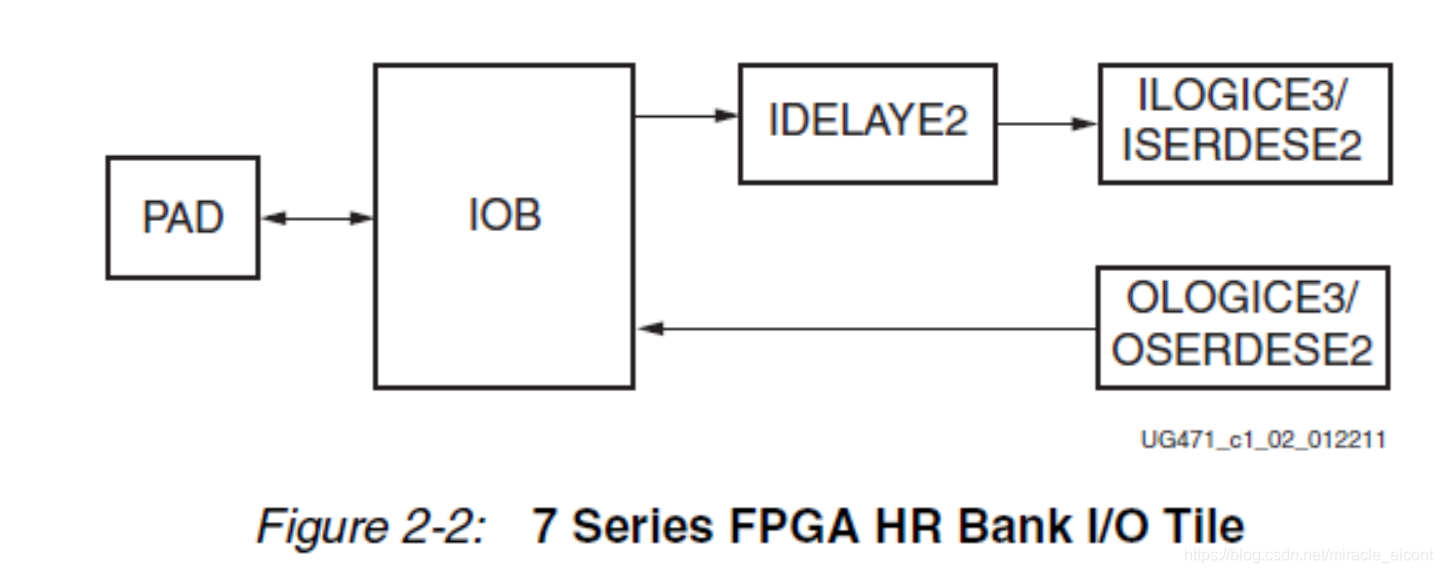

可以用两个图来说,对于HP Bank,是这样的

对于HR Bank是这样的

1.2 那什么是HP Bank,HR Bank,甚至HD Bank呢?

- The HR I/O banks are designed to support a wider range of I/O standards with voltages up to 3.3V. 简单说,就是支持宽电压的IO Bank

- The HP I/O banks are designed to meet the performance requirements of high-speed memory and other chip-to-chip interfaceswith voltages up to 1.8V. 简单说就是支持高性能,也即是高速的IO Bank

- The HD I/O banks are designed to support low-speed interfaces. 简单说就是高密度的,支持低速接口的IO Bank

The 7 series FPGAs offer both high-performance (HP) and high-range (HR) I/O banks. 7系列中只有HP 和 HR 没有HD

再上个表格对比下

| HR bank | HP bank | HD bank | |

| 全称 | High Range | High Performance | High Desity |

| 名称 | 高范围bank | 高性能bank | 高密度bank |

| 电压范围 | 1.2~3.3V | 1.0~1.8V | 1.2~3.3V |

| 接口速率 | 支持高速接口 | 支持低速接口 |

2. IDELAY2(重点说)

2.1基本情况

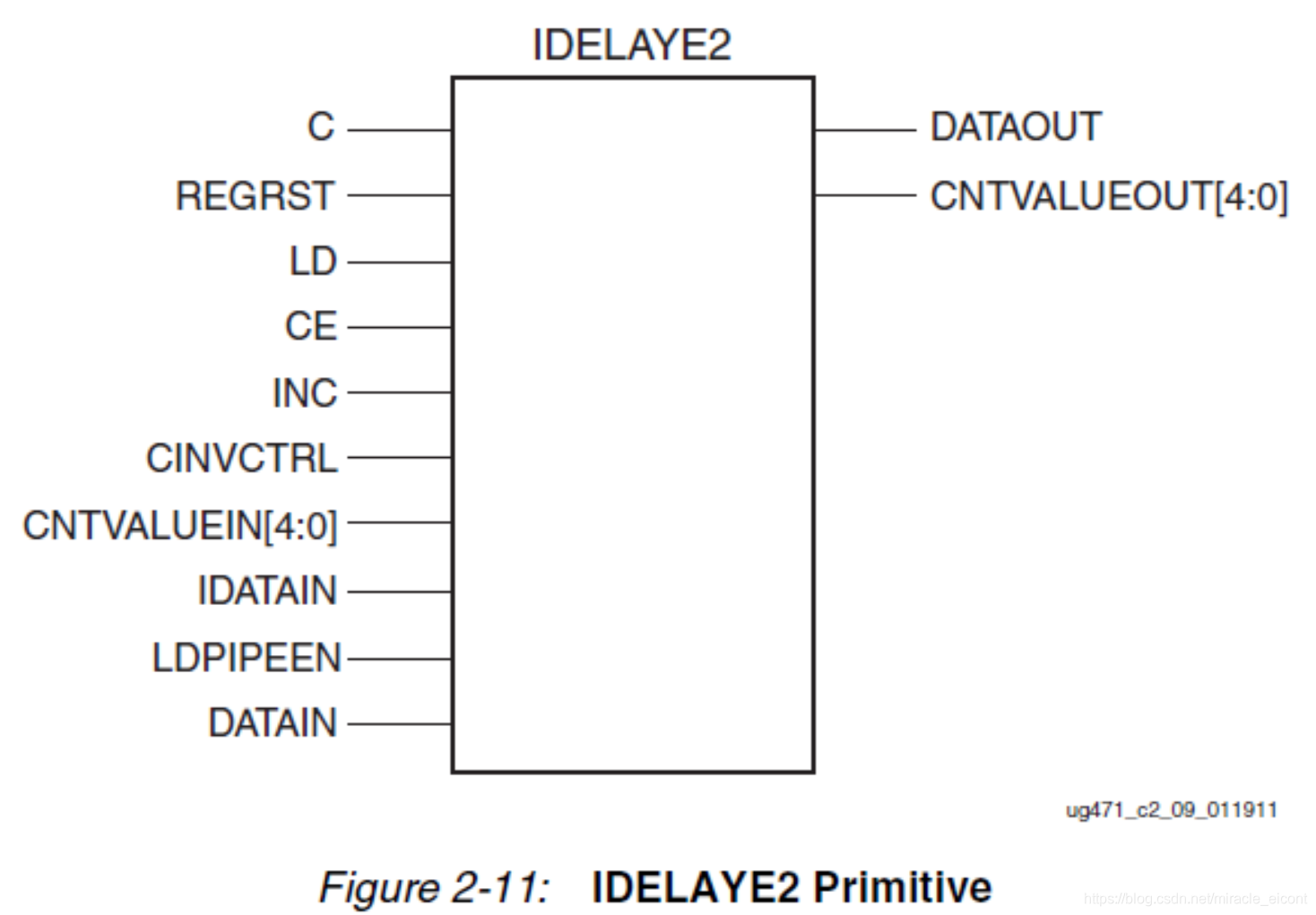

IDELAY2是一个专用的延时单元,有31级,延时线每级的可分辨的延时时间是由专用的IDELAYCTRL提供的,一个时钟区域内一个IDELAYCTRL同时供多个IDELAY2,它 的逻辑图如下:

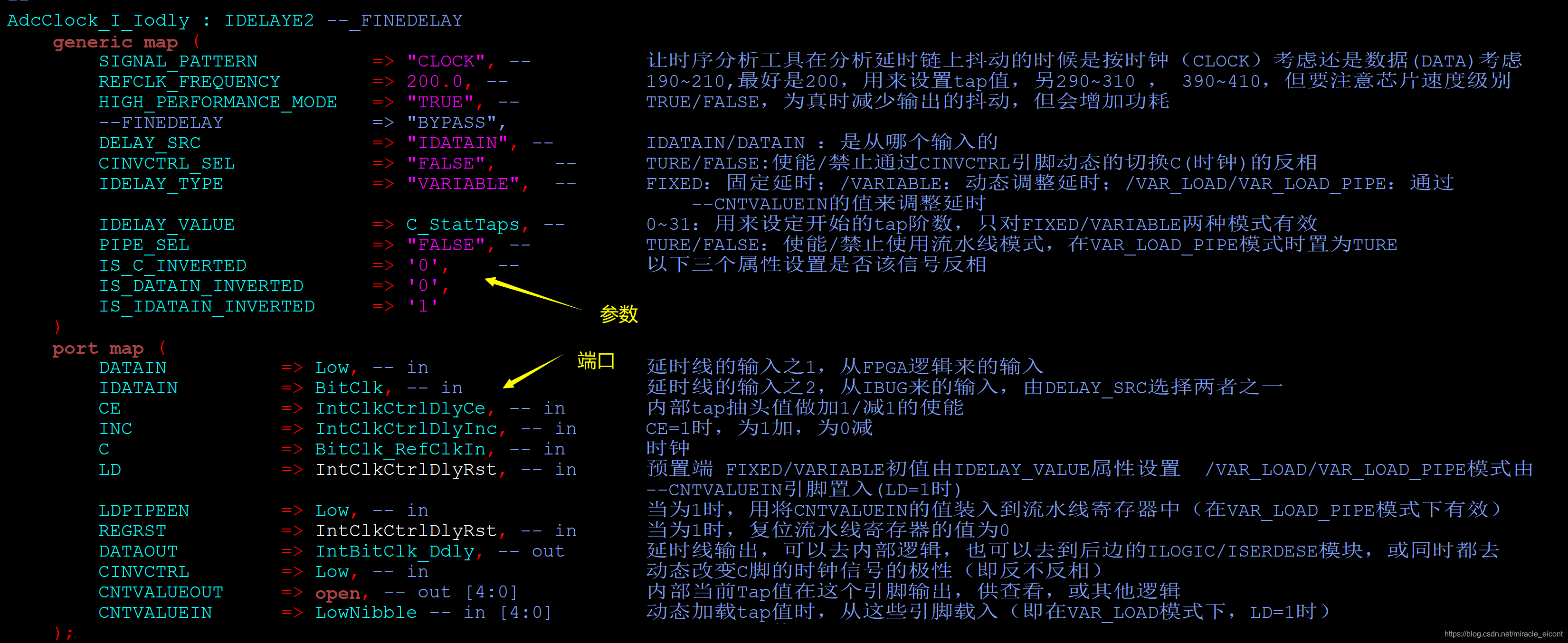

2.2属性和引脚

这个直接上图吧,不要看端口接的是啥,重点看后边注释

2.3 四种工作模式有啥不同

- FIXED模式下,延时是固定的,其抽头值由属性IDELAY_VALUE确定的,不用动态装载,工作时也不能变化;

- VARIABLE模式下,延时是可变的,其初如抽头值也是由属性IDELAY_VALUE确定的,在工作时,在C(时钟)作用下,当CE=1时(使能),由INC引脚控制抽头值的增(=1)和减(=0),且会由31->0(增时)或由0->31(减时);

- VAR_LOAD模式,与VARIABLE模式不同之处在于:可以装入初值,怎么装:LD=1时,把CNTVALUEIN的值装入延时线;

- VAR_LOAD_PIPE和VAR_LOAD的区别在于:前者可以把延时线的tap(抽头)值的更新值可以先存到pipe register里(在LDPIPEEN=1时),然后再统一载入(在LD=1时)到tap ,在总线模式下非常有意义;而后者在LD=1时,直接载入CNTVALUEIN的值至tap;

2.4 IDELAY2到底可以延时多长时间?(以V7 T 系列为例,IDELAY是IDELAY2)

- 这个延时是由物理延时线产生的,故只能往后延不会往前延,也即只是正的延时,这是个基本概念;

- 这个延时可以理解为不同延时线抽头实现,改变了Tap值就可以改变延时的大小,由下图可见每个抽头延时的大小(也叫resolution)是 1/(32x2xfref),亦即与参考频率有关。fref=200MHz是78ps

- 当用IDELAY来传clock类信号时,其延时基本没有误差,为啥呢,因为基本时钟信号比较规矩,有规律,看下图

- 当用IDELAY来传data类信号时,其延时就不准了,有误差,为啥呢:数据信号和时钟信号不一样呗。如果想减少误差,就将IDELAY的属性HIGH_PERFORMANCE打开,看下边图啊

- 一共是31个Tap所以总延时也就是78x31=2.418ns(或者理解为200M时钟周期的一半),换句话就是说,IDELAY撑死也就至多延时2.5ns(参考频率更高的,延时更小),所以如果项目设计时采用的时钟比较低,想用IDELAY来改变时钟/数据的时序关系,这就有点杯水车薪的感觉,思路应该不是正选。

- 使用IDELAY都要配IDELAYCTRL,这中间的门道到底是啥,没有人说,xilinx也不会讲,下边补点IDELAYCTRL的内容

3.输入延迟控制(IDELAYCTRL)

3.1 IDELAYCTRL概述

如果IDELAYE2或者ODELAYE2例化时,IDELAYCTRL也必须例化。手册里基本都是这句:该模块的用途是对IDELAYE2或者ODELAYE2的延时tap进行校准,减少处理过程、电压和温度的影响,使用REFCLK时钟精细校准。这解释有点懵逼,说到底:(1)IDELAY2和IDELAYCTRL到底是啥关系;(2)IDEALY2到底是怎样实现的延时?所以说会使用,不见得真明白,不明白是因为压根就没有解释,总之吧,会用就可以了

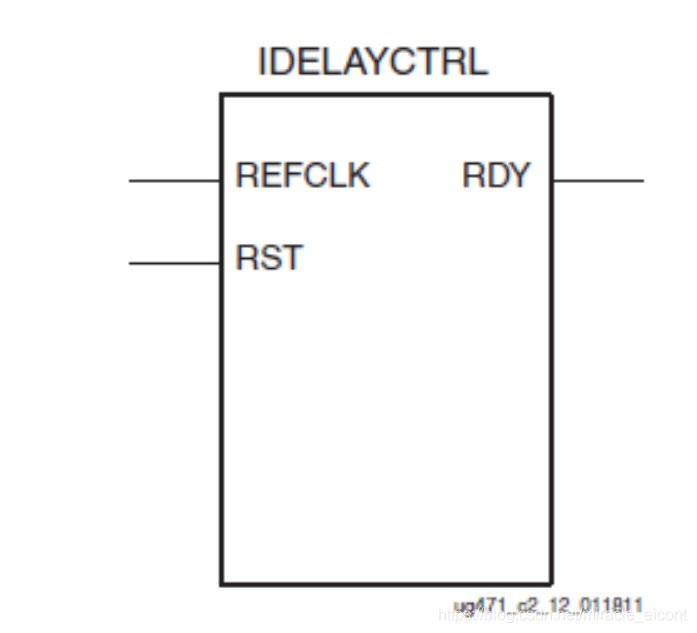

3.2 IDELAYCTRL原句及端口

1.RST:复位信号

RST端口高电平复位,异步复位。为了确保恰当的IDELAY和ODELAY操作,在REFCLK时钟稳定后,必须对IDELAYCTRL进行复位。

2.REFCLK:参考时钟

REFCLK时钟为IDELAYCTRL提供校准时钟。该时钟必须由BUFG或者BUFH时钟缓冲器驱动。REFCLK可以直接来自用户提供的时钟源或者MMCM,但都必须布线到全局时钟buffer。

3.RDY:Ready信号

RDY信号指示IDELAY和ODELAY模块已经完成校准。如果RDY信号变为低电平,IDELAYCTRL模块必须进行复位处理。

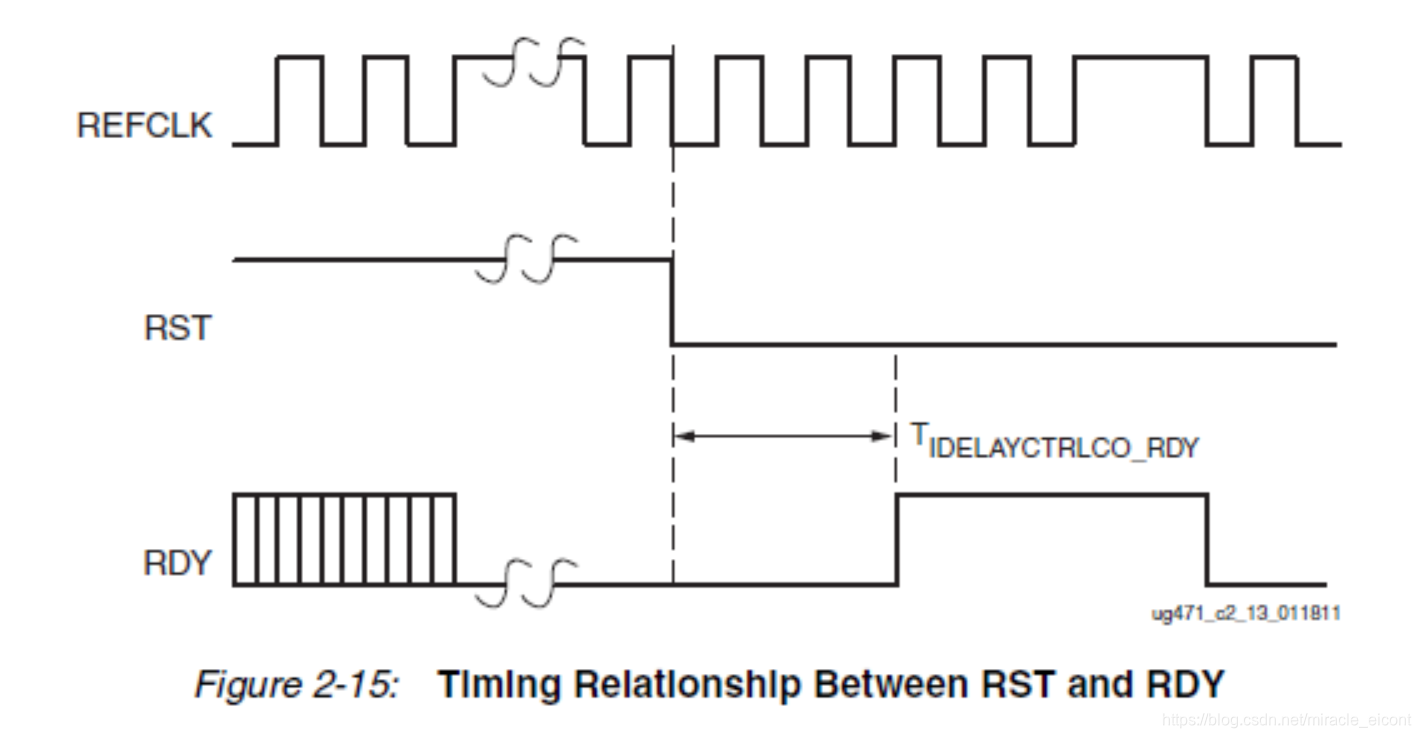

3.3 IDELAYCTRL时序

IDELAYCTRL控制时序图如图所示。

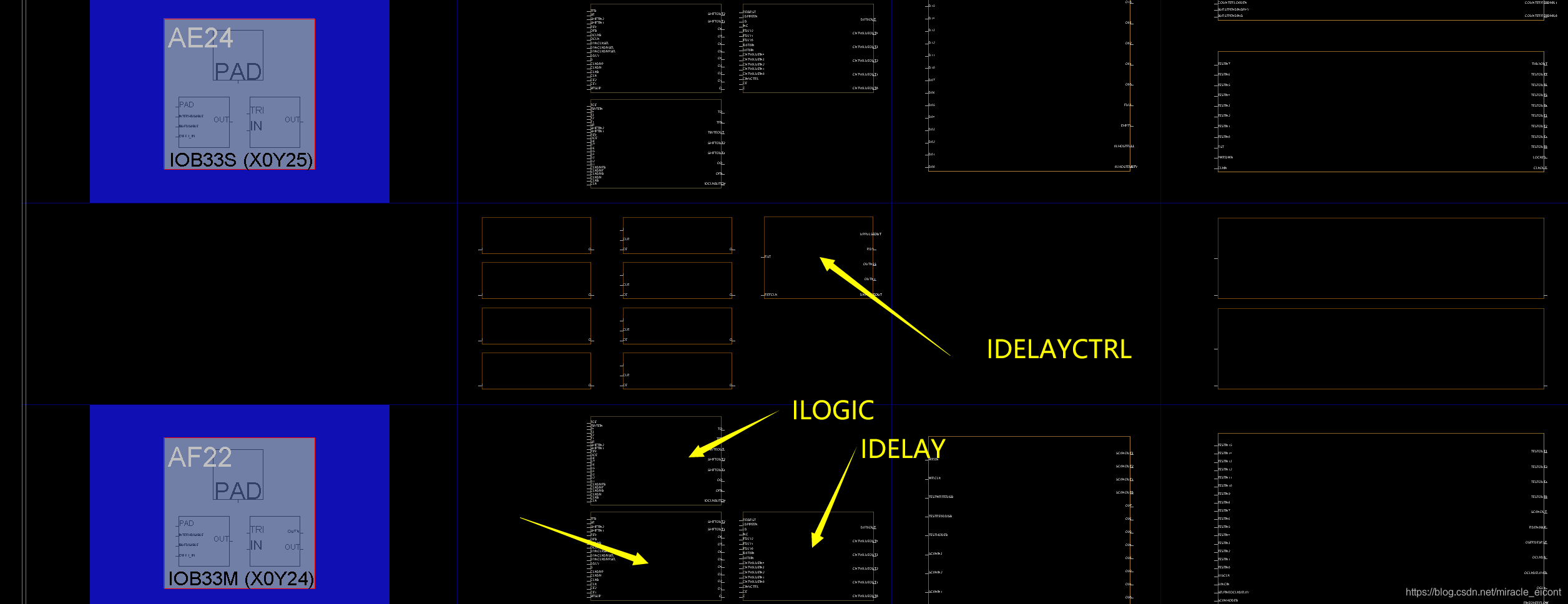

3.4 IDELAYCTRL位置

IDELAYCTRL位于I/O行的的每个时钟域。一个IDELAYCTRL完成它所在时钟域的所有IDELAYE2和ODELAYE2块的校准。截了个图,显示了IDELAYCTRL位置相关位置示意图。

4 参考文献

关于在FPGA中实现延时的探讨,这是2014年在电测与仪表上发表的论文用FPGA进位链实现延时的论文:基于CycloneIII的高精度时间数字转换设计 http://d.wanfangdata.com.cn/periodical/dcyyb201402018

1. https://www.xilinx.com/support/documentation/data_sheets/ds183_Virtex_7_Data_Sheet.pdf

2. https://www.xilinx.com/support/documentation/user_guides/ug471_7Series_SelectIO.pdf

3. https://www.xilinx.com/support/documentation/user_guides/ug472_7Series_Clocking.pdf

本文详细介绍了Xilinx 7系列FPGA中的SelectIO资源,特别是IDELAY2和IDELAYCTRL的工作原理。讨论了IDELAY2的四种工作模式及其在信号传输中的应用,并解释了IDELAYCTRL如何与IDELAY2配合使用以提高信号延时的准确性。

本文详细介绍了Xilinx 7系列FPGA中的SelectIO资源,特别是IDELAY2和IDELAYCTRL的工作原理。讨论了IDELAY2的四种工作模式及其在信号传输中的应用,并解释了IDELAYCTRL如何与IDELAY2配合使用以提高信号延时的准确性。

847

847

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?