通常ATE测试工程师是根据datasheet的电气特性表定义测试level的min/nom/max. 但是这样定义有一下问题:

- 电气特性表声明的工作电压范围是指一定温度范围下的,ATE测试一般是在个别温度下,如果测试温度不是worst case,即使DUT可以在datasheet 声明的min/nom/max条件下测试pass,在应用时的极端温度条件下依然无法工作;

- DUT随使用会有aging的问题,电气特性会老化变差。ATE测试的DUT是新出产的,测试条件需要考虑aging的问题

- ATE测试设备本身有精度问题,需要考虑精度的影响

- 产品的Vmin如何得到

以SRAM为例,一般foundry对与工艺都有电压工作范围的曲线:

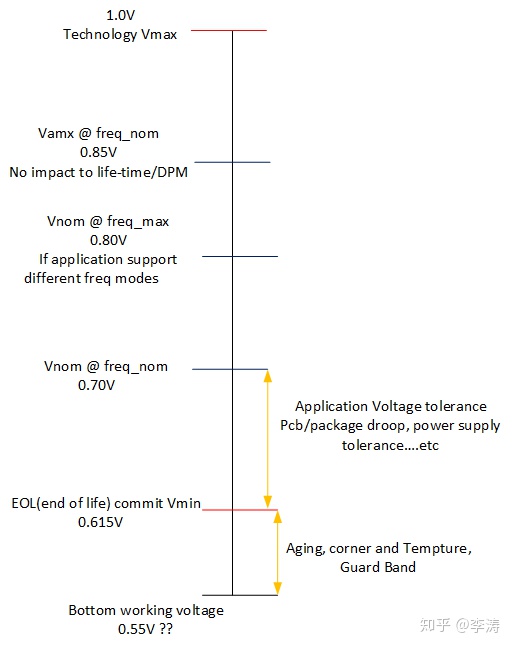

每个工艺都有理论上的bottom Vmin 和ceiling Vmax,超出这个范围是完全无法工作的。比如工艺的bottom vmin = 0.55V, 那么不同DUT的在EOL时的Vmin会受一下几个因素影响:

- aging factor ( 随着使用时间增加,vmin会变大)

- temperature factor(vmin 在有些温度会变大)

- corner factor (slow corner Vmin会大一些)

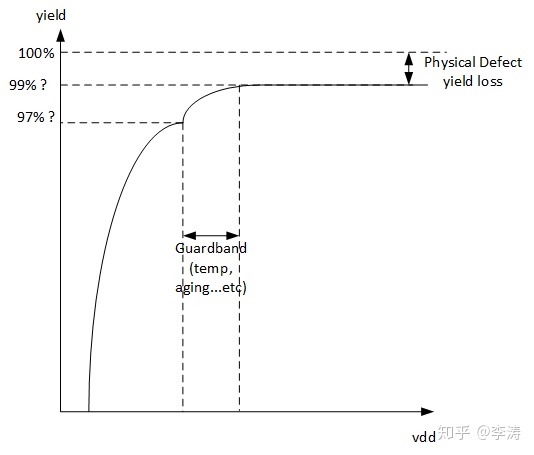

因此EOL vmin是考虑这些因素之后加了guardband得到的,理论上大部分好的DUT在EOL时Vmin在这个EOL vmin之下。

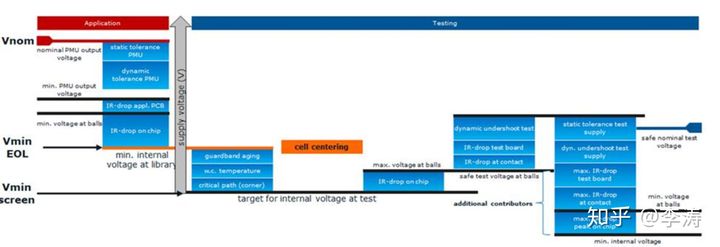

Datasheet在定义Vnom的时候需要考虑application的tolerance(例如供电芯片的电压偏差,板子和package引起的IR drop, 负载电流变化引起的overshoot/undershoot...etc), 一般会在EOL Vmin的基础上加一个合理的Guardband得到Vnom = 0.615+ 0.085 = 0.7V.

产品有可能有不同的工作频段,比如一般load的时候工作在Vmed (~400Mhz),load大的时候需要工作在Vhigh (~800Mhz)。不同工作频段的Vnom是根据toggling rate 或者 max load current估算的,比如上面的示例Vhighvnom = 0.8V and Vmed_nom = 0.7V, 0.1V是补偿load current导致更大的IR drop以及overshoot/undershoot。

工艺还会提供Vmax的参数,如果产品工作在Vmax下会造成stress带来的DPM以及life-time的问题。特别需要小心的是ceiling voltage是一定不能随便使用的,一般只有qualification stress,burn-in的时候会在ceiling voltage以上stress产品。

- ATE的level如何定义

建议EOL Vmin应该作为最低的screen level,以保证测试pass的产品可以在application board的Vnom下正常工作。

EOL Vmin的定义已经考虑了aging,Corner和temperature的worst case, 大部分产品是应该能meet这个target的,用着spec去screen不会引起非常大的yield loss.

如果我们知道了EOL Vmin = 0.615V,那么ATE的程序是设置为0.615V吗?当然需要考虑一下几点:

- aging的问题

测试的芯片可以pass 0.615V,但是使用5年以后也许就只能pass 0.625V了。因此需要 -20mv aging guardband,去screen现在的芯片。

aging的guard band估算需要工艺工程师提过,也可以通过一定数量新品的htol, burn-in去获取;

-ATE测试机和测试板的问题

需要考虑测试机的精度,测试板到芯片ball的IR drop, 负载电流变化时的undershoot/overshoot问题.

一般来说需要额外加上一定的+V_ate去补偿IR drop的问题,因此在早期可以先忽略这个因素,使用worst case。如果yield loss高,可以再考虑补偿IR drop

- 使用 EOL Vmin - Vaging + V_ate去screen,会造成deliver defect吗

假设ATE测试在25C下,在-10C时有worst Vmin。如果DUT在25C刚好pass 0.595V ( 0.615- 0.02V), 那么在 -10C EOL Vmin应该会大于0.615V。似乎 screen 没有考虑温度问题,是否应该- Vtemp?

其实这是一个概率分布问题。按照工艺指标,大部分芯片在所有温度下的EOL vmin都应该小于0.615V,只有很少的slow芯片会靠近或者超过EOL Vmin。所以使用EOL Vmin - Vaging + V_ate去在特定温度screen,也只会slip少量defect,应该还在DPM范围只能。

- 如何characterize EOL Vmin

在不同corner选取一定数量的sample去做Vmin测试

- 在不同温度进行Vmin测试, 不同温度的Vmin给出温度系数 (Vtemp);

- 测试Vmin drift在burn-in之前和之后 (Vaging);

- Vmin测试的同时测试电流load,估算IR drop

绘制Vmin分布去计算mean, sigma...etc 评估工艺提供的bottom Vmin和EOL vmin是否符合测试预期;

- 如何在production监控EOL Vmin

保留至少一个Vmin测试,监控process的drift问题。根据EOL vmin screen的yield loss也可以间接监控process的drift问题。

1023

1023

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?