先对题目要求及元器件介绍

一、要求:设计一个能实现从 00:00——23:59 计数的数字电子钟;

二、所用芯片:

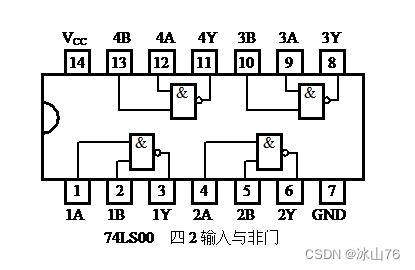

1.辅助芯片:74LS00 两片,用于分频器和计数器的复位:

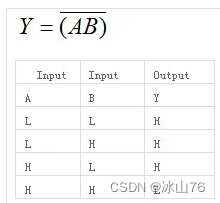

劲非 74LS08 两片,用于分频器和计数器的进位:5

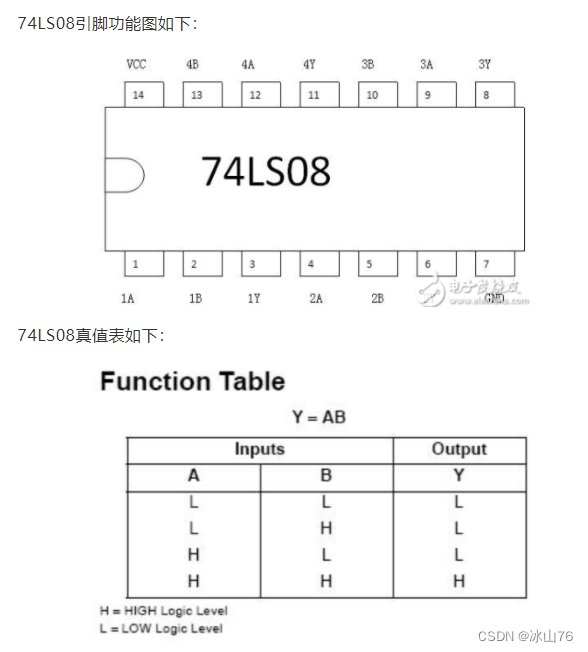

2.振荡部分:555 芯片一片,产生 1KHZ 的脉冲信号(8 脚接+5V 电源,1 脚接 地):10K 电阻两个,473 电容一个,103 电容一个;

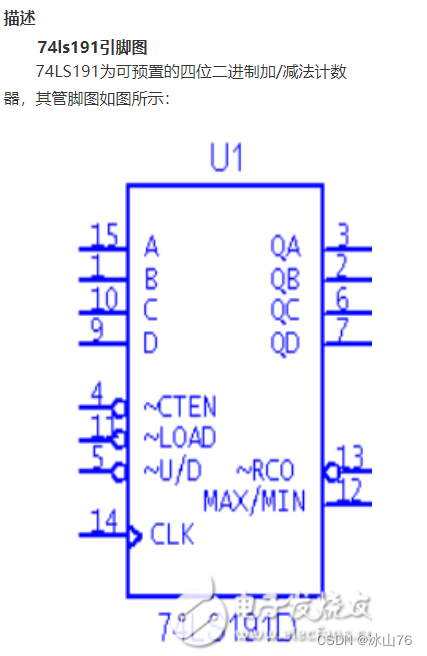

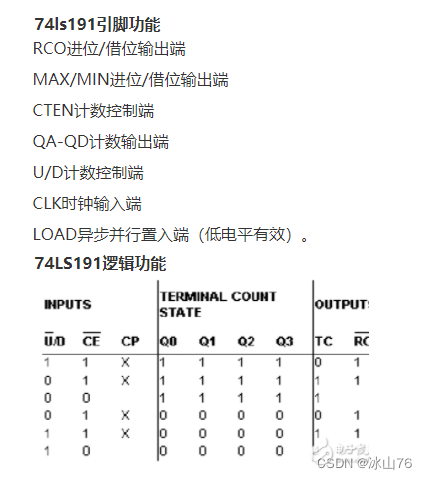

3.分频和计数部分:74LS191 芯片七片。其中三片用做十分频器,通过三次十 分频产生课程设计所需要的 1HZ 脉冲信号:另外四片用作计数器,秒位设 计成 60 进制,分位设计成 24 进制;

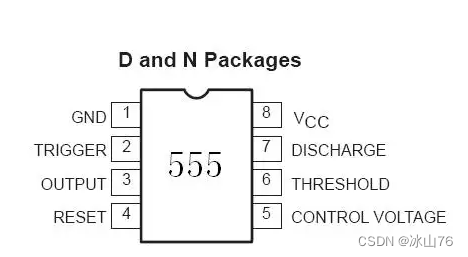

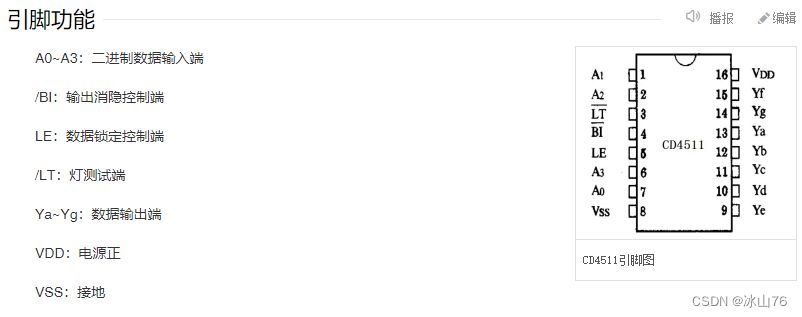

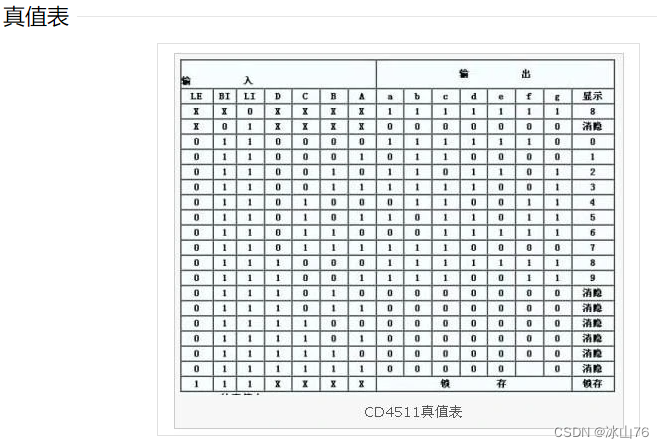

4.译码部分: CD4511 芯片四片,CMOS 芯片,七段显示译码器,其中有三个 辅助控制端:3 脚LT灯测试端,设计中不需要用到,直接接+5V 电源;4 脚:灭灯输入端,设计中也不需要用到,直接接+5V 电源;5 脚 LE 锁存使能输入端,设计中不需要用到,直接接地;

5.显示部分:“8”字型数码显示管四个,共有 A—G 七段,与 4511 芯片相配 套使用,共阴极数码管,中间的针需要接地。

三、注意事项: 1.所有芯片要接+5V 电源

根据题目要求,首先对芯片进行分析:

1.74LS00是双输入与非门,实现的是Y=(AB)'的功能,其逻辑图如下所示:

74LS00实现的是Y=(AB)'的功能,即

即只有AB两端同是高电平时,输出Y才为高电平,只要任何一个是低电平结果就是低电平

该芯片共有14个引脚,14、7为电源,剩余12个引脚分为四组,每组分别三个引脚,根据AB

输入情况得到Y输出,根据题目要求,它用来给分频器复位,如何实现复位功能,我们下面再说,先把每个芯片介绍完毕。

其中a b c d 为 BCD 码输入,a为最低位。LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,各笔段都被点亮,以检查显示器是否有故障。BI为消隐功能端,低电平时使所有笔段均消隐,正常显示时, B1端应加高电平。另外 CD4511有拒绝伪码的特点,当输入数据越过十进制数9(1001)时,显示字形也自行消隐。LE是锁存控制端,高电平时锁存,低电平时传输数据。a~g是 7 段输出,可驱动共阴LED数码管。 CD4511和 CD4518配合而成一位计数显示电路,若要多位计数,只需将计数器级联,每级输出接一只 CD4511 和 LED 数码管即可。所谓共阴 LED 数码管是指 7 段 LED 的阴极是连在一起的,在应用中应接地。限流电阻要根据电源电压来选取,电源电压5V时可使用300Ω的限流电阻。

这一部分先把题目及所用器件的基本介绍弄出来,下面就开始研究如何实现,在我们要做任何一个东西之前,我们可以把这个系统分为三大部分:输入、处理、输出

根据题目我们可知,输入就是时间,时间不同产生的高低电平变化,输入我们的系统,经过我们的系统处理,得到数码管的显示,显示的格式就是时间 时,分,并且时间应该越精确越符合题意,如果系统时间从00:00开始,经过一个小时,显示为01:00最为正确,如果设计过程中对细节处理不足,那最终一个小时后的结果就不是大于就是小于,偏差越大,设计越不合理。

首先我们设计输入部分,题目已经告诉我们如何产生秒信号,我们需要的是硬件电路的实现,今天工作事特别多,又要忙了,先把这些写出来,把芯片认识清楚,明天再弄实现部分

1917

1917

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?