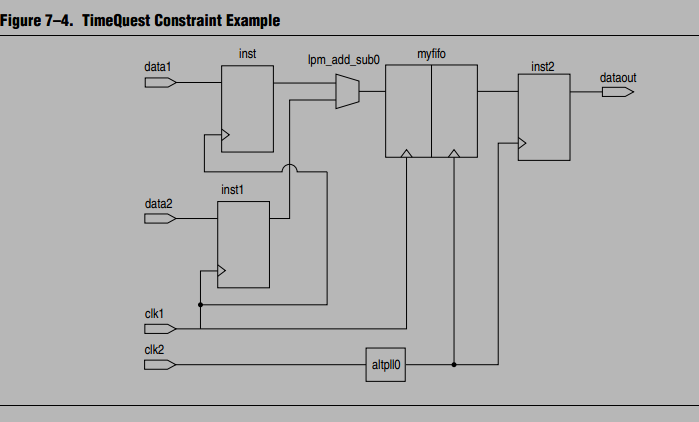

下面的example包含了两个时钟,一个PLL和一些其他的同步设计单元。如下图:

下面的.sdc文件包含了上述的电路的基本约束:

#创建时钟

create_clock -name clockone -period 10.000 [get_ports {clk1}]

create_clock -name clocktwo -period 10.000 [get_ports {clk2}]

#创建虚拟时钟——用于对IO做输入输出约束

create clock -name clockone_ext -period 10.000

create clock -name clockone_ext -period 10.000

#约束锁相环时钟

derive_pll_clocks

# 约束锁相环时钟不确定性

derive_clock_uncertainty

#设定异步时钟组

set_clock_groups \

-asynchronous \

-group {clockone} \

-group {clocktwo altpll0|altpll_component|auto_generated|pll1|clk[0]}]

#设定输入输出延迟约束——相对于虚拟时钟

set_input_delay -clock { clockone_ext } -max 4 [get_ports {data1}]

set_input_delay -clock { clockone_ext } -min -1 [get_ports {data1}]

set_input_delay -clock { clockone_ext } -

本文档详细介绍了如何使用SDC文件为包含PLL的FPGA设计设置时序约束。主要步骤包括定义时钟、创建虚拟时钟、约束PLL时钟、设置时钟不确定性、定义异步时钟组以及设定输入输出延迟,以确保设计的正确性和可靠性。

本文档详细介绍了如何使用SDC文件为包含PLL的FPGA设计设置时序约束。主要步骤包括定义时钟、创建虚拟时钟、约束PLL时钟、设置时钟不确定性、定义异步时钟组以及设定输入输出延迟,以确保设计的正确性和可靠性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?