5.2 锁存器

5.2.1 SR锁存器

5.2.1 D锁存器

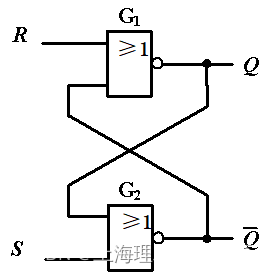

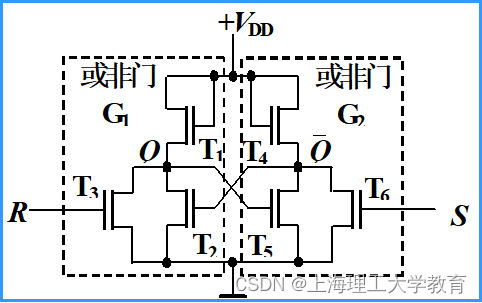

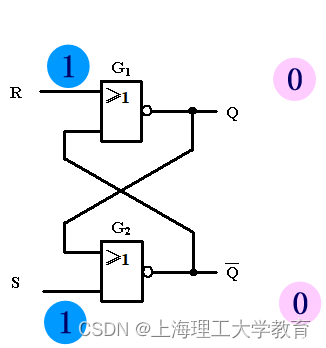

1. 基本SR锁存器

初态:R、S信号作用前Q端的状态,初态用Q n表示。

次态:R、S信号作用后Q端的 状态次态用Q n+1表示。

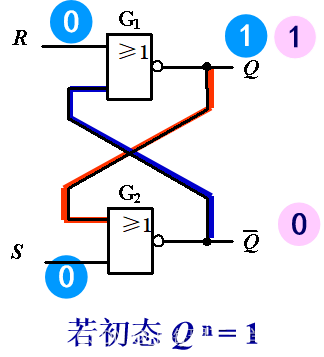

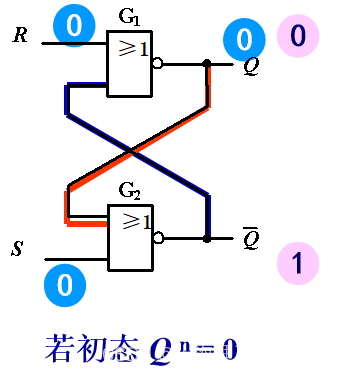

1) 工作原理

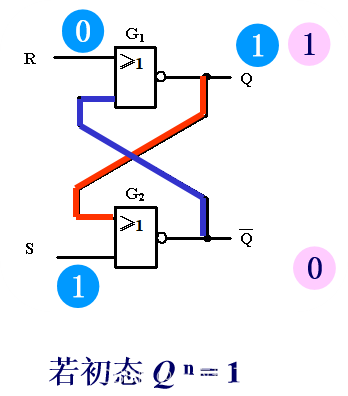

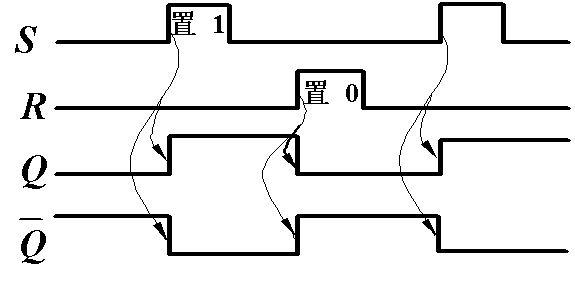

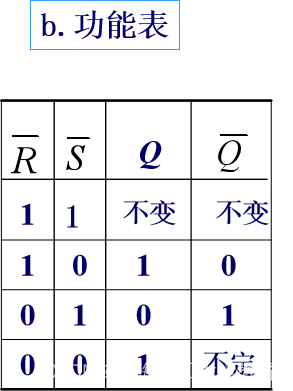

R=0,S=0 状态不变

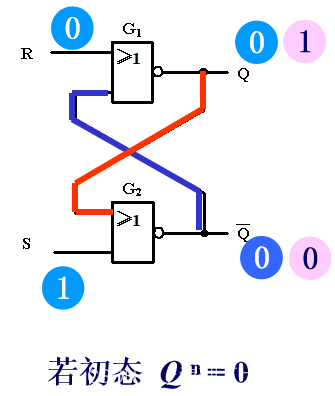

R=0,S=1 置1

无论初态Q n为0或1,锁存器的次态为为1态。 信号消失后新的状态将被记忆下来。

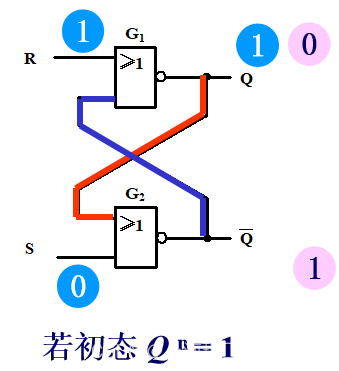

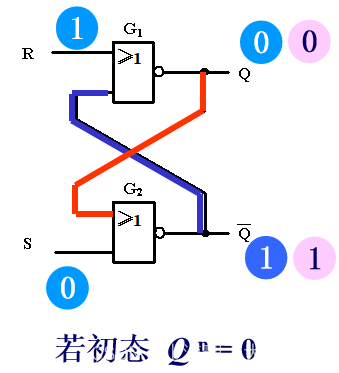

R=1,S=0 置0

无论初态Q n为0或1,锁存器的次态为0态。 信号消失后新的状态将被记忆下来。

S=1,R=1 状态不确定

无论初态Q n为0或1,触发器的次态 Qn+1 、Qn+1非 都为0 。

触发器的输出既不是0态,也不是1态

当S、R 同时回到0时,由于两个与非门的延迟时间无法确定,使得触发器最终稳定状态也不能确定。

约束条件: SR=0

3)工作波形

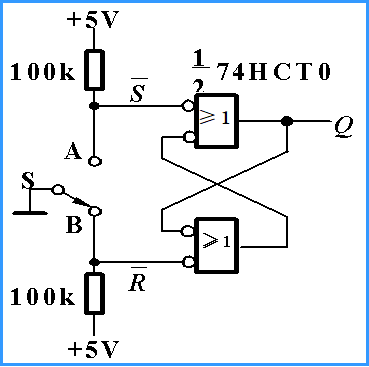

4)用与非门构成的基本SR锁存器

A.电路图

B.功能表

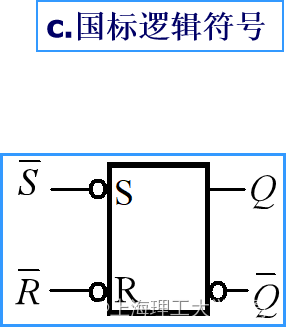

C国际逻辑符号

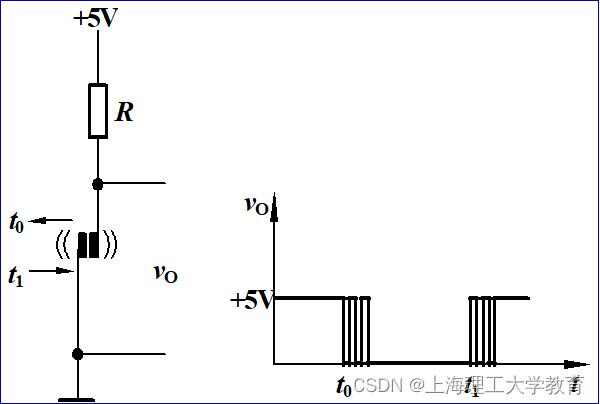

例 运用基本SR锁存器消除机械开关触点抖动引起的脉冲输出。

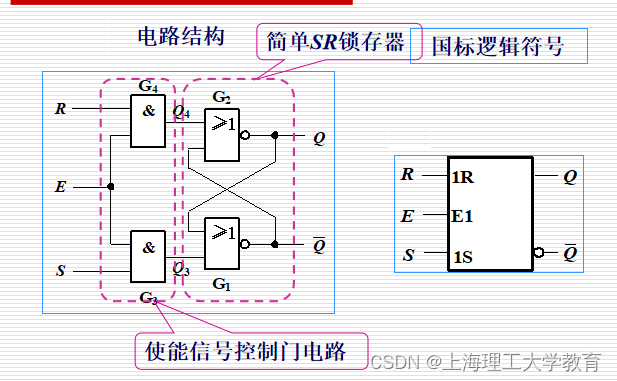

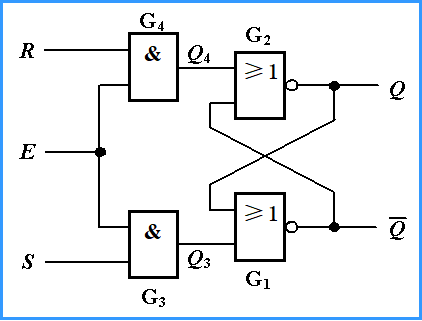

2. 逻辑门控SR锁存器

电路结构

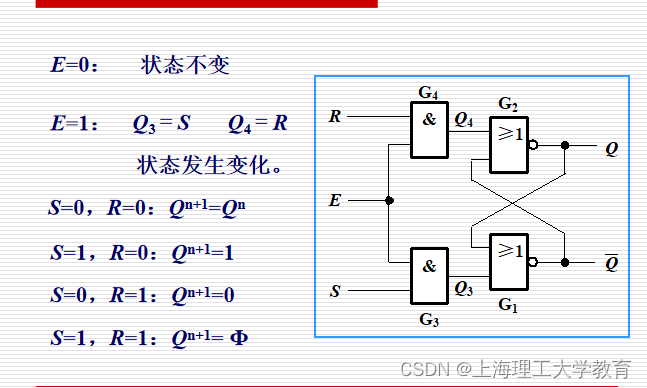

工作原理

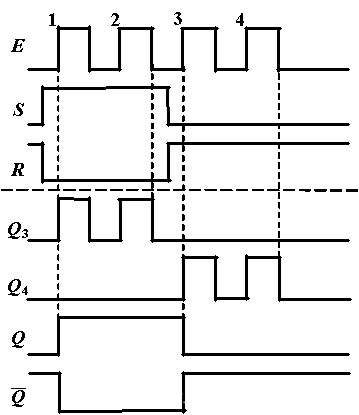

逻辑门控SR锁存器的E、S、R的波形如下图虚线上边所示, 锁存器的原始状态为Q = 0,试画出Q3、Q4、Q和Q的波形

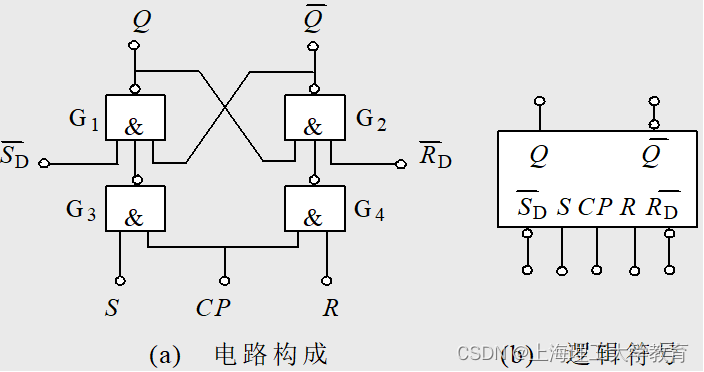

4、逻辑门控SR锁存器其他形式 CP=0时,锁存器保持原来状态不变。

CP=0时,锁存器保持原来状态不变。

CP=1时,工作情况与基本RS锁存器相同。

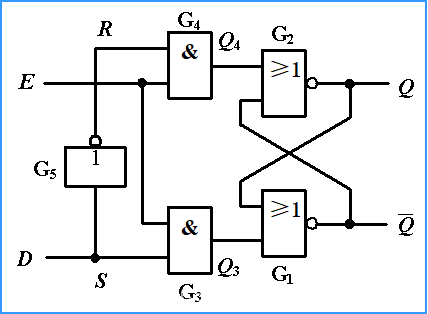

5.2.2 D 锁存器

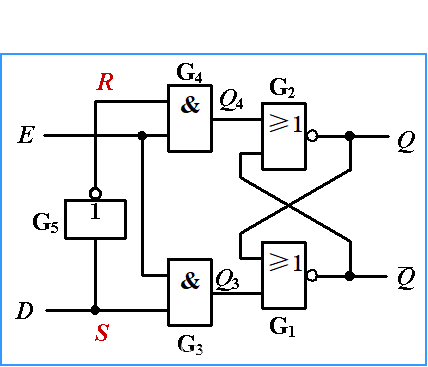

1. 逻辑门控D锁存器

逻辑电路图

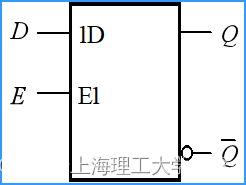

国标逻辑符号

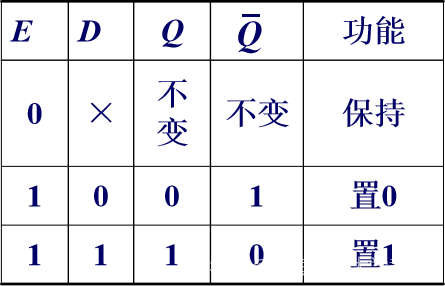

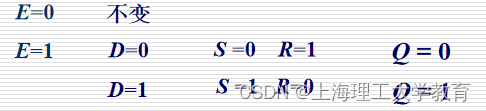

逻辑功能

D锁存器的功能表

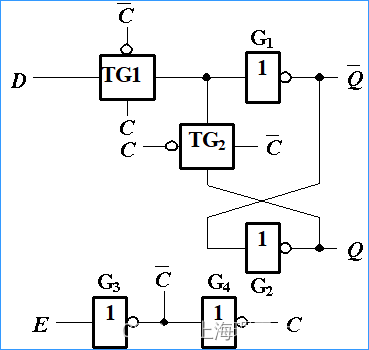

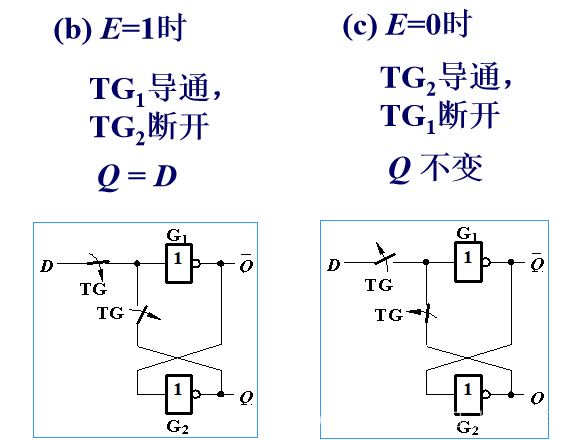

2. 传输门控D锁存器

(a)电路结构

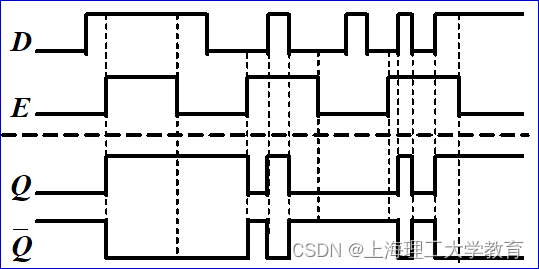

(c)工作波形

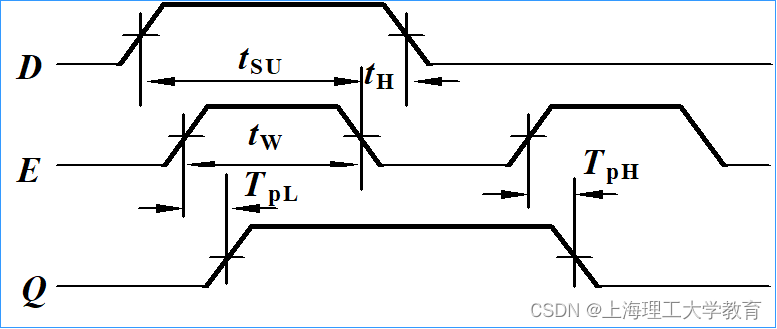

3. D锁存器的动态特性

定时图:表示电路动作过程中,对各输入信号的 时间要求以及输出对输入信号的响应时间。

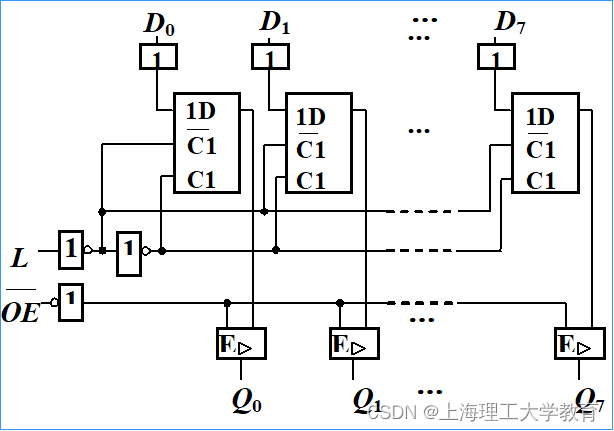

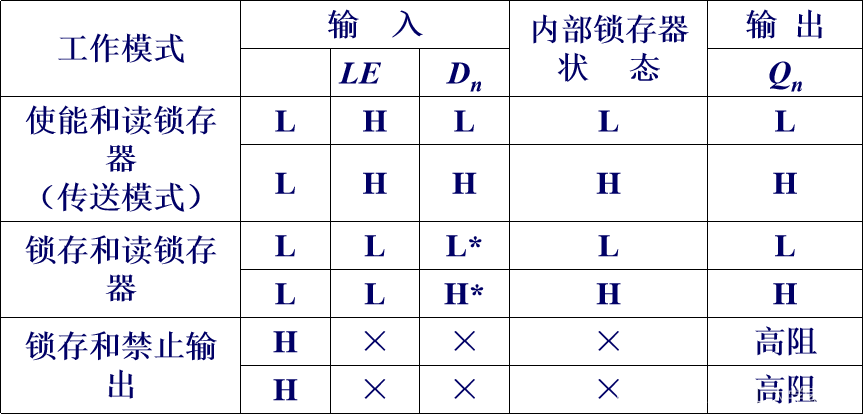

4. 典型集成电路

74HC/HCT373 八D锁存器

L*和H*表示门控电平LE由高变低之前瞬间Dn的逻辑电平。

5.3触发器

触发器的电路结构和工作原理、

5.3.1 主从触发器

5.3.2 维持阻塞触发器

*5.3.3 利用传输延时的触发器

5.3.4 触发器的动态特性

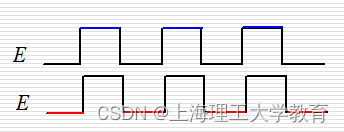

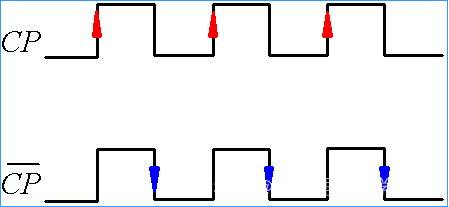

1. 锁存器与触发器

锁存器在E的高(低)电平期间对信号敏感

触发器在CP的上升沿(下降沿)对信号敏感

触发器是能够存储1位二进制码的逻辑电路,它有两个互补输出端,其输出状态不仅与输入有关,而且还与原先的输出状态有关。根据电路结构的不同特点,触发器可以分为主从触发器和边沿触发器。根据逻辑功能的不同,触发器也可分为RS触发器、JK触发器、D触发器、T触发器和T'触发器。

触发器逻辑功能的描述可有以下几种表示方法:状态表(功能表)、特性方程、激励表、状态转换图、工作时序图(时间波形图)以及HDL语言描述。

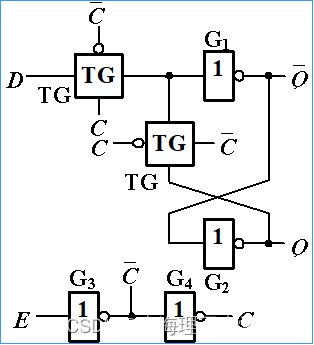

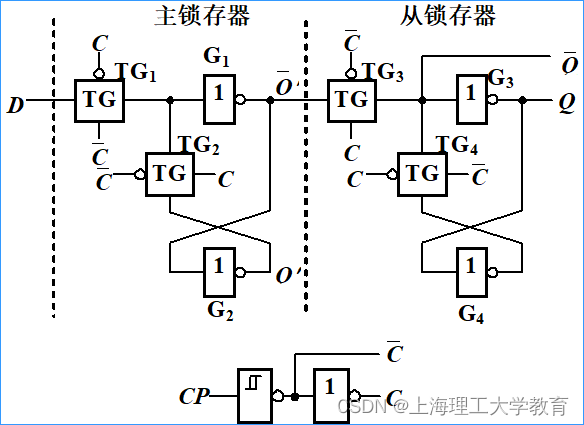

5.3.1 主从触发器

1. 电路结构

主锁存器与从锁存器结构相同  TG1和TG4的工作状态相同 TG2和TG3的工作状态相同

TG1和TG4的工作状态相同 TG2和TG3的工作状态相同

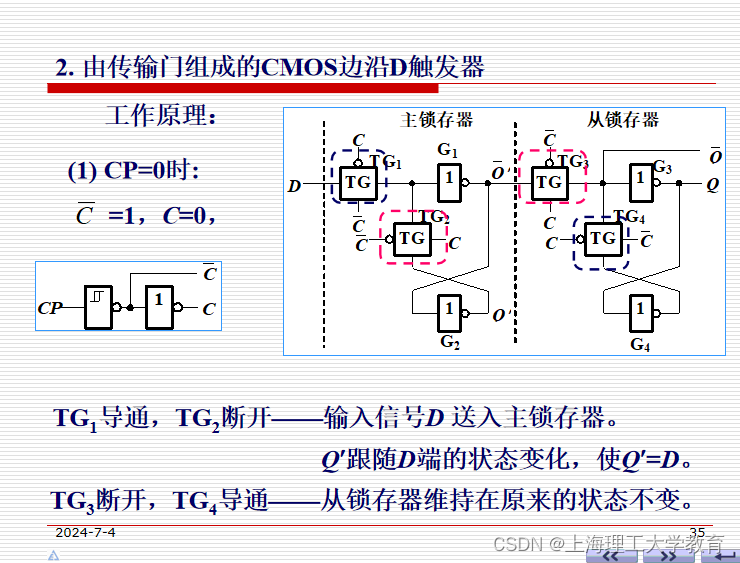

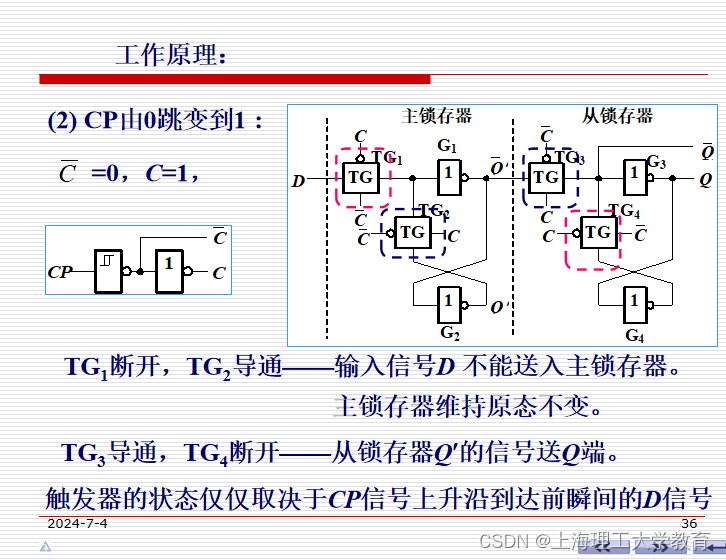

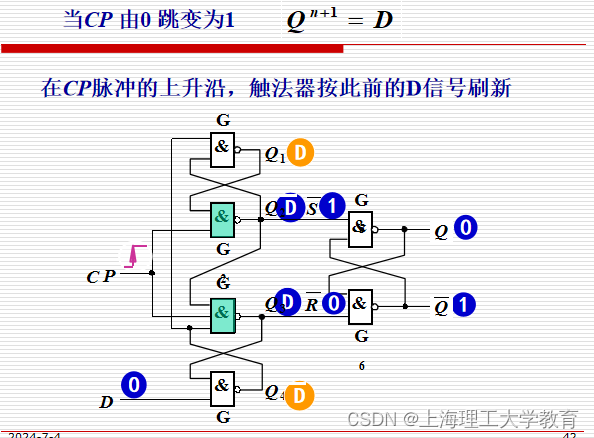

2. 由传输门组成的CMOS边沿D触发器

工作原理:

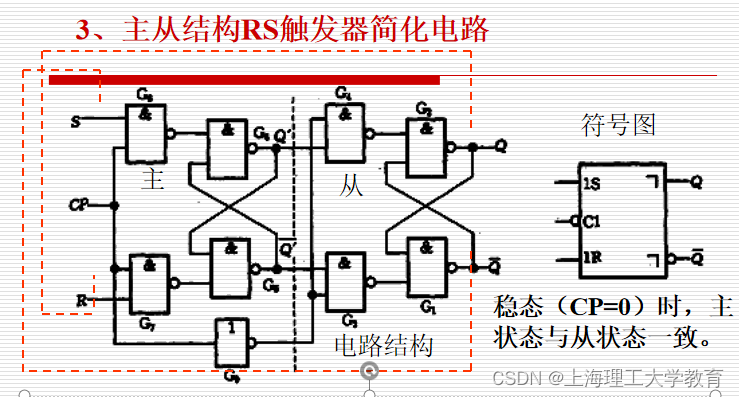

3、主从结构RS触发器简化电路

功能:CP为高时接受信息,输出维持不变:CP从高变低时,刷新输出,同时禁止信号输入。其逻辑功能与同步RS触发器相同。当红线相连时,此电路具有计数功能。

CP触发方式——电平触发

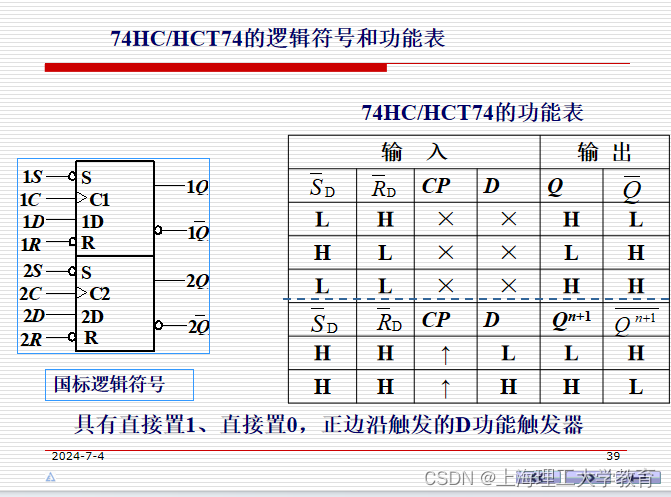

4. 典型集成电路

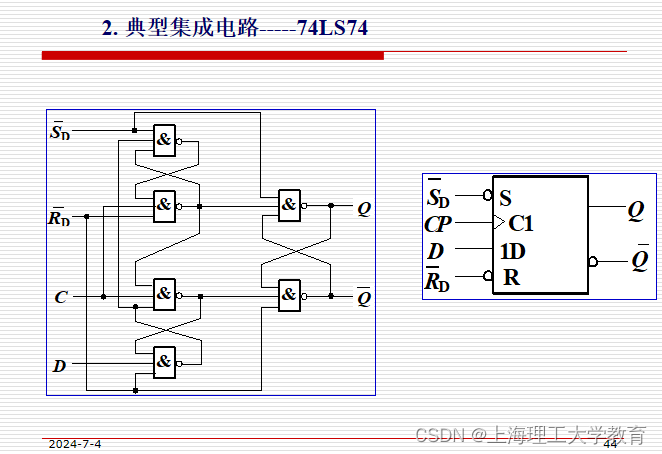

74HC/HCT74 中D触发器的逻辑图

逻辑符号和功能表

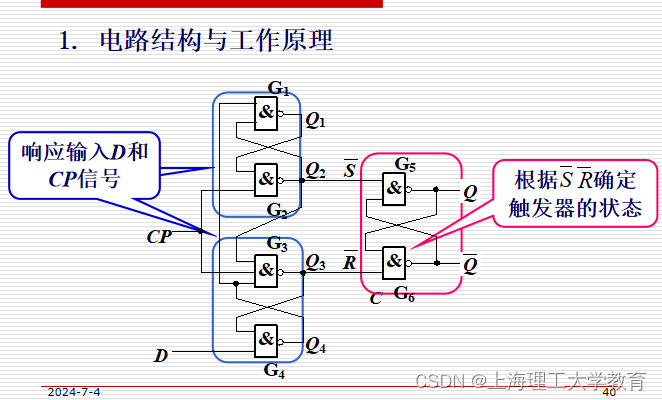

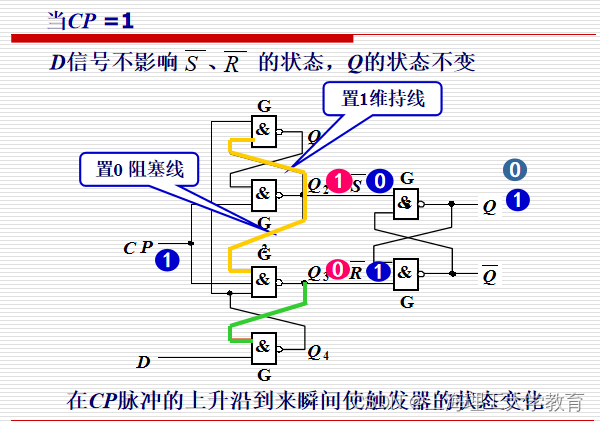

5.3.2 维持阻塞触发器

1电路结构和工作原理

典型集成电路

资料仅供学习使用

如有错误欢迎留言交流

博主的其他专栏:

关注博主了解更多

1361

1361

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?