System Generator从入门到放弃(一)-安装与使用

文章目录

一、安装与使用

1、简介

摘自:百度百科

System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

2、功能介绍

摘自:百度百科

用SystemGenerator进行仿真

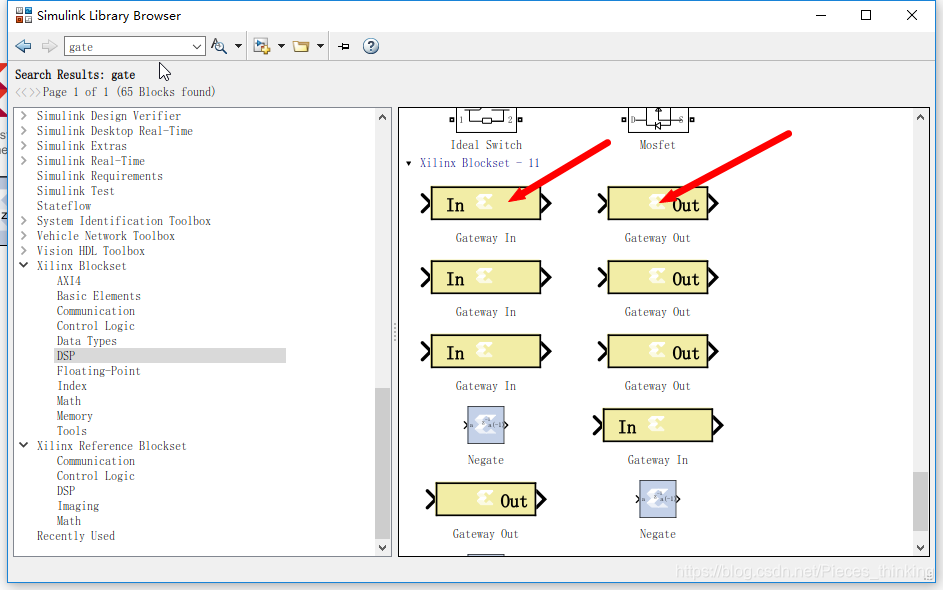

- 1、必须包含的模块:Gateway In、Gateway Out、SystemGenerator、以及Xilinx定点运算单元。

- 2、对于系统设计中有精确时钟限制的外部接口模块,使用System

Generator设计不是最佳方法,此时可以利用HDL等方法实现,然后通过System Generator工具提供的Black

Box导入Sysgen工程中即可。

SystemGenerator Blockset

1、主要包括:Xilinx Blockset、XilinxPreference Blockset 和 Xilinx XtremDSP Kit三个库函数块。

2、XilinxBlockset包含了所有在Simulink中构建数字信号处理系统和其他FPGA数字系统的模块。

3、XilinxPreferenceBlockset 是更高层次的模块,都是由Xilinx Blockset中的模块组成的,降低了开发难度,并且具有较高的可靠性。

信号数据类型

- 1、XilinxBlock的输出格式可以设定为:Fullprecision和User-defined precision Fullprecision:会在运算中自动进行位宽扩展User-definedprecision:对输出结果进行截位(wrap)或饱和(saturate)处理(用户设置)。

- 2、在SystemGenerator中,点击Format –>Port/Signal Displays –> Port Data Type即可显示每个模块输入输出的数据类型。

- 3、当Simulink无法确定数据类型和采样速率时,会报错,通常这种情况出现在有反馈的情况下。这时可以通过添加一个Assert模块对信号进行强制制定或重新定义。且不占用硬件资源。

- 4、GatewayIn可以设定SamplePeriod,值越大,采样点越少。一般来说,对于同一组Gateway In,sample

period应该是一样的,即采样率时一样的。所以当修改一个Gateway In的Sample Period时,记得同时更新同一级的Gateway In的Sample Period。 - 5、采样率变换,利用模块:Up sample和Down

sample。SystemGenerator中不同颜色代表不同的采样率。可以点击Format –> Sample Time Colors

视频介绍

这部分Xilinx官方有相关的视频介绍:

https://www.xilinx.com/video/hardware/hardware-co-simulation-vivado-system-generator-for-dsp.html

3、System Generator安装

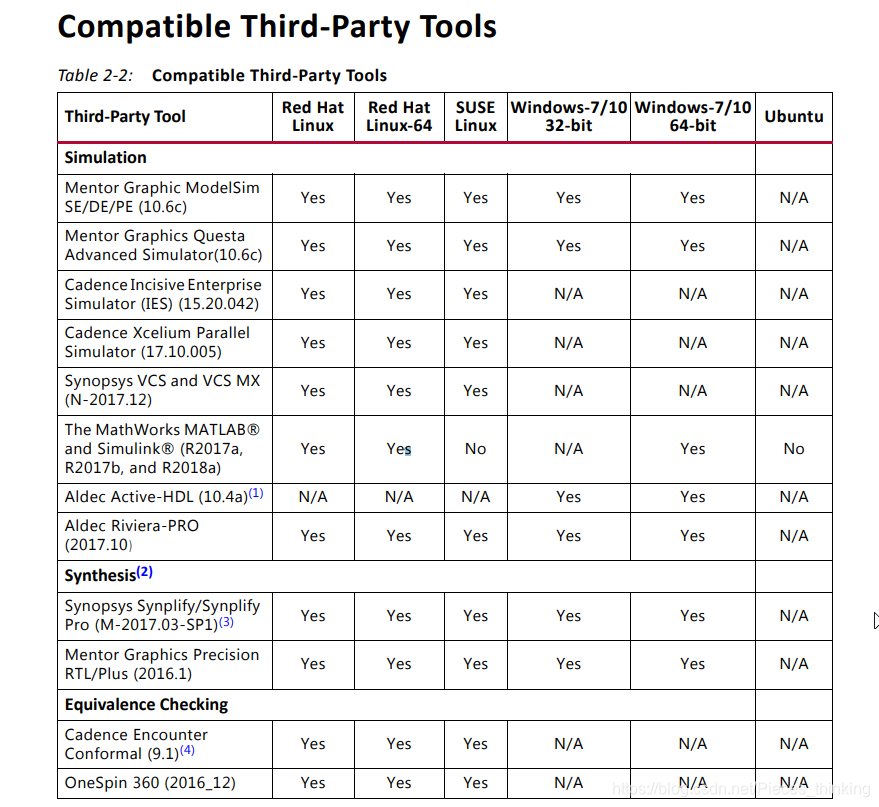

System Generator软件不需要单独安装,在安装Vivado时会有相关的选项,注意勾选就可以了。但是System Generator软件需要同MATLAB一同使用,并且MATLAB版本必须与System Generator版本兼容。版本兼容信息需要在安装MATLAB或者Vivado时进行相关的查询,具体可以在ug973(13/81页,每个版本不同)官方文档中中查询,查询地址:https://www.xilinx.com/support/documentation-navigation/see-all-versions.html?xlnxproducttypes=Design Tools&xlnxdocumentid=UG973

有各个版本的介绍

以2018.2版本为例:

PS:在打开Xilinx官方文档时(pdf),尽量在官网中浏览器中打开,这样PDF中的超链接才可以直接打开,否则有些连接没办法打开

基于上表,相关设计环境如下:

- WIN10 64位

- Vivado 2018.2

- System Generator 2018.2

- MATLAB R2017

在安装Vivado的过程中,会出现配置MATLAB的界面,如果安装时没有配置,可以在“开始->Xilinx Design Tools->System Generator 2018.2 MATLAB Configurator”工具中修改(具体路径可能会不同,右键->更多->打开文件位置->右键->以管理员身份运行):

具体操作详见:https://blog.csdn.net/Pieces_thinking/article/details/80753739

4、System Generator简单入门

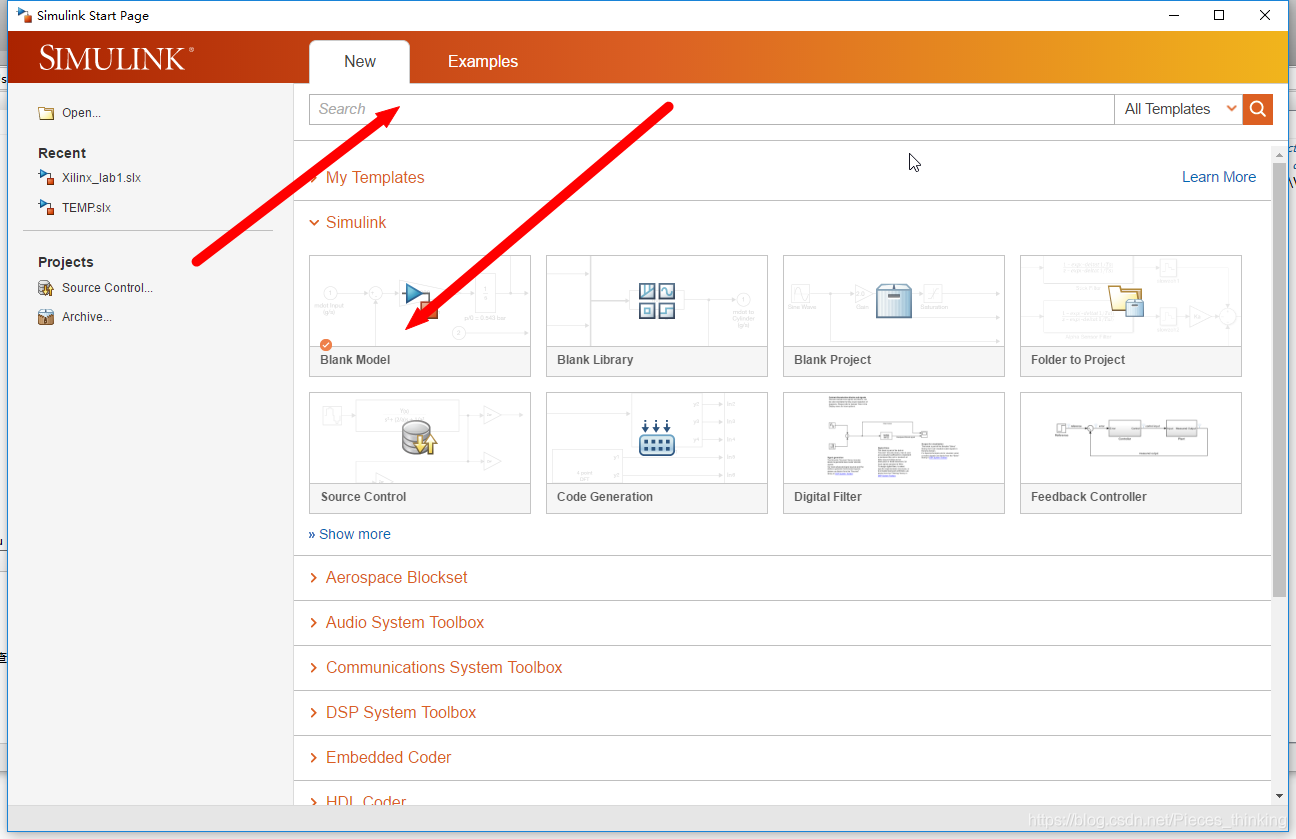

运行System Generator(注意不要直接运行MATLAB,否则无法向Simulink中添加Block),在命令行中输入simulink后回车(或者点击“主页”标签中的Simulink按钮),打开Simulink;

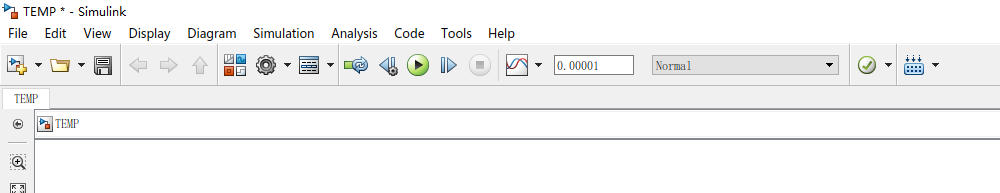

1.点击“Blank Model”创建一个空模型

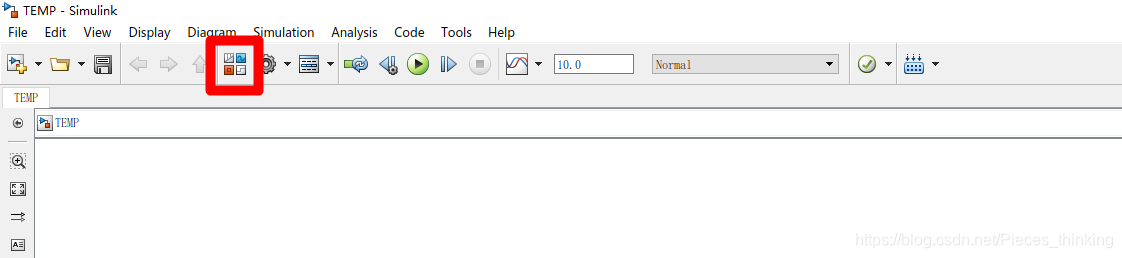

2.点击“Library Browser”打开Simulink库

3.添加block到Simulink

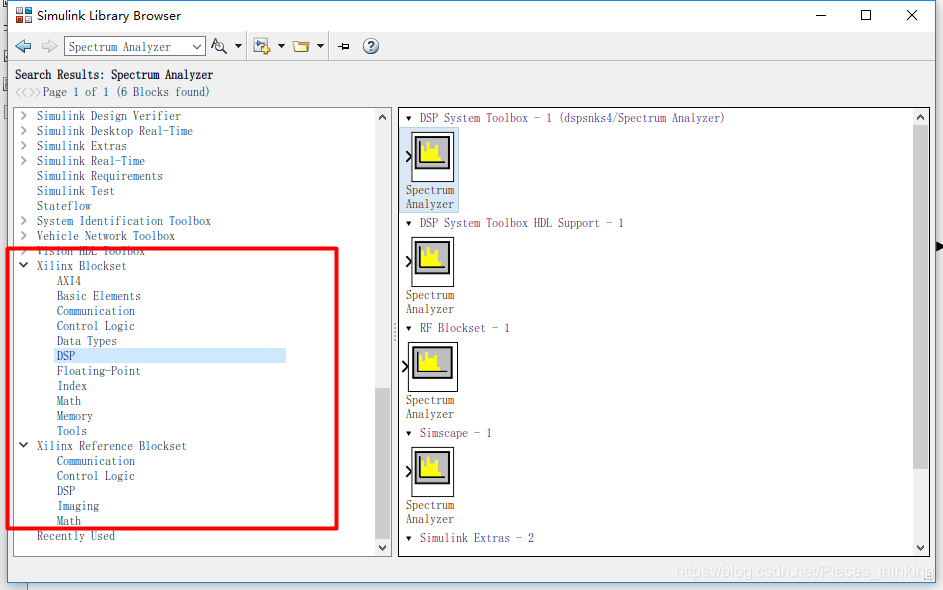

列表中可以找到“Xilinx Blockset”和“Xilinx Reference Blockset”,其中的模块即为System Generator设计时使用的模块。

添加block到Simulink中有两种方法:

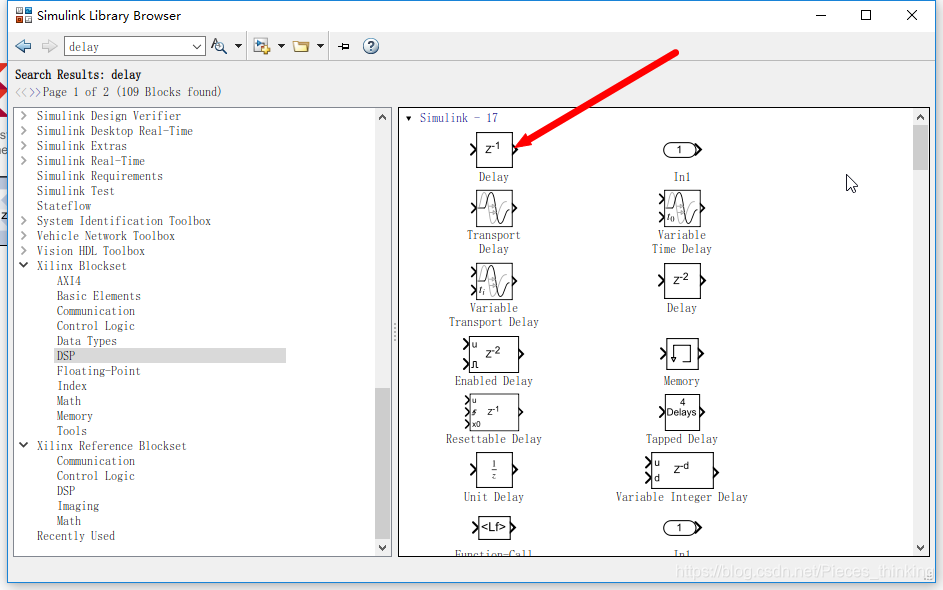

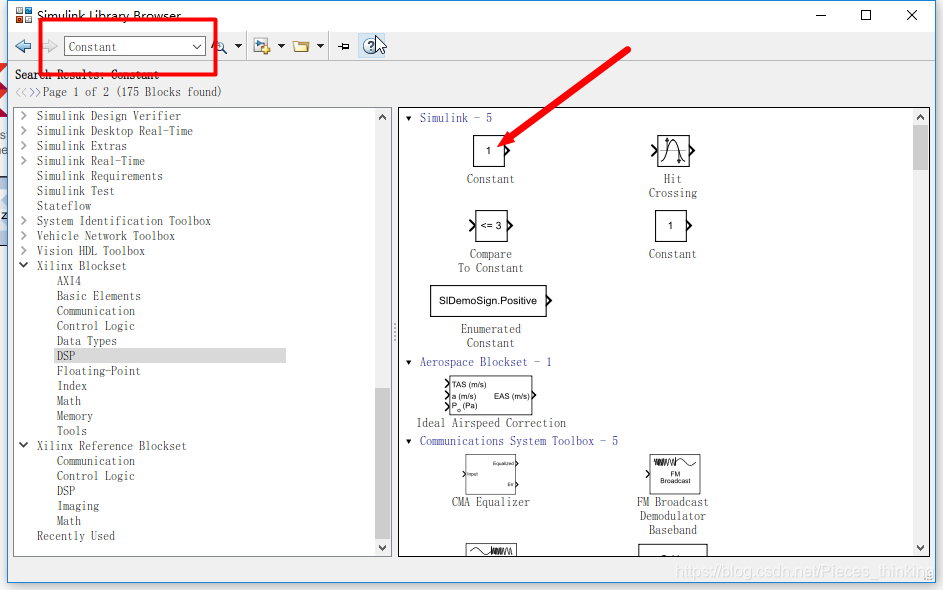

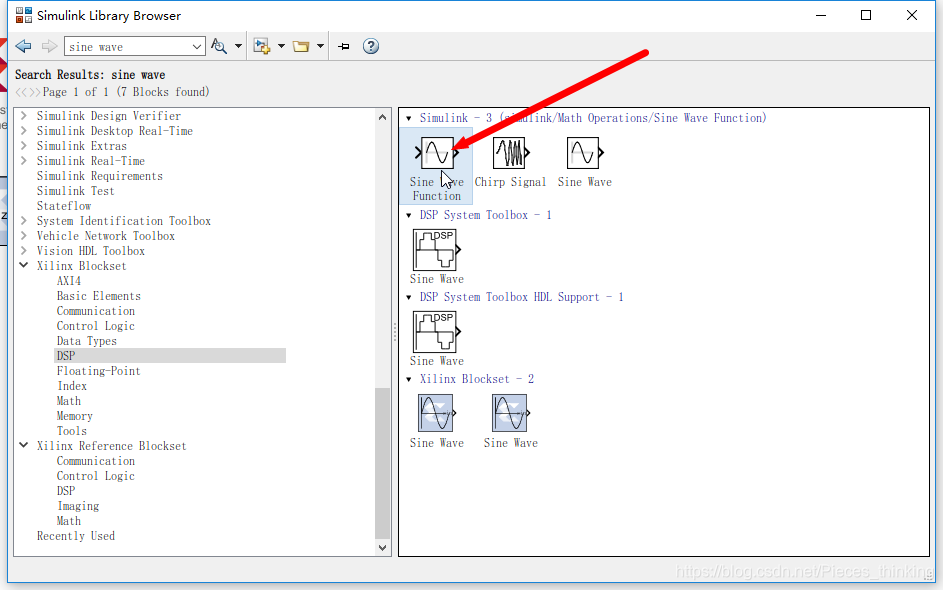

- 像上述一样打开库,在库中搜索,然后按住鼠标拖拽到工作薄上即可;

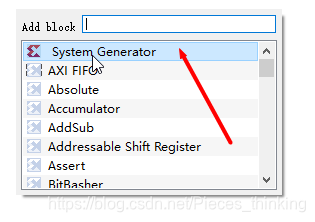

- 在Simulink空白处点右键->Xilinx BlockAdd,在出现的小窗口中搜索,双击可添加到模型中。

第一个方法适合于在库中寻找未知的block;如果已经对某block很熟悉,用第二个方法更方便。

4.简单小实例

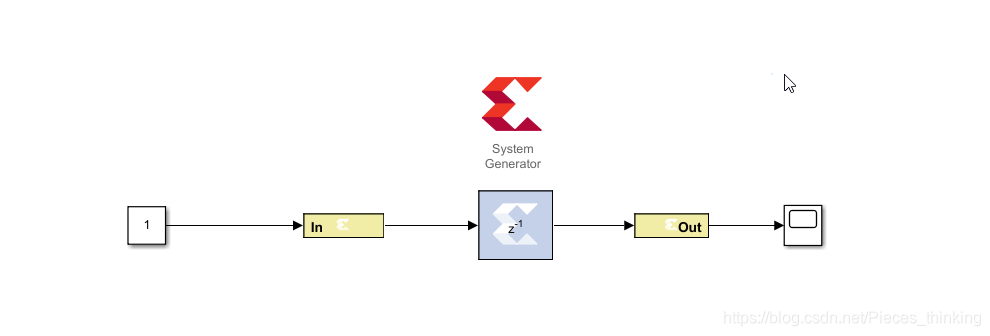

添加System Generator、Gateway In、Gateway Out、Delay、Constant(不是Xilinx Blockset中的那个)、Scope,按下图连接:

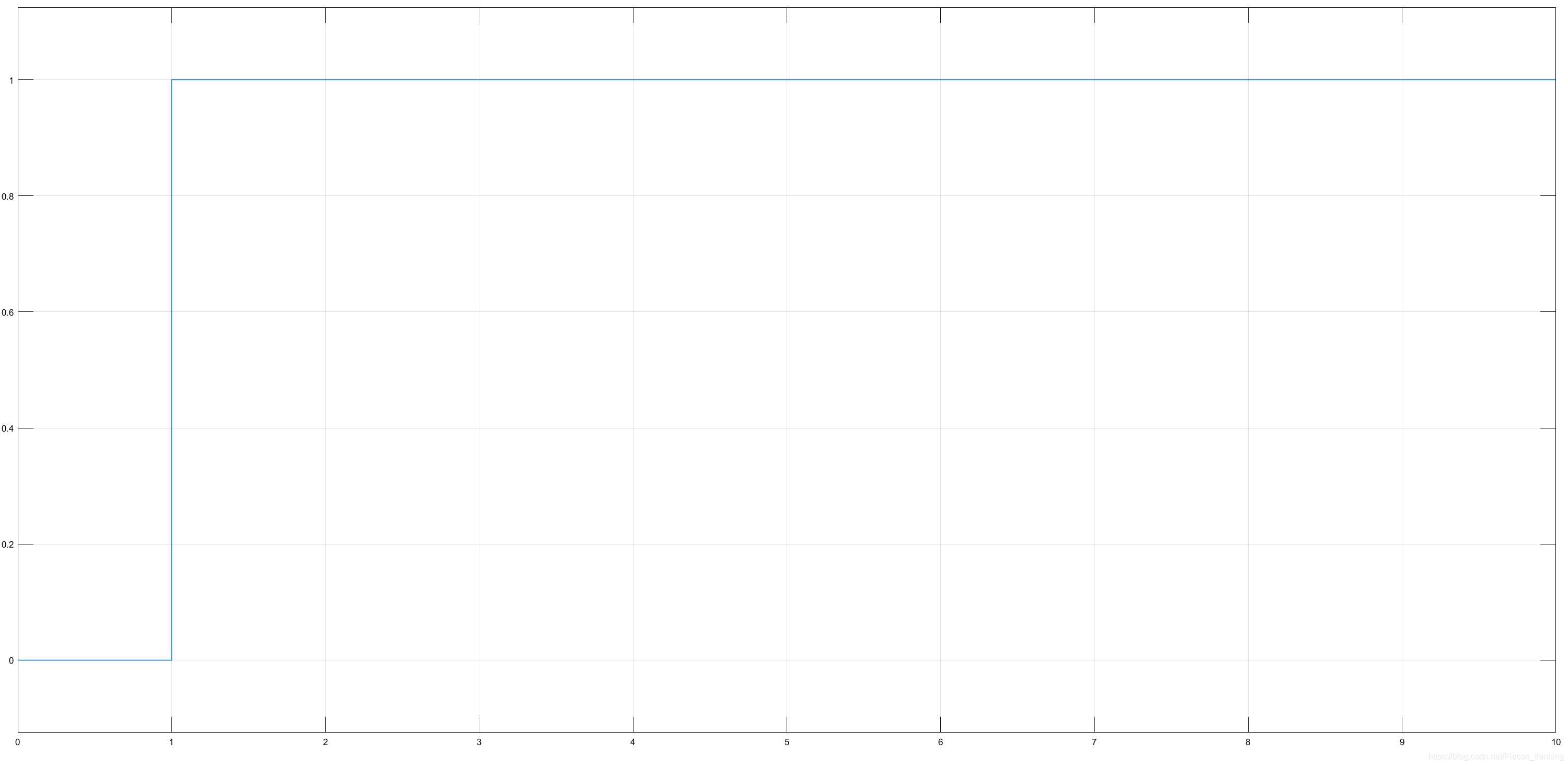

Constant输出一个常数值1,Delay延迟一个采样周期,其它block的具体用法可参考本系列后面文章。直接点击Run运行,打开Scope,结果如下:

看到经过1个单位延迟后,输出保持为1。保存Model,Simulink的模型文件存储为“.slx”格式。本系列后面文章将不再讲述如何新建模型与添加block。

5、System Generator后续学习参考资料

◎ug948:讲述了6个使用System Generator的基本实验,熟悉软件特性。

◎ug958:介绍了System Generator的所有Block相关知识(在Simulink中添加好Block后,右键->help,也可以查阅到相关介绍)。

◎ug897:详细介绍了System Generator的所有功能特性。

◎MATLAB(通过System Generator启动)中输入“xlDoc”可查阅System Generator的帮助文档;输入“demo blockset xilinx”可查阅官方示例。

本系列会将官方的白皮书和相关历程奉献出来。

4461

4461

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?