目录

目录

案例1:【VCS中timescale报错】

最近练习vcs时,发现一个以前没有注意的问题,就是利用vcs编译时,多个模块的摆放顺序会对timescale产生影响。

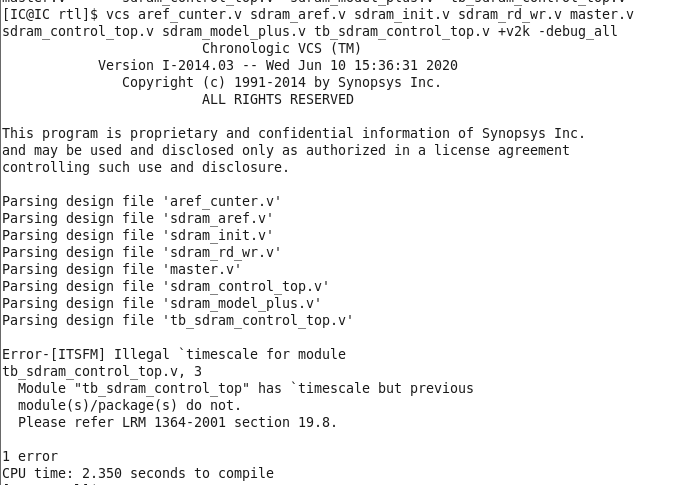

第一张图里面我对多个模块的.v文件进行编译,顺序是aref_cunter.v sdram_aref.v sdram_init.v sdram_rd_wr.v master.v sdram_control_top.v sdram_model_plus.v tb_sdram_control_top.v,timescale 只在tb_sdram_control_top.v文件中写了,其他都没有写,然后发现vcs编译报错,报告的错误为

Module "tb_sdram_control_top" has `timescale but previous

module(s)/package(s) do not.

这表示除了这个模块写了timescale,其他模块都没有写 之后我重新调整了顺序 顺序为tb_sdram_control_top.v aref_cunter.v

订阅专栏 解锁全文

订阅专栏 解锁全文

878

878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?