FPGA- 序列检测器

序列检测器是时序数字电路设计中经典的教学范例。下面我将用Verilog HDL语言来描述、仿真并实现它。

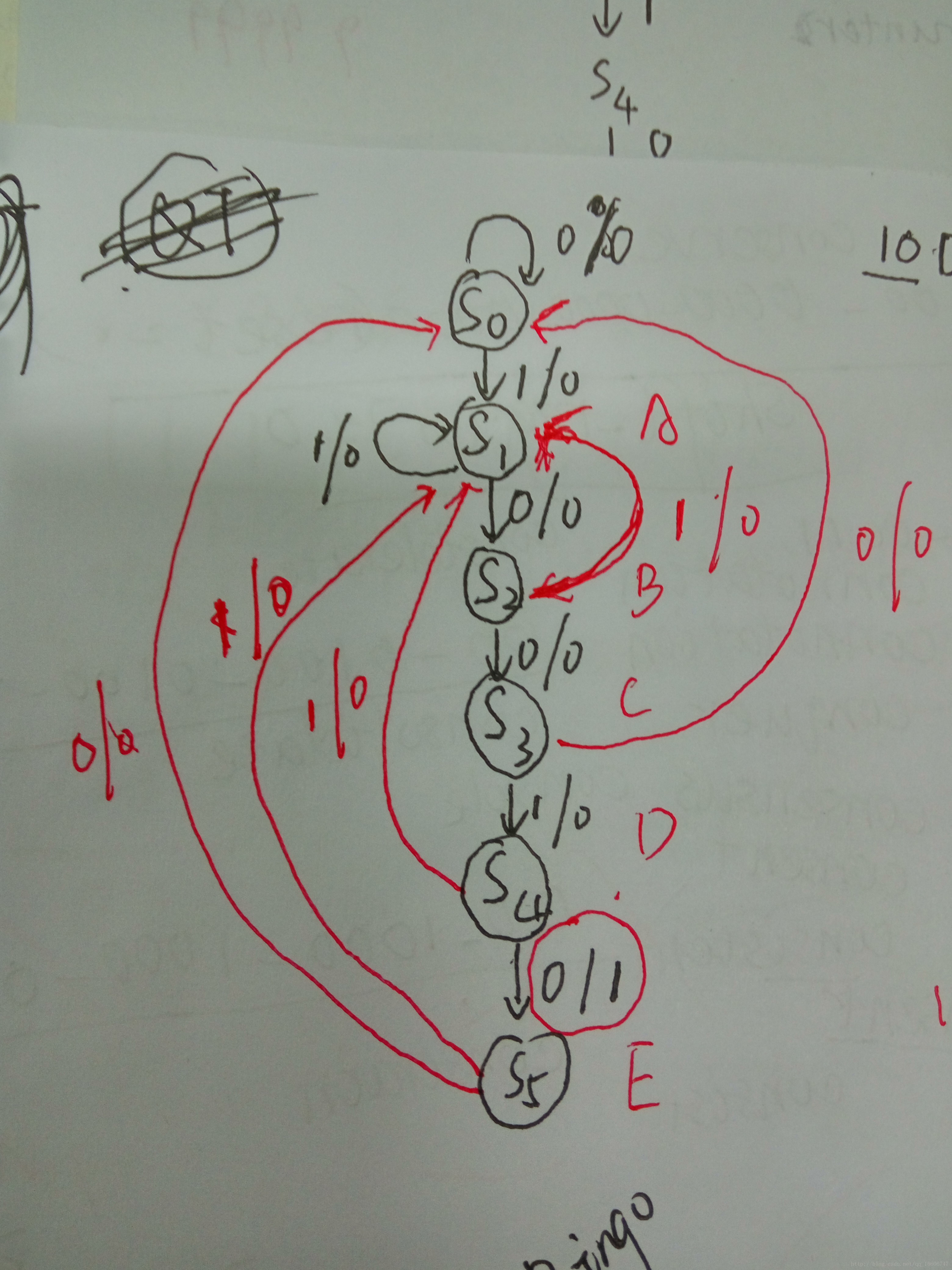

本次设计实现:设计一个“10010”序列的检测器。设x为数字码流输入,z为检测标记输出,高电平表示“发现指定序列”,低电平表示“没有发现指定序列”。本次设计的码流设置为data=20'b1100_1001_0000_1001_0100.其状态转换图如下面的图片。

状态转移图

代码如下:

//本设计为一个“10010”序列的检测器

module seqdet(x,z,clk,rest);

input x;

input clk;

input rest;

output reg z;

parameter s0 = 6'b000_001,

s1 = 6'b000_010,

s2 = 6'b000_100,

s3 = 6'b001_000,

s4 = 6'b010_000,

s5 = 6'b100_000;

reg [5:0] state;

always@(posedge clk or negedge rest)

if(!rest)

begin

state <= s0;

本文介绍了使用FPGA实现一个针对特定序列"10010"的检测器。通过状态转移图和提供的代码,详细阐述了设计过程,并提供了仿真测试及结果展示。

本文介绍了使用FPGA实现一个针对特定序列"10010"的检测器。通过状态转移图和提供的代码,详细阐述了设计过程,并提供了仿真测试及结果展示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1211

1211

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?