DDS的FPGA实现

补充一下相位控制字,下面的相位就是-90°,改变相位就是给ROM的地址取一个偏移量即可。

首先创建工程:

DDS_Module.v

module DDS_Module(

Clk,

Reset,

Fword,

Pword,

Data

);

input Clk;

input Reset;

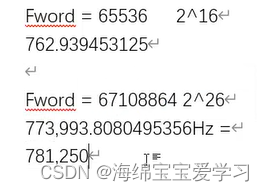

input [31:0]Fword; // 32位 最少需要4G的存储空间

input [11:0]Pword; // 为什么是12位 4096个点

input [13:0]Data; // 使用的14位的DA

// 频率控制字同步寄存器

reg [31:0] Fword_r;

always(posedge Clk)

Fword_r <= Fword;

// 相位控制字同步寄存器

reg [31:0] Pword_r;

always(posedge Clk)

Pword_r <= Pword;

// 相位累加器

reg [31:0] Freq_ACC;

always@(posedge Clk or negedge Reset)

if(!Reset)

Freq_ACC <= 0;

else

Freq_ACC <= Fword_r + Freq_ACC;

// 按照图来看,其实可以看成组合逻辑

// wire [31:0]Freq_ACC_out;

// assign Freq_ACC_out = Freq_ACC + Pword_r;

// 相位累加器与相位控制字的结果输出

reg [31:0] Freq_ACC_out;

always@(posedge Clk or negedge Reset)

if(!Reset)

Freq_ACC_out <= 0;

else

Freq_ACC_out <= Freq_ACC + Pword_r;

// 波形数据表地址 ROM

reg [11:0] Rom_addr;

// assign = Freq_ACC_out;

// Fword = 2'20

// Freq_ACC_out[31:20]

assign Rom_Addr = Freq_ACC_out[31:20];

// 例化ROM

blk.mem_gen_0 rom(

.clka(Clk),

.addra(Rom_Addr),

.douta(Data)

);

endmoudle

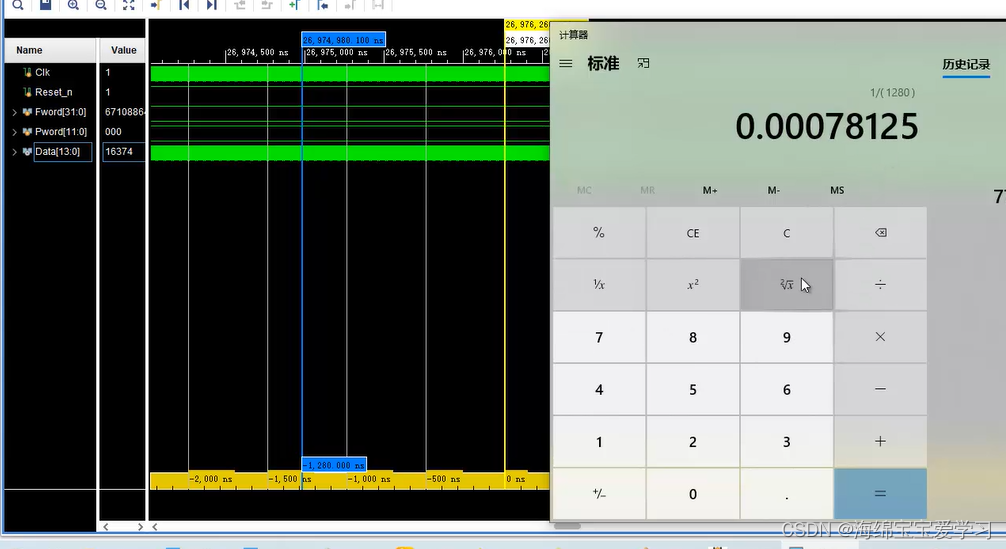

写一个testbench 测试

module DDS_Module_tb;

reg Clk;

reg Reset;

reg [31:0]Fword;

reg [11:0]Pword;

wire [13:0]Data;

DDS_Module DDS_Module(

Clk,

Reset,

Fword,

Pword,

Data

);

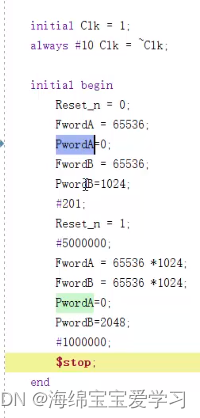

initial Clk = 1;

always #10 Clk = ~Clk;

initial begin

Reset = 0;

Fword = 65536;

Pword = 0;

#201;

Reset = 1;

#20000000;

Fword = 65536 * 1024;

#20000000;

Fword = 65536 * 32;

#20000000;

$stop

end

endmodule

掉进了 vivado 软件的坑!

修改 testbench

1569

1569

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?