调试工具(9种),只介绍常用5种

signal probe

将内部信号快速布线到I/O 管脚 ,同时又不影响设计,从而使设计验证更加有效。当开始于一个完整布线设计时,您可以选择用于调试信号,并将它们布线到之前保留或者当前未使用的I/O 管脚。

1. 执行完整的编译。

2. 保留Signal Probe 管脚。

3. 分配Signal Probe 源。

4. 在流水线路径与Signal Probe 管脚之间添加寄存器。

5. 执行Signal Probe 编译。

6. 分析Signal Probe 编译的结果。

LAI (Logic Analyzer Interface)

Signal Tap

1.power up

2.分段缓存中,采集存储器被均分为多个段(segment),并为每个段定义一组触发条件。每个段都用作一个非分段缓存。分段缓存使您能够对包含相对不经常发生的事件的系统进行调试。

3. 假如我想用A实例触发后再自动触发B实例。允许异步

设置如下:在A实例下面设置trigger out|instan B(注意是B不是A)

正常情况B实例的trigger in 会自动设置好为A

跨时钟抓信号

set_false_path -to {sld_signaltap:*}

Memory Content Editor

要使用这个功能,需要在生成这个mem IP时(ROM或者RAM都可以),勾选一个选项,如下图:

允许使用“In-System Memory Content Edit”更新内容,并设置一个RAM的ID,这个ID是在“In-System Memory Content Edit”中区分不同的RAM时使用的。

如果各位童鞋使用了synplify pro/premier工具综合了同样的工程后,再将上述配置文件加载进FPGA,可能会发现这个功能没了,是的,的确没了,但是有没有办法补救呢,因为synplify的综合速度简直是忒快了,大工程忍不住的要用他来综合,办法还真有,使用“/* synthesis syn_black_box */“这个综合命令对这个RAM模块做一些设置

module ram(

)/* synthesis syn_black_box */;

endmodule

quartus II工具In-System Memory Content Editor使用方法_Pilgrim2017的博客-CSDN博客

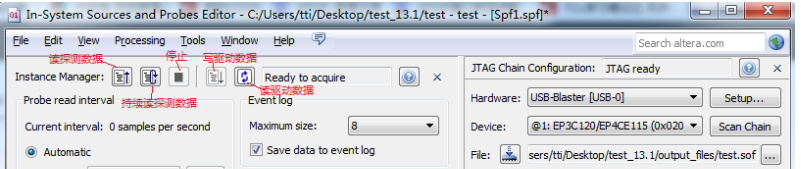

Sources and Probes

类似vio

先例化编译再用

598

598

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?