目录

知识整理,持续更新,如有错漏,欢迎讨论。

知识点多来自B站,唐老师讲电赛,寒武纪魔道电子。

一,BUCK降压电路

1.1 布局与布线

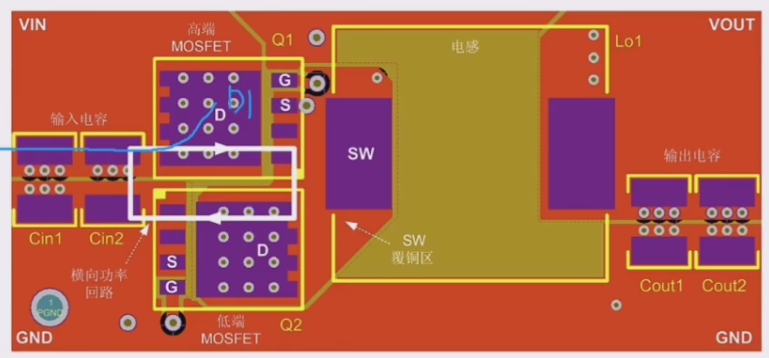

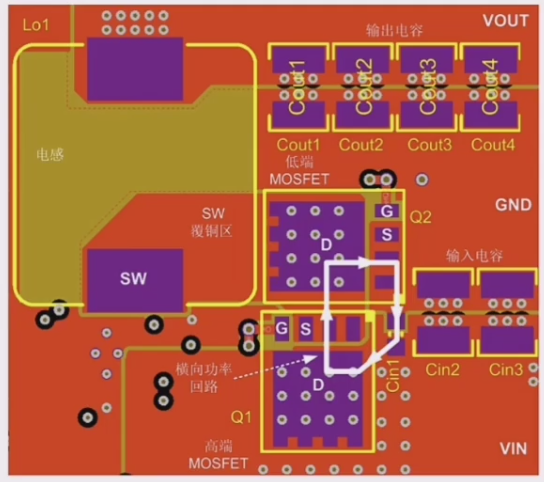

1.1.1 高频电流环路

高频电流环路的面积越小越好。

主要包括“输入电容C1,外接MOS管Q1,反向开关管或二极管Q2”。

注意:电感和输出电容不属于高频电流环路。

元器件布局基本可以分为两种:I型和U型。(可通过Vin和Vout判断)

- I型布局

- U型布局

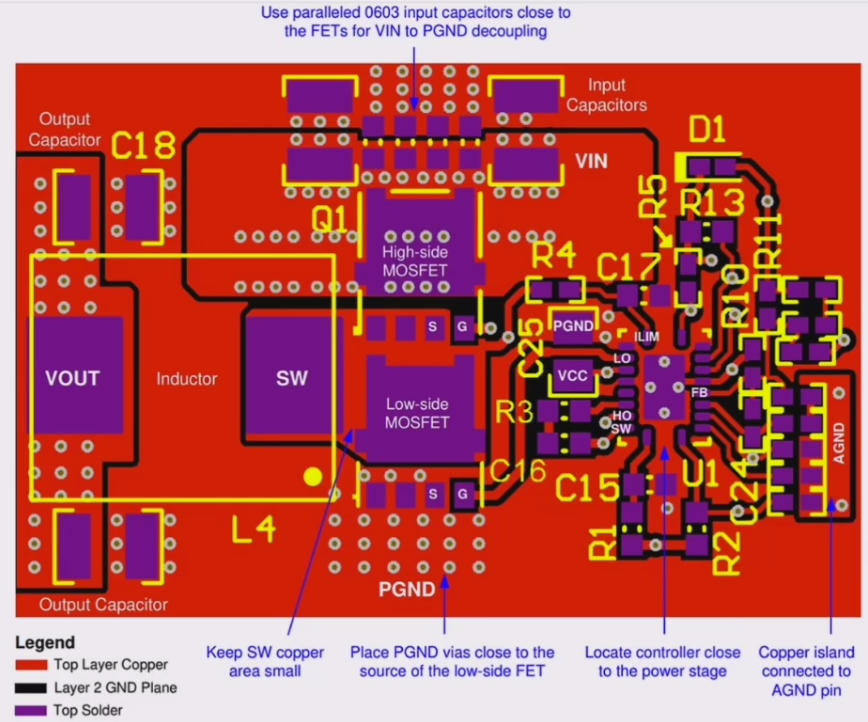

1.1.2 小信号的地

小信号的地连一起(FB分压电阻,COMP,SS)然后再与PGND单点相连,或者通过过孔连到背面。

电源AGND放正面,其他地就是AGND(背面覆铜,小信号的地)。

1.1.3 其他要注意的地方

- 与FB相连的两个电阻越靠近FB引脚越好,FB覆盖面积越小越好。走线细而短。

- 电感两个引脚间距离尽可能大一些,非一体成型电感最好把GND挖空,一挖到底。还要让敏感电路和回路远离电感。特别是Vout到FB的走线,特别要避开电感,二极管,特别是不能和电感平行。

1.2 输入输出电容,电感的选择

1.2.1 电感的选择

对于大多数应用,选择DC电流额定值比其最大负载电流值高出至少25%的电感器。

选择直流电阻小于200mR的电感器以获得最佳效率。

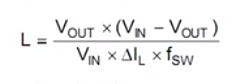

对于大多数设计而言,电感值可以根据以下公式导出:

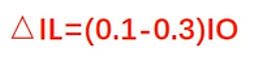

(detaIL是电感纹波电流,下面红色计算公式,fsw是开关频率)

小知识:可以看出,开关频率越大,电感值越小。

当然,也不能太高,开关损耗也高。

轻载时(负载小于100mA),使用较大电感值的电感以提高效率。

选择电感纹波电流大约为最大负载电流30%的电感器。最大电感峰值电流为:

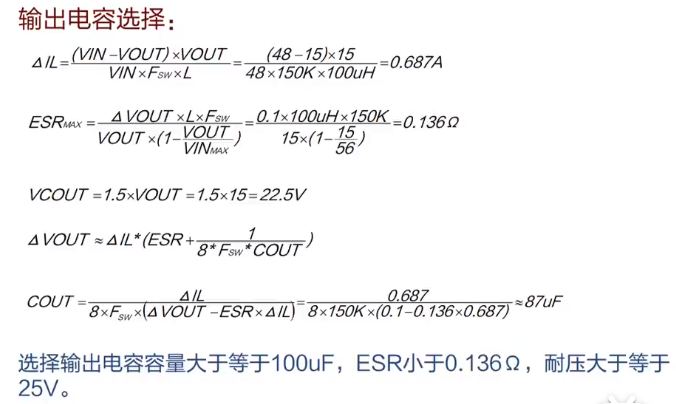

1.2.2 输入输出电容的选择

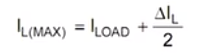

输入电容计算:设输入电压8-30V,输出电流3A,输出电压5V,开关频率180KHz,可得出Cin为52.08uF。

选择100uF的电容或220uF,越大越好。耐压是Vin的1.5倍。

detaVin是输入电压纹波,一般可以取0.2~0.4V。

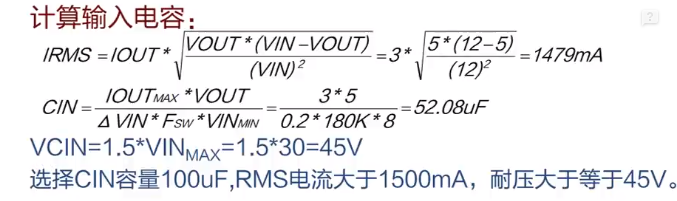

输出电容公式:

Cout大于等于C4的1.5倍。

detaVout是输出电压纹波。

注意:

- 输入电容用MLCC电容(陶瓷电容)比较好,ESR比较小,但是虚标非常严重。

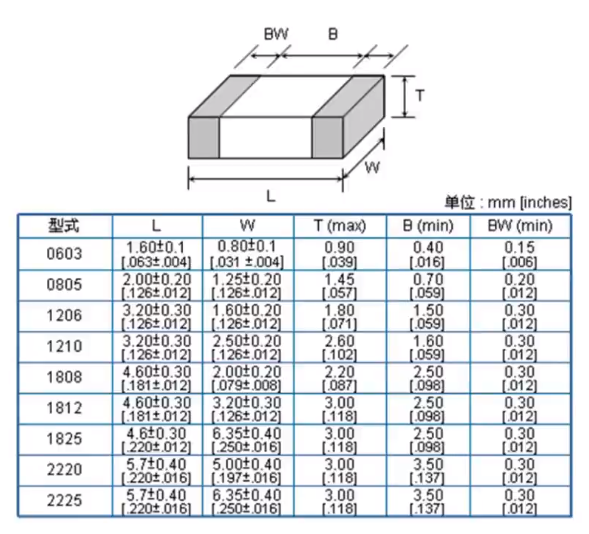

- 相同耐压,相同电容量,施加相同的直流电压,封装越大,衰减越小。

- 输出电容一般比输入电容还要大。

- 输出电容不够时,当Io较大时,会有比较严重的压降,电压会上蹿下跳(纹波过大),会发热,电容和电感会啸叫。

- 输出电容尽量不要用普通的铝电解电容,输入电容可以用。

- MLCC电容(陶瓷电容)耐压1.5倍以上就行,聚合物钽电解电容耐压1.5倍以上就行,普通钽电容至少3倍。

三,电源芯片

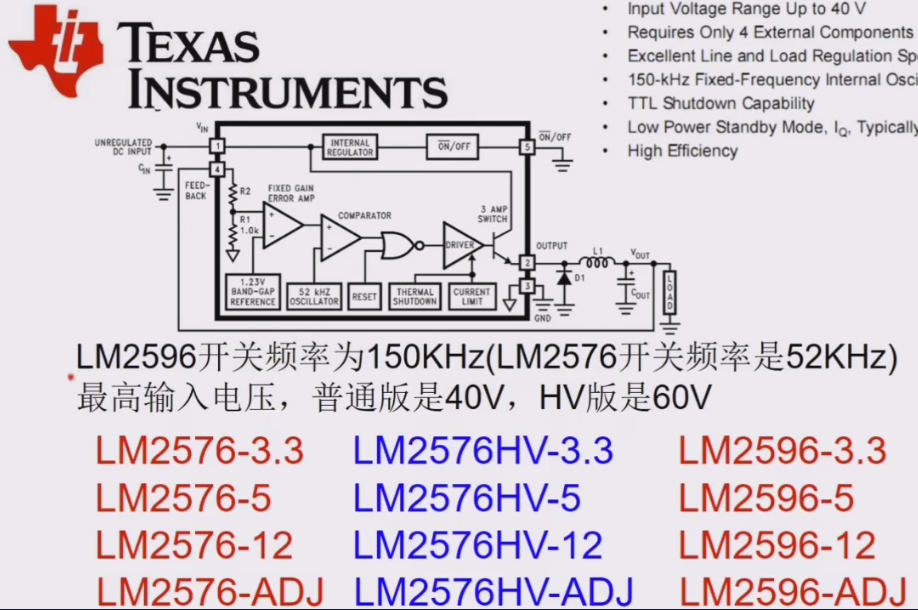

3.1 LM2596,LM2576

LM2596,LM2576基本是一样的,区别是开关频率不一样(频率越快,电感可以越小)

四,运放电路设计

4.1 运放的供电,去耦和PCB

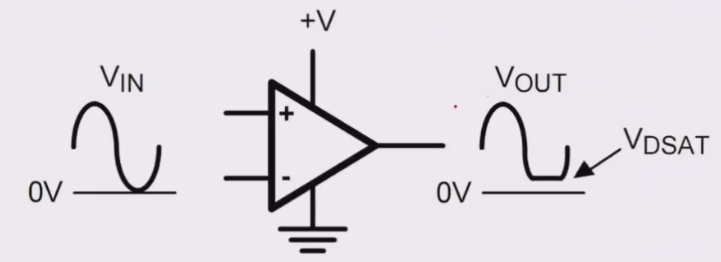

所有的运放都可以用单电源供电,没有例外。

所有的运放又都可以用双电源供电,没有例外。

4.1.1 供电

有些运放供电电压可能高达+600V。而有些运放的供电电压可能最高只能是±3V。使用运放前一定要仔细阅读该运放的官方datasheet。

双电源供电的运放,正负电源尽量同时加入,否则容易损坏运放。且不要带电接线、拔线或改线等。

单电源供电的两个缺点:

1.输出小信号时误差较大,输出电压越小,误差越大。

2.能处理的频率较低≤100kHz

单电源供电,且输入信号很小时,会导致信号放大不正确,误差极大,微弱信号检测时最好的方法是双电源供电。

4.1.2 去耦

电容:

选择电容,运放处理的信号小于等于10MHz,用100nF。10MHz到几十MHz,用10nF。

100多MHz到几百MHz用1uF,几百MHz到几G用100pF。

宽带宽的放大器,要多个电容并联。

- 大的去耦电容(库电容)远离芯片。

- 小的去耦电容(去耦电容或者叫旁路电容)靠近芯片。

- 让去耦电容器尽量靠近电源引脚。

- 如果使用了多个去耦电容器,将最小的去耦电容器放在离电源引脚最近的位置。

- V+和V-间接电容滤波,可减少偶数次高次谐波

注意的地方总结:

- 缩短反向输入端引脚的连接(走线)。

- 去耦电容靠近电源引脚。

- 不要将导孔(即过孔via)置于去耦电容和电源引脚之间。

- 尽可能扩宽走线路径,不要让走线路径上出现90度的角。

- 灌流至少一个坚实的接地层(上拉电阻是用来解决总线驱动能力不足时提供电流的,一般说法是拉电流。下拉电阻是用来吸收电流的,也就是灌电流)。

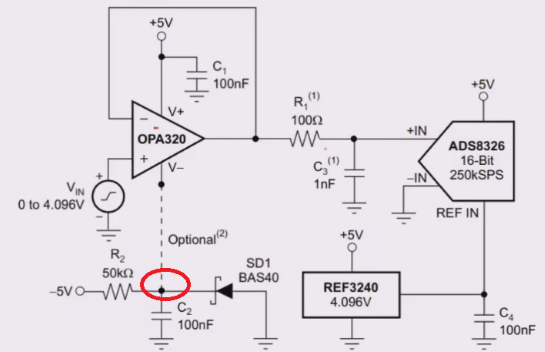

4.1.3 如何给运放提供,比如+5V和-0.3V的电压

在负极引脚接一个肖特基二极管,这个BAS40导通压降0.3V。

4. 5 运放不稳定和自激振荡

自激振荡:输入信号为0时,输出有一定幅值、一定频率的信号,称电路产生了自激振荡。

运放反相输入端与GND之间的寄生电容是运放不稳定和自激振荡的最主要的因素。

运放输出端与GND之间的寄生电容是运放不稳定和自激振荡第二的因素。

- 反相输入端覆盖面积越小越好,反向输入端与GND覆铜之间的距离稍微大一点,将反向输入端附近的电源层和地层挖空(一挖到底,从顶层挖到底层)形成净空区:禁飞区、禁布线。

- 将输出端附近的电源层和地层挖空(一挖到底,从顶层挖到底层)或者在输出端接一个电阻,电阻左边有事,右边没关系。

- 使用输出串联电阻,增加反馈系数β上的零点,减小寄生电容带来的极点的影响。

- 尽可能使得连线缩短,特别是串联匹配电阻尽量靠近输出端。

- 增加噪声增益

- 使用反馈补偿电容

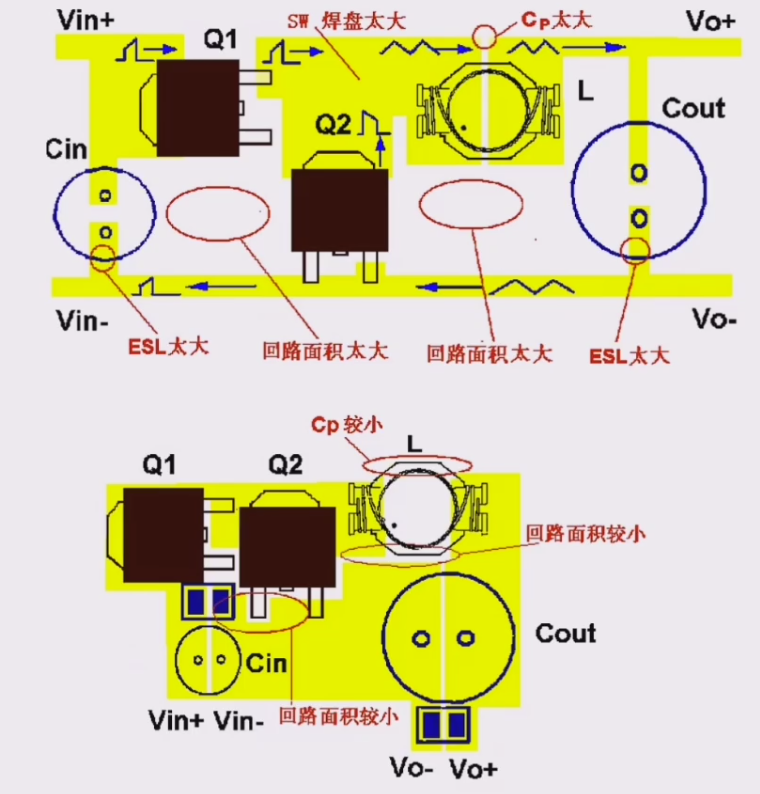

附录一:Buck电路布板错误示例(电感焊盘,电容焊盘,回路面积):

附录二:陶瓷电容不同规格尺寸图

836

836

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?