目录

4. 暂存器转移层次(Register-Transfer Level, RTL)

前面一篇文章,我们说到了电路描述语言verilog HDL,也就是通过编写代码的方法,让EDA工具来编译我们写的代码后生成了对应的电路。

细心的你应该发现了在小编的 “什么是verilog” 这篇文章里面在设计一个module的时候,只做了输入和输出,没有对中间的module实体进行设计编写代码,在这一章节中,小编将带大家认识一下module的设计方法有哪些。

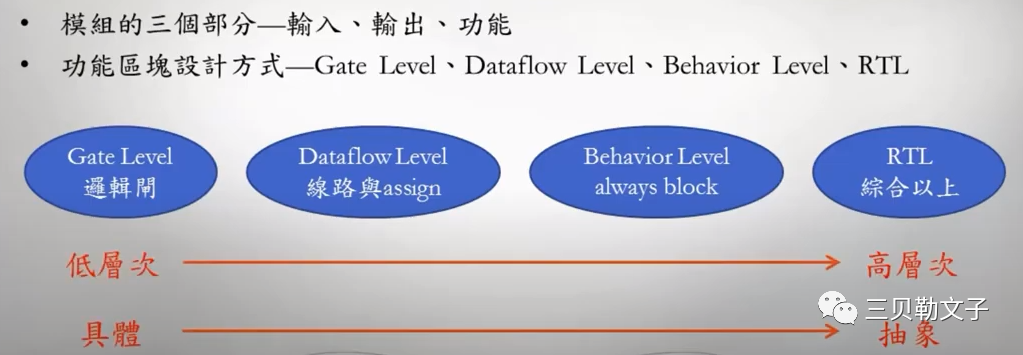

算了,我也不卖关子了,常见的电路设计方法有四种,分别是:逻辑闸层次(Gate Level)、资料流层次(Dataflow Level)、行为层次(Behavior Level)、暂存器转移层次(Register-Transfer Level, RTL)。

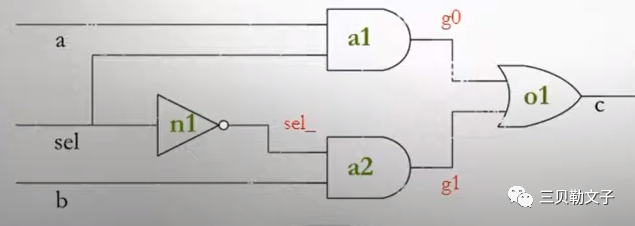

以MUX2to1为例子,在module中的电路长下面这个样子:

1. 逻辑闸层次(Gate Level)

(1) 设计的格式:

// 电线定义:wire 电线1, 电线2,...;

// 定义逻辑闸:逻辑闸类型 逻辑闸名称 (输出, 输入1, 输入2,...)(2)以MUX2to1为例子:

module MUX2to1(a,b,sel,c);

input a,b,sel;

output c;

wire sel_, go, g1;

not n1(sel_, sel);

and a1(g0, sel, a);

and a2(g1, sel_, b);

or o1(c, g0, g1);

endmodule2. 资料流层次(Dataflow Level)

(1) 设计的格式:

// 电线定义:wire 电线1, 电线2,...;

// 电线赋值:assign 电线名称 = 运算式;(2)以MUX2to1为例子:

module MUX2to1(a,b,sel,c);

input a, b, sel;

output c;

wire g0, g1;

assign g0 = a & sel;

assign g1 = ~sel & b;

assign c = g0 | g1;

endmodule3. 行为层次(Behavior Level)

(1) 设计的格式:

// 暂存器定义:reg 暂存器名称1, 暂存器名称2, ...; 宣告

// 使用always block:always@(名称1 or 名称2, ...)

// alwanys@(*)

// 行为描述:A = B & C

// if,,,else

// case

always@(*)

begin

statement1;

statement2;

if (a) begin

statement3;

statement4;

end

else

statement5;

end(2)以MUX2to1为例子:

module MUX2to1(a,b,sel,c);

input a, b, sel;

output c;

reg c;

always@(a or b or sel) // 要变化的变量都需要在这里进行宣告

begin

if(sel)

c = a;

else

c = b;

end

endmodule4. 暂存器转移层次(Register-Transfer Level, RTL)

综合上面三种设计层次的方式,混合使用。

5. 总结

7万+

7万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?