一、 亚稳态

在数字电路中,触发器是一种很常用的器件。对于任意一个触发器,都由其参数库文件规定了能正常使用的“建立时间”(Setup time)和“保持时间”(Hold time )两个参数。“建立时间”是指在时钟沿到来之前,触发器输入信号必须保持稳定的时间。“保持时间”则是指在时钟沿之后,信号必须保持稳定的时间。这些指标通常比较保守,以应对电源电压、工作温度、信号质量以及制

造工艺等各种可能的差异。

异步时序电路中有多个独立的时钟源,不同时钟源存在频率和相位的差异,当数据信号通过两个时钟域的交界处时,将会分别由这两个时钟来控制信号的值。此时如果两时钟信号的敏感沿非常接近并超过了允许的额度,则将出现数据信号的不稳定,即电路陷入亚稳态,也称为同步失败 。如图 1 (a )所示。因为触发器内部数据的形成需要一定的时间,如果不满足建立和保持时间,触发器将进入亚稳 ,其输出在经过一段时间的不确定状态后才能随机地稳定到0 或1 。这个不可预知的状态就是亚稳态,亚稳态的形成过程如图1 ( b )所示。而且这种亚稳态可能向后传播,造成后级出现逻辑错误。通常触发器进入瞬时亚稳态,也会马上重新进入稳态,但此时输出值往往是不确定的,如输入端为数字信号,输出端为错误的数据,如输入端是时序信号,输出

端可能是错误的时序逻辑 ,这是时序逻辑设计中必须避免的。

二、 同步器的设计和分析

在实际中,常用的是采用两级触发器串联的同步器(如图2(a ))。这种用两级触发器串联的同步器亦称为电平同步器(The Level Synchronizer ),它是其他同步器的基础。两级触发器的原理是降低出现亚稳态的概率,使其很小。由上述分析可以看出,来自前一个时钟域的信号到达下一个时钟域的第 1个触发器时,很可能出现不满足建立/保持时间的情况,而导致触发器的输出端 Q 长时间处在亚稳态状态。如果这种状态持续不到一个周期,可以通过增加一级触发器来消除该亚稳态,使第 2 级触发器的输出端满足同步信号的要求,达到异步电路同步化的效果 。图 2 (b )描述了由两级触发器构成的同步器对亚稳态的抑制过程。

对于电平同步器,它能将原时钟域的输出电平信号(保险起见,电平信号应保持大于两个同步时钟周期),转换成目标时钟域的同步输入电平信号 。虽然两级触发器能有效抑制亚稳态,但增加一级 D 触发器就增加了对输入信号的一级延时。因此,对于高速率数字电路的同步器,通常采取的策略是用触发器级联来实现时间缓冲,为电路从亚稳态下恢复过来提供时间,即以时间延迟为代价,降低亚稳态的发生对电路的影响。

两级触发器法在两个异步时钟频率相差不大的情况下比较适合。在信号从快时钟域向慢时钟域过渡时,如果信号变化太快,慢时钟将可能无法对该信号进行正确的采样,导致采样失败。使用两级触发器法时,应使原时钟域的信号保持足够长的时间,以便另一个时钟域的触发器可以正确地对其采样。电平同步器的最大优点就是结构简单,同时,缺点也十分明显,当目的时钟域频率小于源时钟域频率的 2 倍时,它就不能很好地工作 。基于这个原因,本文提出了4种对两个异步时钟频率大小关系没有要求的同步器。

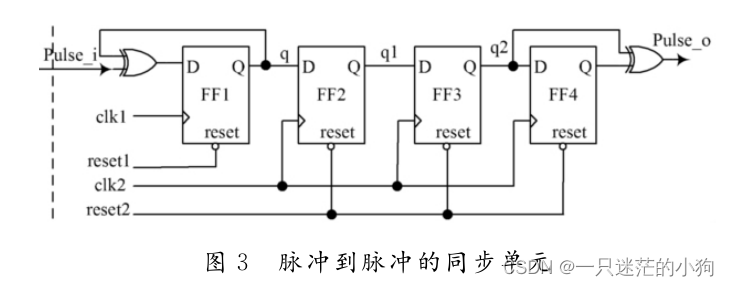

2.1 脉冲到脉冲的同步

在实际的应用当中,当需要将原时钟域的一个脉冲信号同步到目标时钟域的脉冲信号时,往往会使用这种脉冲到脉冲的同步方式。图3代表该电路的具体电路结构。clk1 代表原时钟域的时钟信号,clk2代表目的时钟域的时钟信号。这个同步电路实现的是把一个时钟域的脉冲信号同步到另一个时钟域,在目标时钟域产生一个脉冲。并且对源时钟域的时钟频率和目标时钟域的频率大小关系没有要求。

输入信号来自原时钟域,是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路。每当翻转电路接收到一个脉冲时,它就会在高、低电平间进行转换,然后通过电平同步器到达异或门的一个输入端,而另一个信号经一个时钟周期的延迟进入异或门的另一端,翻转电路每转换一次状态,这个同步器的输出端就产生一个单时钟宽度的脉冲。如此这样,就实现了不同时钟域内的脉冲

信号的同步。

这种脉冲同步器虽然对时钟频率没有要求,但是对两个脉冲之间的间隔是有要求的,如果前后两个脉冲间隔太小,同步以后的脉冲不能分辨这是两个脉冲,会导致最后的同步输出把两个脉冲连在一起输出。甚至当脉冲间隔小于目标时钟域的时钟周期时,则同步器就不能检测到每个脉冲。后面讨论的几种结构的同步器都是基于这种脉冲到脉冲的同步器设计的,所以都对相邻两次脉冲脉冲信号或者电平信号都不能离的太近。为了防止这种现象发生,最好保证相邻两次的脉冲间隔大于2个目标域时钟周期。

2.2 脉冲到电平同步

在实际应用当中,有时需要脉冲到电平的同步,实现方法和脉冲到脉冲的同步大体相同,区

别在于,脉冲到电平的同步需要对电平维持时间的控制。具体的电路实现如图 5 所示。

脉冲到电平的同步和脉冲到脉冲的同步实现原理相同,脉冲到电平同步电路多了一个电平

宽度控制电路,电平宽度控制信号level_clear_i是由目标时钟域时钟控制生成的。根据电路不同的需求,有电平宽度控制信号产生不同宽度的电平信号。

2.3 电平到电平的同步

实际应用中,如果是慢时钟域到快时钟域的同步,电平到电平的同步两级异步触发器就可以完成,但是两级触发器构成的同步只适合时钟域时钟相差不大或者慢始终域到快时钟域的情况。该电平到电平的同步电路是在脉冲到电平的同步电路之前加一个电平到脉冲的转换电路。具体的电路实现如图7所示。图7左边第一个虚线框里是一个电平到脉冲的转换单元,通过这个转换单元实现在原时钟域内将电平转换成与原时钟域同步的脉冲信号,然后经过第二个虚线框内的脉冲到电平的同步电路,实现了原时钟域的电平信号到目标时钟域的电平信号的同步。

2.4 电平到脉冲的同步

电平到脉冲的同步和电平到电平的同步实现方法相似,将图 7 中第二个虚线框内的电路替换成脉冲到脉冲的同步即可,具体的电路结构图如图 8 所示。第一个虚线框内的也是一个电平到脉冲的转换单元,然后经过后面的脉冲到脉冲的同步电路,实现了电平到脉冲的同步。

303

303

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?