在使用libero工具开发时,如果删除已经综合过的顶层输入输出信号,在下次综合会报错找不到管脚约束,其实是因为libero的学术文件不会根据.v文件自动更新,需要找到约束文件删除多余的管脚信号。

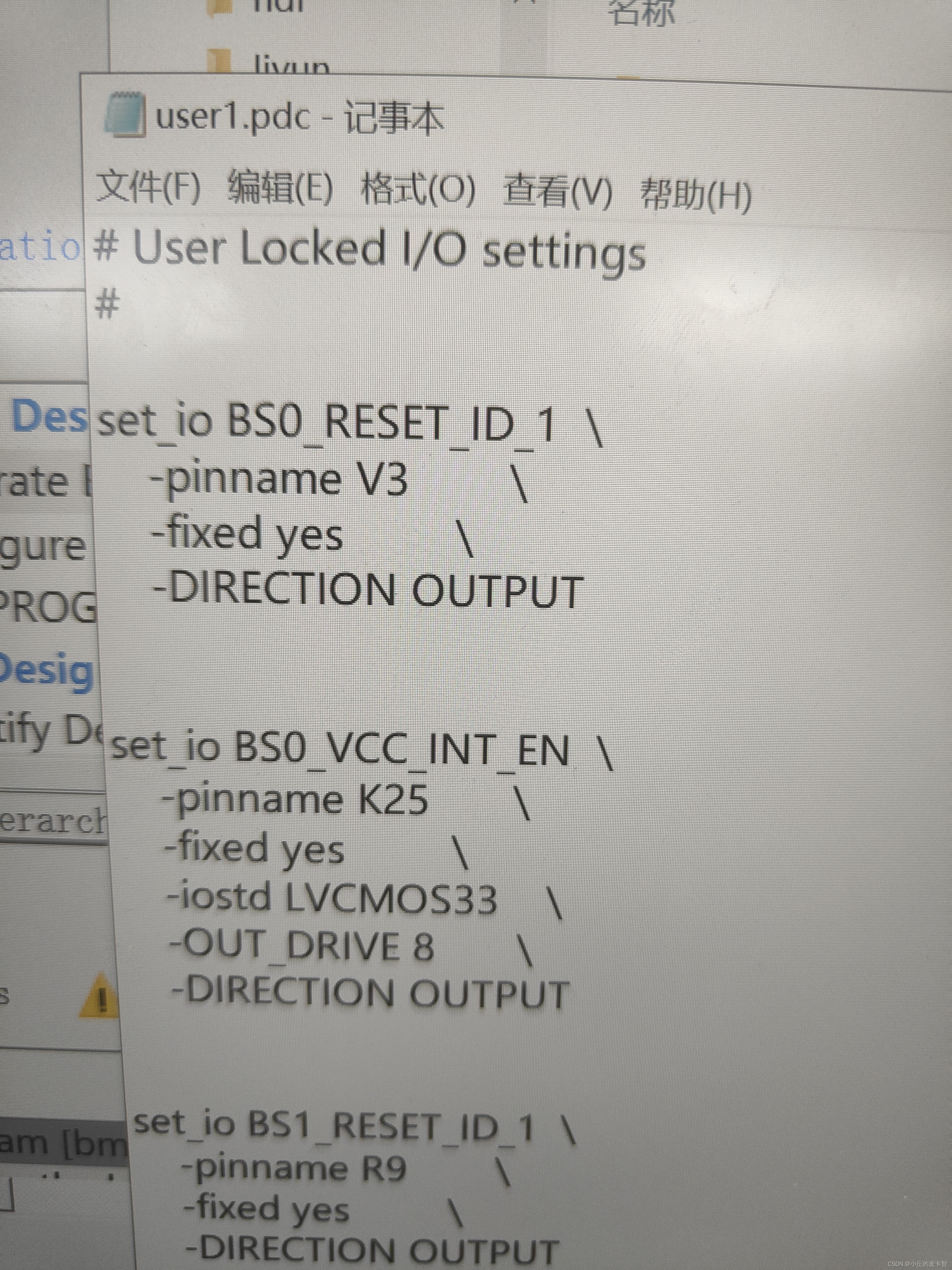

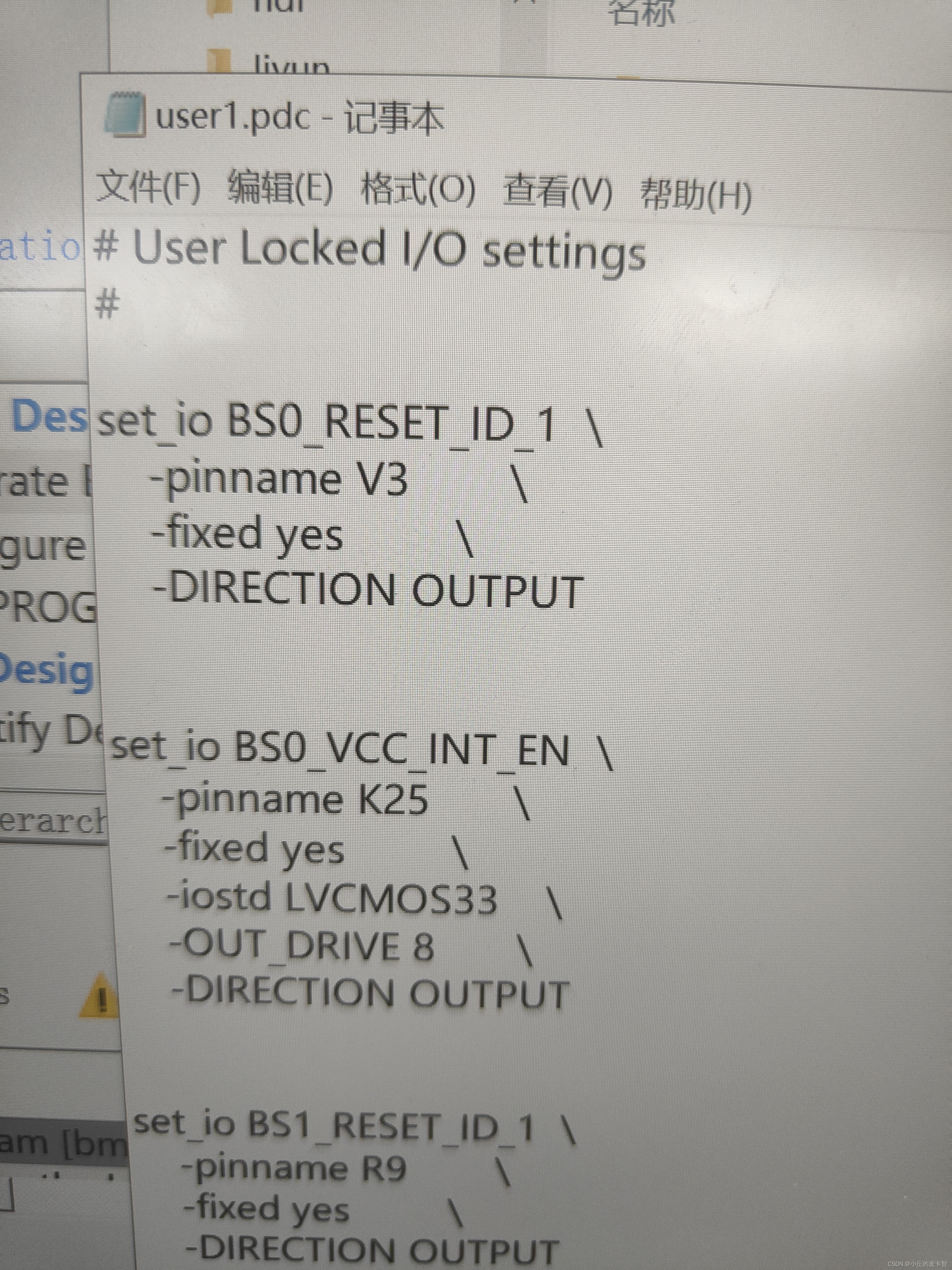

约束文件位置在:libero自动生成的工程文件夹下/constraint/io/.pdc的文件

文章讲述了在使用Libero开发过程中,删除已综合的顶层IO信号可能导致综合时找不到管脚约束的错误,原因在于Libero的学术文件不自动更新,需手动删除约束文件中多余的管脚信号,约束文件通常位于工程文件夹下的/constraint/io/.pdc文件。

文章讲述了在使用Libero开发过程中,删除已综合的顶层IO信号可能导致综合时找不到管脚约束的错误,原因在于Libero的学术文件不自动更新,需手动删除约束文件中多余的管脚信号,约束文件通常位于工程文件夹下的/constraint/io/.pdc文件。

在使用libero工具开发时,如果删除已经综合过的顶层输入输出信号,在下次综合会报错找不到管脚约束,其实是因为libero的学术文件不会根据.v文件自动更新,需要找到约束文件删除多余的管脚信号。

约束文件位置在:libero自动生成的工程文件夹下/constraint/io/.pdc的文件

147

147

1753

1753

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?