Vivado软件中包含有三种类型的 IP核,包括数据处理类IP核、驱动类IP核、存储类IP核。

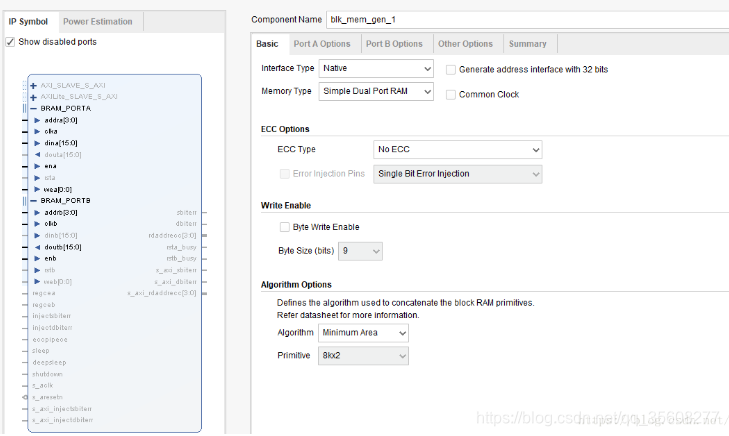

与BRAM对应的存储型IP核是Block Memory Generator(BMG)

调用BRAM

- 首先在Vivado界面的右侧选择IP Catalog 选项。

- 然后就可以在IP 目录中,选择想要的IP核,此处在搜索框输入BRAM,选择我们要使用的BRAM IP核。

- basic设置

(1)在component name后的框里输入将要定制的BMG IP核的名称;

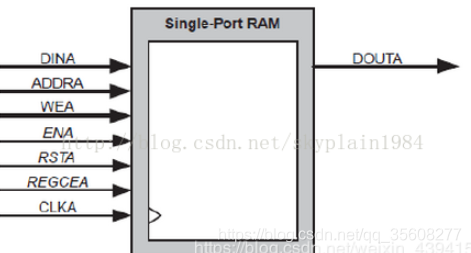

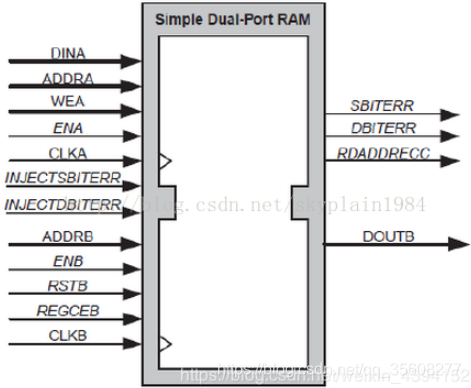

(2)在Memory Type选框中有四种选项:单口RAM、单双口RAM、真双口RAM、单口ROM、双口ROM。

我们常用的是单口BRAM,单口写,单口读。

(3)Interface Type表示BMG IP核的接口类型,如果用PL调用 BRAM,选择Native。如果用PS通过PL来调用BRAM,则选择AXI4。这里选择Native。

(4)ECC Options表示纠错编码选项,主要调整BMG支持的软错误纠正控制(软ECC)模块的实现和使用,一般不会使用,除非对系统可靠性要求很高的场景中才会考虑使用。这里不进行调整。

(5)写使能和算法选项同样不做任何修改。

-

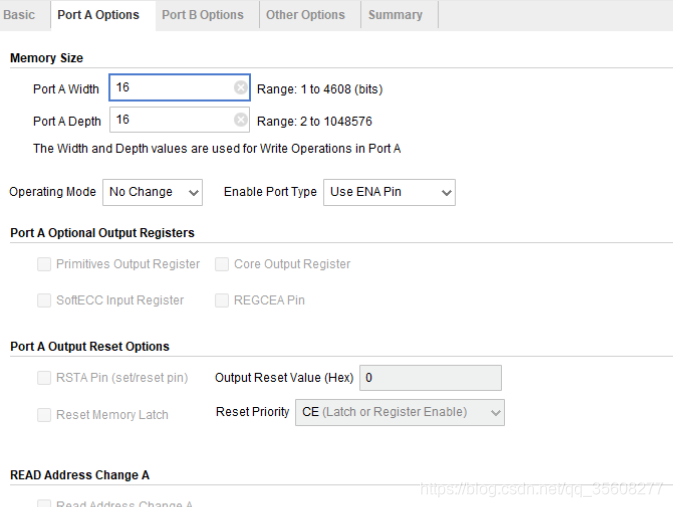

设置端口的位宽以及深度

-

Port A Width即位宽,也就是你存储数据的有多少位,Port A Depth即深度,也就是你要存多少个数据。端口A设置好后,还需要点击Port B Options,点击完进入Port B Options选项后,系统会帮你自动设置好端口B的宽度和深度,因为B肯定是和A一样的。

(1)如果打算以.coe文件来初始化BRAM,操作模式选框要选“读优先”,程序中不再需要对BRAM进行写,只进行读。

(2)使能端口类型选框,其作用是选择是否加入ENA引脚,该引脚可看做是BMG的开关信号的输入引脚。为了方便,选择“总是使能”,这样,BMG就会一直处于工作状态。

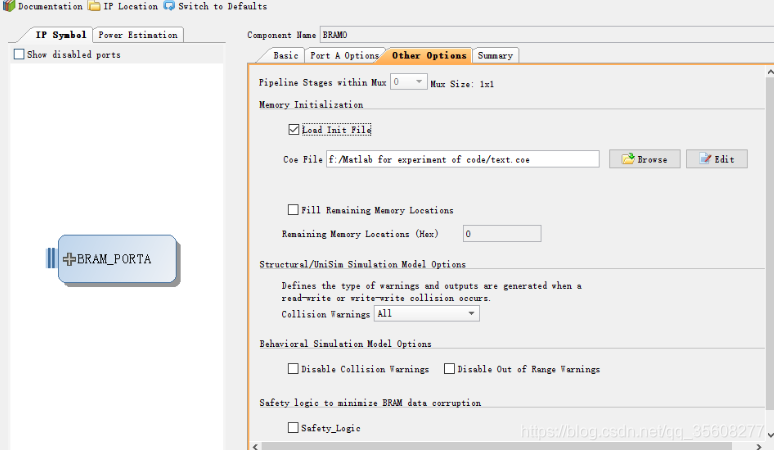

在Other Options选项中,有一个Load Init File选项,即加载初始化文件,在这里勾上后,即可加载已存储好数据的.coe文件。

MEMORY_INITIALIZATION_RADIX=16; //表示数据的进制类型

MEMORY_INITIALIZATION_VECTOR= //表示存储的数据

7ADB,BDB2,5646,88D5,74E9,D990,481D,69A9,2DA4,E097,…

.coe文件可以借助matlab来得到。部分关键代码如下:

r = dec2hex(x2);

fid = fopen('text.coe','w');

fprintf(fid,'MEMORY_INITIALIZATION_RADIX=16;\n');

fprintf(fid,'MEMORY_INITIALIZATION_VECTOR=\n');

for i = 1:3191

fprintf(fid,r(i,:));

if i==3191

fprintf(fid,';');

else

fprintf(fid,',');

end

if mod(i,15)==0

fprintf(fid,'\n');

end

end

- 然后点击下方OK,然后再点击弹出来的窗口的Generate即可生成BRAM 的IP核。

例化

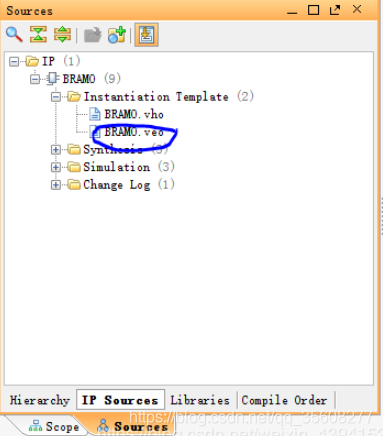

(1)在IP Sources文件夹中找到.veo文件,打开

.veo是verilog

.vho是VHDL

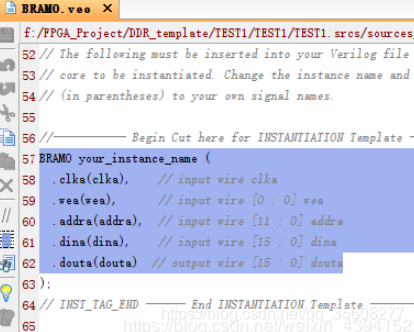

(2)复制BRAM0的例化verilog代码(下图选中区域);

(3)在工程中新建仿真文件,即testbench文件;

(4)读懂BRAM“写优先模式”的时序图,并编写testbench。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date:

// Design Name:

// Module Name:

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module Bram_test();

//Testbench时钟信号

parameter size = 100;

reg clka = 0;

reg wea = 0;

reg [11:0] addra = 12'h000;

wire [15:0] douta; //输出信号设置为wire垿

always #10 clka <= ~clka;

initial

begin

#45 wea = 1;

repeat(size)

begin

#20 addra=addra+1;

end

wea = 0;

end

BRAM0 My_Bram (

.clka(clka), // input wire clka

.wea(wea), // input wire [0 : 0] wea

.addra(addra), // input wire [11 : 0] addra

.douta(douta), // output wire [15 : 0] douta

.dina()

);

endmodule

(5)将testbench文件设为顶层文件,并进行行为仿真;

(6)输出波形仿真结果

ref

https://blog.csdn.net/XXQ121/article/details/81037687

https://blog.csdn.net/weixin_43941525/article/details/90408941

2401

2401

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?