1. 前言

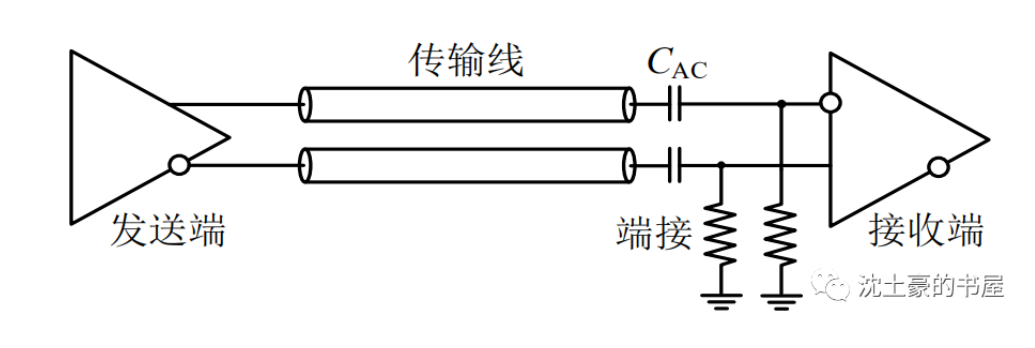

在高速串行互连系统中,采用在互连通道中串联 AC 耦合电容,实现不同电平

信号互连时的隔直作用。

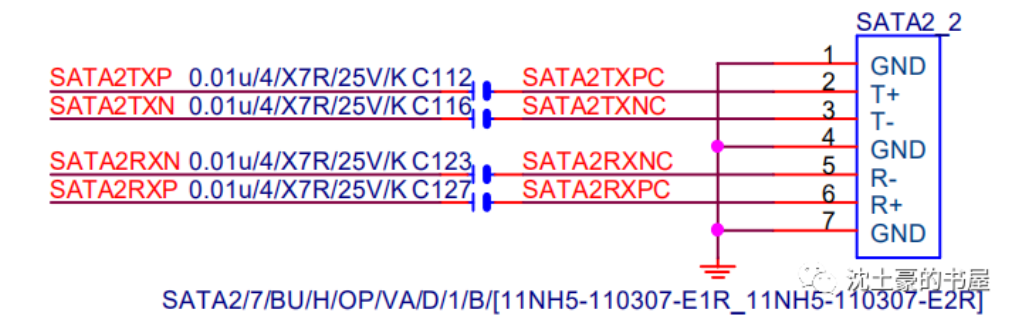

这个电容值的选取,我在技嘉的B75的SATA接口,看到了选取的是0.01uF。

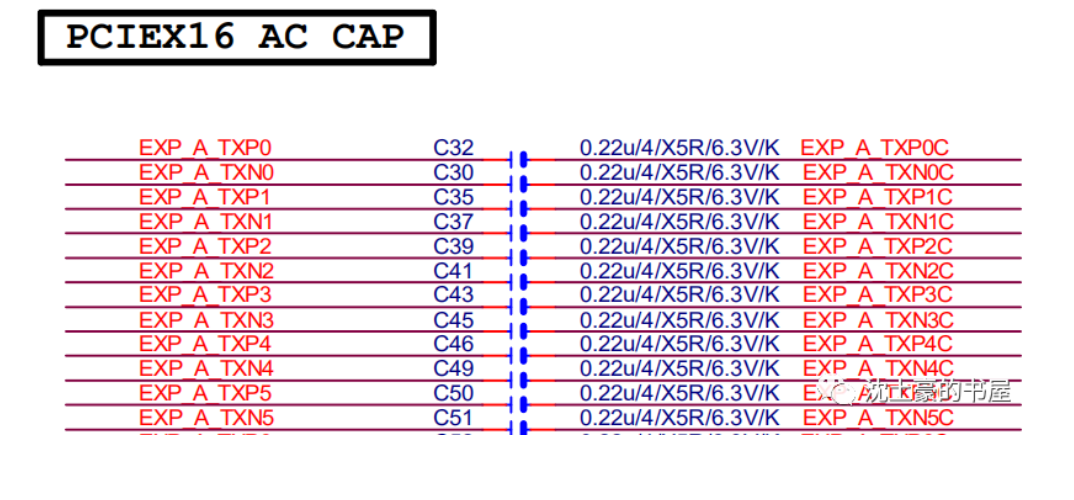

PCIE的接口上,看到了0.22uF

2. 这些值是怎么来的?

我在一篇硕士论文和一些回答里找到了一些答案:

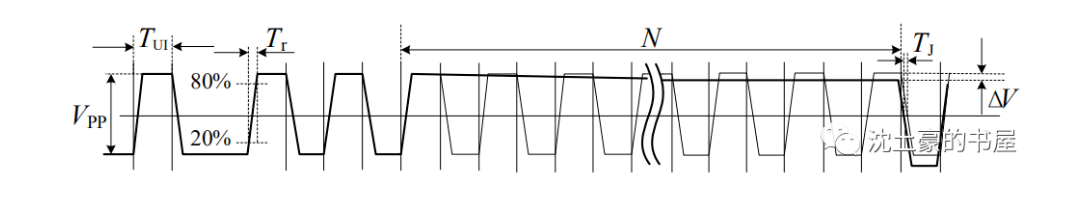

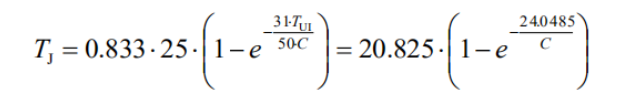

在高速串行系统中,若驱动器在某时段内发送连“1”码,接收器上电压会呈指数降低,如图 所示,时间越长,压降△V越大,此时若码型变为“0”,则接收器上电压迅速降低并反相,电压降低的起点低于理想位置,使边沿变化时刻比理想位置提前,即 AC 耦合带来了码型相关抖动 TJ。

作者还有一些相关的推导:

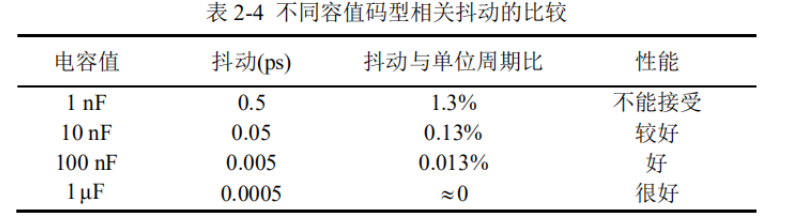

我直接说下结论,这里作者通过长连0/1,推导出了电容值与数据码型相关抖动大小的一个公式。

文章很长我也没有看完,不过结论:这个AC耦合电容的选取,是跟PCS层编码规则出现的长连0/长连1导致的直流压降有关。

这个“压降”又会导致data depend jitter,即码型相关的抖动。

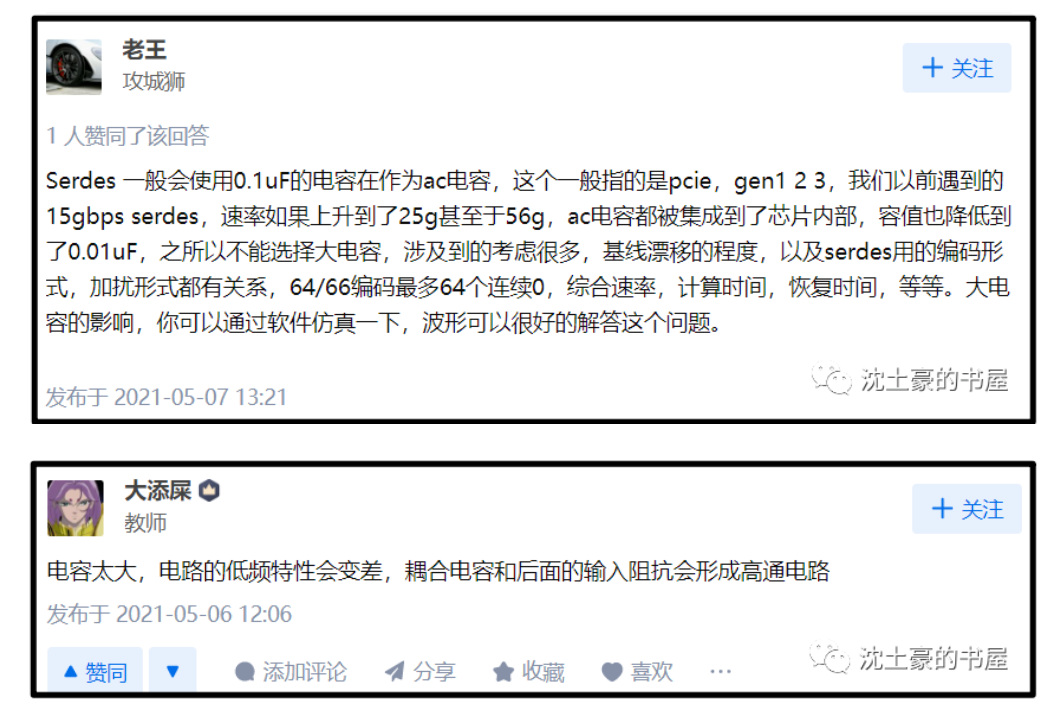

当然我也看到了一些其他回答:

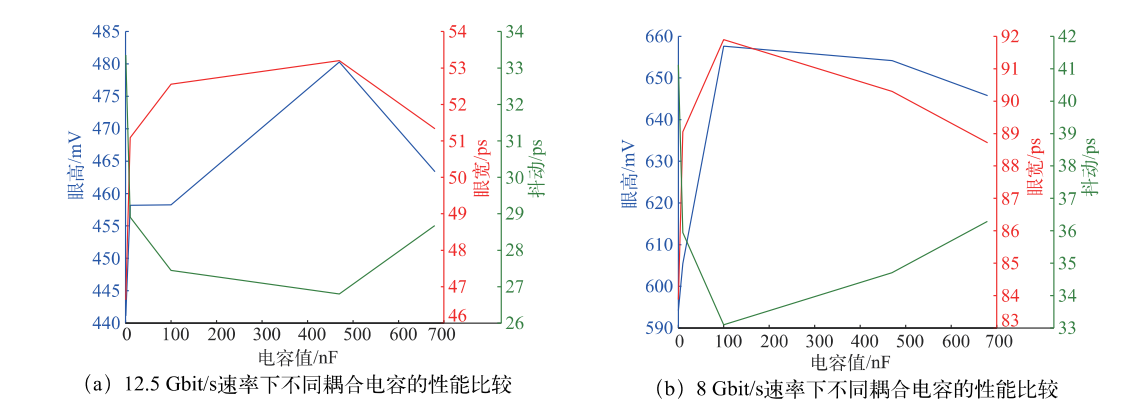

还有一篇,《16Gbit/s 高速串并收发器调试及交流耦合电容选取方案》

文章工作:基于可测性设计 (DFT) 的高速 SerDes 调试方法实现了动态配置 SerDes 参数。测试了不同速率下高速 SerDes 的传输性能,并且验证了不同速率下交流(AC) 耦合电容的选取对 SerDes 性能的影响。

3. 资料

推导是从一篇哈工大的硕士论文里的看到的,还有一篇

《25 Gbps 跨背板高速串行链路信号完整性设计》蒋炜。

16_Gbit_s高速串并…调试及交流耦合电容选取方案_张秀均

这两篇文章都很好。

欢迎关注我的公众号:沈土豪的书屋

文章探讨了在高速串行互连系统中,AC耦合电容如何用于隔直作用,并通过分析码型连续时的电压压降,解释了电容值选取与码型相关抖动的关联。研究指出,电容选择与PCS层编码规则产生的直流压降和由此引发的数据依赖抖动紧密相关。此外,文中提及了一种基于DFT的高速SerDes调试方法,验证了不同速率下交流耦合电容对传输性能的影响。

文章探讨了在高速串行互连系统中,AC耦合电容如何用于隔直作用,并通过分析码型连续时的电压压降,解释了电容值选取与码型相关抖动的关联。研究指出,电容选择与PCS层编码规则产生的直流压降和由此引发的数据依赖抖动紧密相关。此外,文中提及了一种基于DFT的高速SerDes调试方法,验证了不同速率下交流耦合电容对传输性能的影响。

5938

5938

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?