转载来源:

低功耗设计基础:Clock Gating

后端Timing基础概念之:为何ICG容易出现setup violation?

为了节约动态功耗,最初有个十分简单的想法:在芯片实际工作过程中,有些信号或者功能并不需要一直开启,那么就可以在它们不用的时候将其时钟信号关闭。这样一来信号不再翻转,从而能够有效减少动态功耗,这就是Clock Gating。

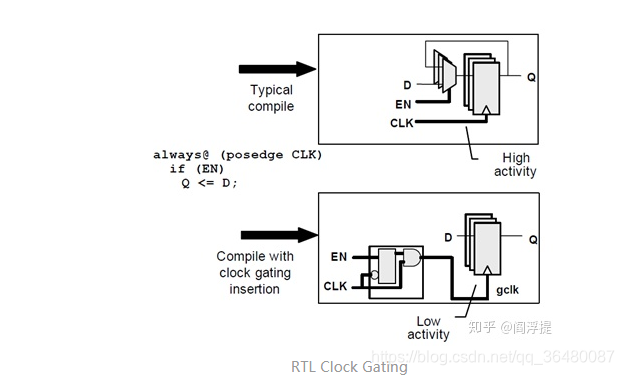

那么Clock Gating是如何被加入到design中的呢?下面的例子介绍了在RTL阶段加入Clock Gating的方法:

可以看到在加入Clock Gating之后,DFF的clock信号前多了一个使能端EN,从而可以控制该时钟信号的打开与关闭。

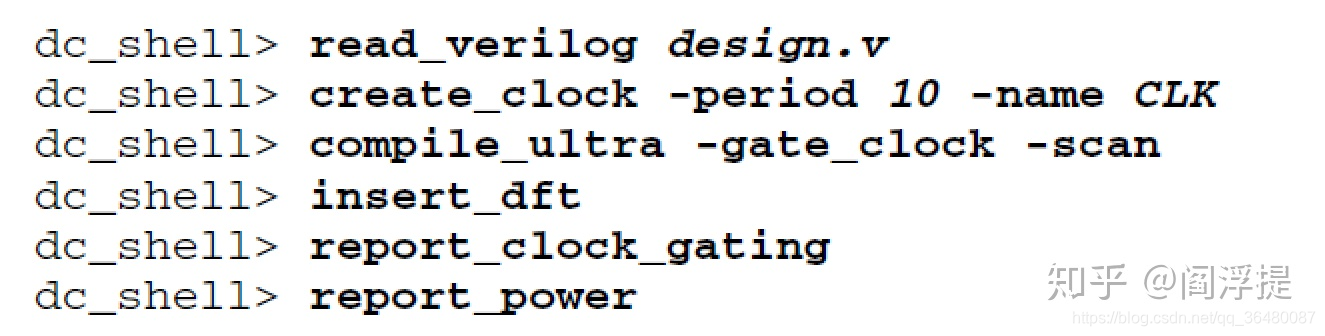

除此之外,在综合阶段,EDA工具同样支持自动插入Clock Gating。以Synopsys公司的Design Compiler工具为例,简单的插入Clock Gating的方法如下:

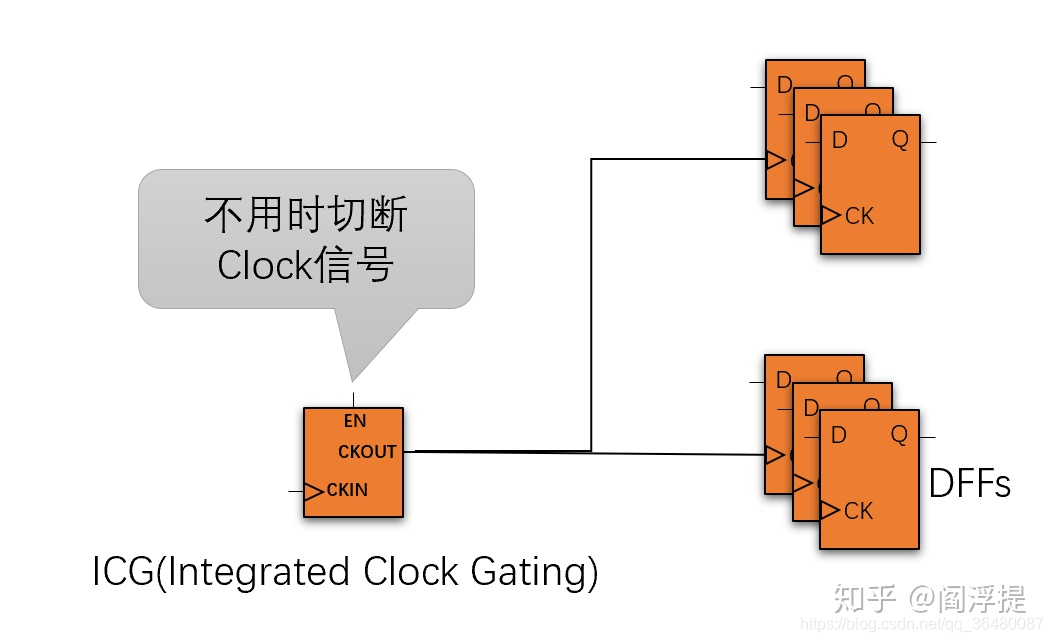

ICG(Intergrated Clock Gating)作为low power的设计手法之一,已经在实际中得到广泛应用。它们能够在某些时候将某些clock关断从而达到降低功耗的目的。

一般每个ICG会控制一个或多个DFF,通过某个DFF传递过来的控制信号控制ICG的开启或者关断。

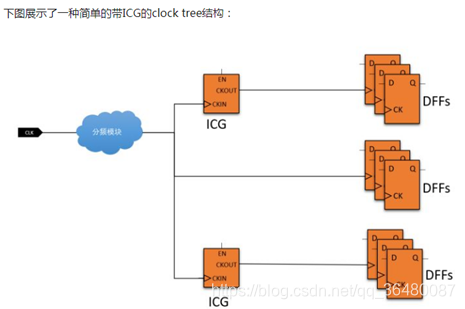

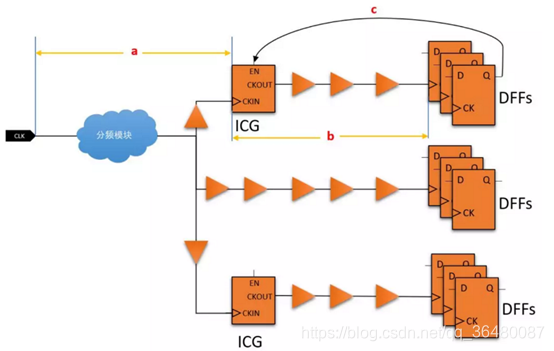

然而,在CTS(clock tree synthesis)工具或者命令综合时钟树的时候,ICG不会被看作sink因此并不会作为balance对象,因此就会出现如下这种结果:

由上图可以看出,在分析DFF到ICG的setup timing时:

launck clk delay = a + b

capture clk delay = a

因此,对于ICG的setup path,天然存在clock skew:b ,而skew的大小完全取决于ICG距离sink DFF有多远。

在出现setup violation的ICG path上,比较多见的就是因为ICG和sink DFF的clock之间存在较多逻辑或者物理上距离较远,从而导致skew较大而发生setup violation。

针对这种现象,

(1) 在实际设计中,我们可能会考虑将出现setup violation的ICG尽量放在sink DFF附近以减小skew。

(2)与此同时,EDA工具也提供命令来收紧ICG的timing constraint来迫使工具来优化这些path,比如set_clock_gating_check命令。

另外,CTS工具会对其做clone、declone操作。

ICG cell Clone:

受相同ICG cell控制的时序单元较多或者分布不均匀时,就会导致ICG cell连线过长,这时可通过clone ICG cell进行优化;

ICG cell De-Clone:

受相同ICG cell控制的时序单元较少,就会导致ICG cell数量过多,设计density增大。这时可通过De-clone ICG cell进行优化;

5032

5032

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?