在数字IC芯片中,时钟树的功耗占比可能高达30%,因此一般会采取门控时钟的方式来降低该部分的功耗。所谓门控时钟,就是在芯片实际工作过程中,有些信号或者功能并不需要一直开启,那么就可以在它们不用的时候将其时钟信号关闭。这样一来信号不再翻转,从而能够有效减少动态功耗。

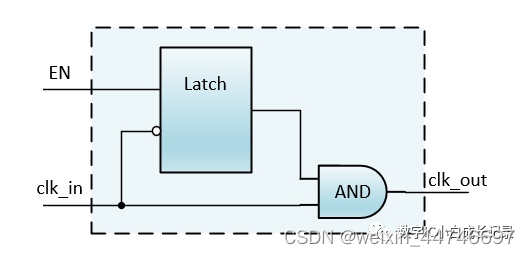

目前门控时钟都采用集成门控时钟单元(ICG,integrated clock gating cell),其结构如下。由一个latch和一个与门(也有的是或门)组成,可以过滤掉EN信号中的毛刺。一般的工艺库中都会有专门的ICG以供调用。

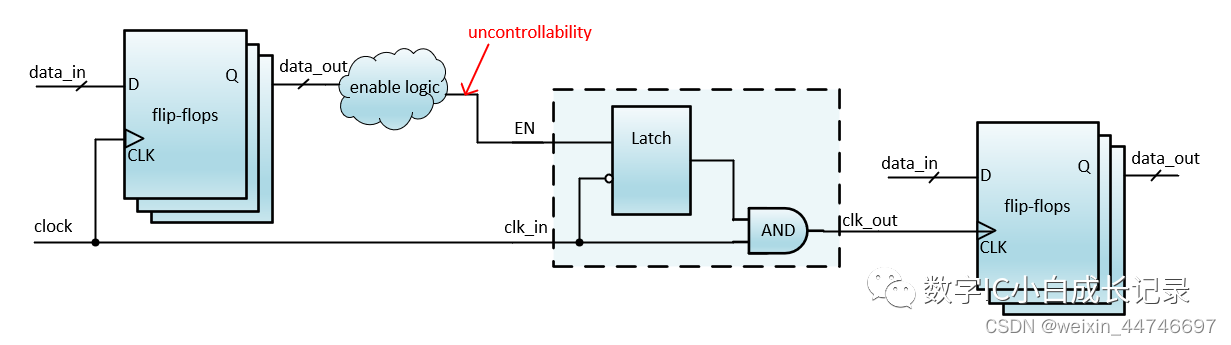

插入ICG后对电路的可测性有什么影响呢?

如下图所示,可以看到由于ICG的EN端不可控,导致ICG后面所驱动的所有寄存器的时钟均不受控,也就是说会带来scan的时钟可控问题,会很大程度降低故障覆盖率。

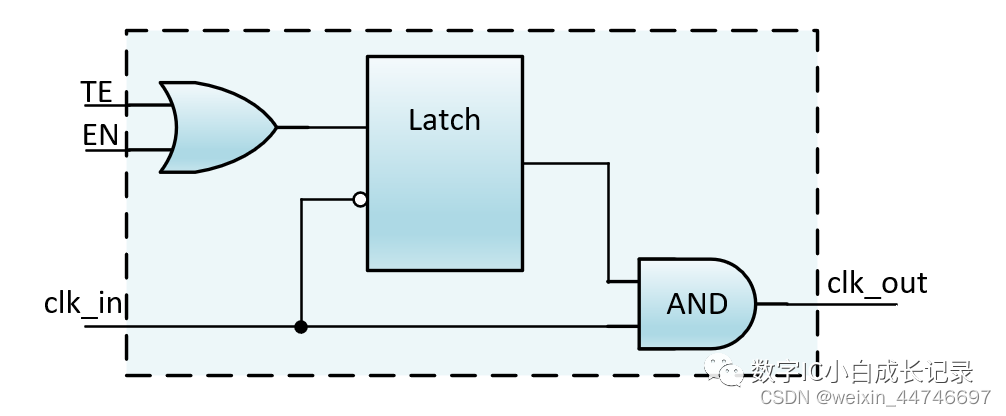

为解决上述问题,现在工艺库所提供的ICG一般会在latch的前面再集成一个或门,并增加一个TE端口,如下图所示,当TE为1时,ICG被强制打开,用来达到对scan时钟的可控制性。

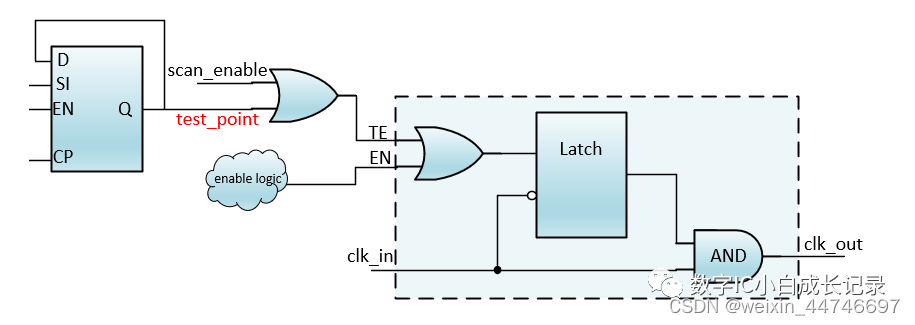

新增的这个TE端口需要接到哪里呢?

一般做法是接到scan_enable信号上:当scan shift时,scan_enable为1,ICG打开使时钟通过,可以正常shift;当scan capture时,scan_enable为0,此时ICG的开关取决于EN端的值,因此enable logic这一部分的逻辑是可以被测试到的。

但scan capture时ICG又由EN端进行控制,如果此时enable logic非常复杂,会使得ATPG工具很难构造EN为1的场景,使得ICG后面所驱动的寄存器无法被测试到。

因此改进的做法是采用test point来控制ICG的TE端:如下图,将test_point与scan_enable相或之后再接到ICG的TE端。在scan shift时,scan_enable为1,ICG打开可以正常进行shift;在scan capture时,由test_point来控制ICG,而test_point的值可以由ATPG工具进行指定,为0时可以测试到enable logic这一部分的逻辑,为1时可以保证ICG后面所驱动的寄存器在capture时有时钟。

3642

3642

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?