背景知识介绍

近年来,随着CMOS技术中器件密度和时钟频率的急剧增长,功耗的增加日益成为一个不可忽视的问题。过高的功耗不仅会导致电子产品使用时的温度上升,也会造成其寿命的大幅下降。低功耗设计技术受到广泛重视。

众所周知,IC设计中的power包含2个部分,分别是dynamic power以及static power。其中,dynamic power是在晶体管开关过程中消耗的,包括switching power(来源于单元输出端外部容性负载的充放电过程)和internal power(来源于输入电压transition过程中流经PMOS-NMOS的短路电流);而static power是当器件通电后晶体管泄露电流所产生的,即为leakage power(来源于反偏pn结二极管泄漏,亚阈值泄漏和栅极泄漏)。

常见的低功耗strategy

在IC设计中常用的有如下几种低功耗策略:

1.supply voltage reduction

由于功耗和电源电压的平方成正相关,故后者的降低能有效减小功耗的产生。但同时电压的降低会引起switching速度的降低,同时在于外部设备进行对接时由于电压的差异性产生额外的问题。

2.clock gating

时钟门控是妇孺皆知的一种低功耗设计方法,也是最常用的一种方法。通过使时钟信号不经过在某时间段内不需要进行逻辑翻转的register,从而降低功耗。

3.Multiple-Vt Library cells

CMOS技术中可以使用具有多阈值电压的单元库,低阈值电压的单元速度快,但亚阈值泄露电流更大;而高阈值电压的单元速度慢,但亚阈值泄露电流更小。通常工具会根据具体电路对这两种单元的摆放进行权衡,从而达到对功耗的最佳优化效果。

4.Multivoltage Design

在现在的SOC设计中,往往集成了多个模块,各个模块的功能不同,对其性能的要求也不同,多电压的设计方法可以有效降低功耗。对于CPU和RAM来说,可以提供较大的供电电压,而对于外设而言,供电电压可以设为一个更小的值。

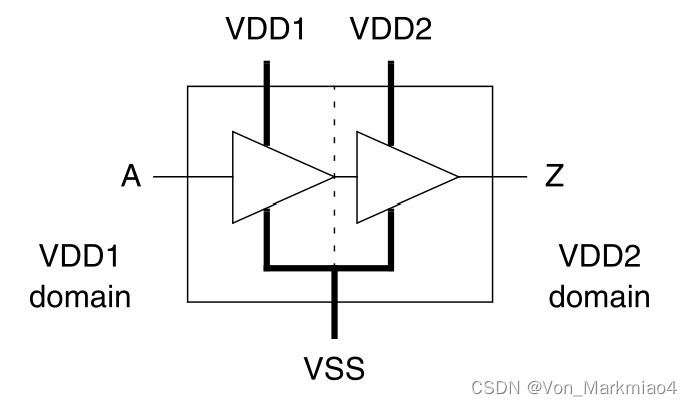

多电压设计需要在各个power domain之间放置level shifter,从而使电压能平稳转换。

5.Power Switiching

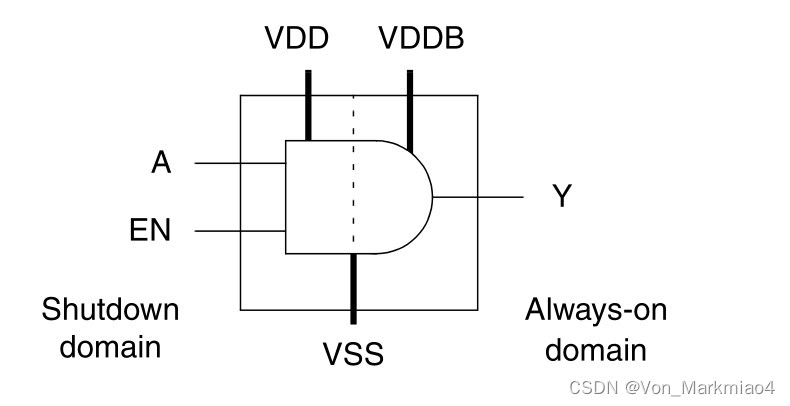

电源关断策略,就是对于某些不需要使用的模块进行暂时的供电电压关断,在技术实现上要求在始终通电的模块和关断的模块间放置isolation cell,当关断的模块没有电源时,isolation cell向始终通电的模块提供一个已知的、恒定的逻辑值,从而防止可能导致PMOS-NMOS短路电流的未知值或中间值。在关断的模块中使用retention register,其可以在断电期间通过在断电之前将数据保存来保留数据。

6.DVFS(Dynamic Voltage Frequency Scaling)

动态电压频率调节策略,就是各模块的供电电压和时钟频率可以动态地进行调整,从而达到最低功耗的设计要求。但这一技术实现要求较高,使用也较少。

低功耗cell概述

下面介绍3个最为常用的低功耗cell:

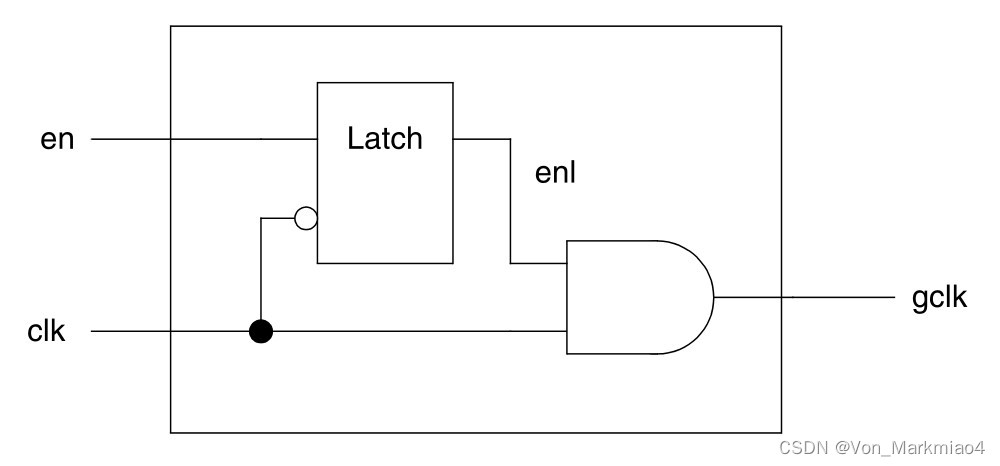

1.clock-gating cells

库单元中的门控时钟单元,往往采用工具已预定义的集成门控时钟(ICG),通过集成的方式,设计者可以很方便地直接进行调用,同时不需要考虑其内部时序问题。

2.level shifters

电平转换单元除了连接VDD,还必须连接两边电压域的供电电源。

3.isolation cells

当该cell的输入端和输出端都通电时,其作为buffer工作;但在输入端断电时,cell提供恒定的输出信号。

后续会介绍upf格式文件的内容以及脚本实例。

467

467

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?