MultiBoot

简介

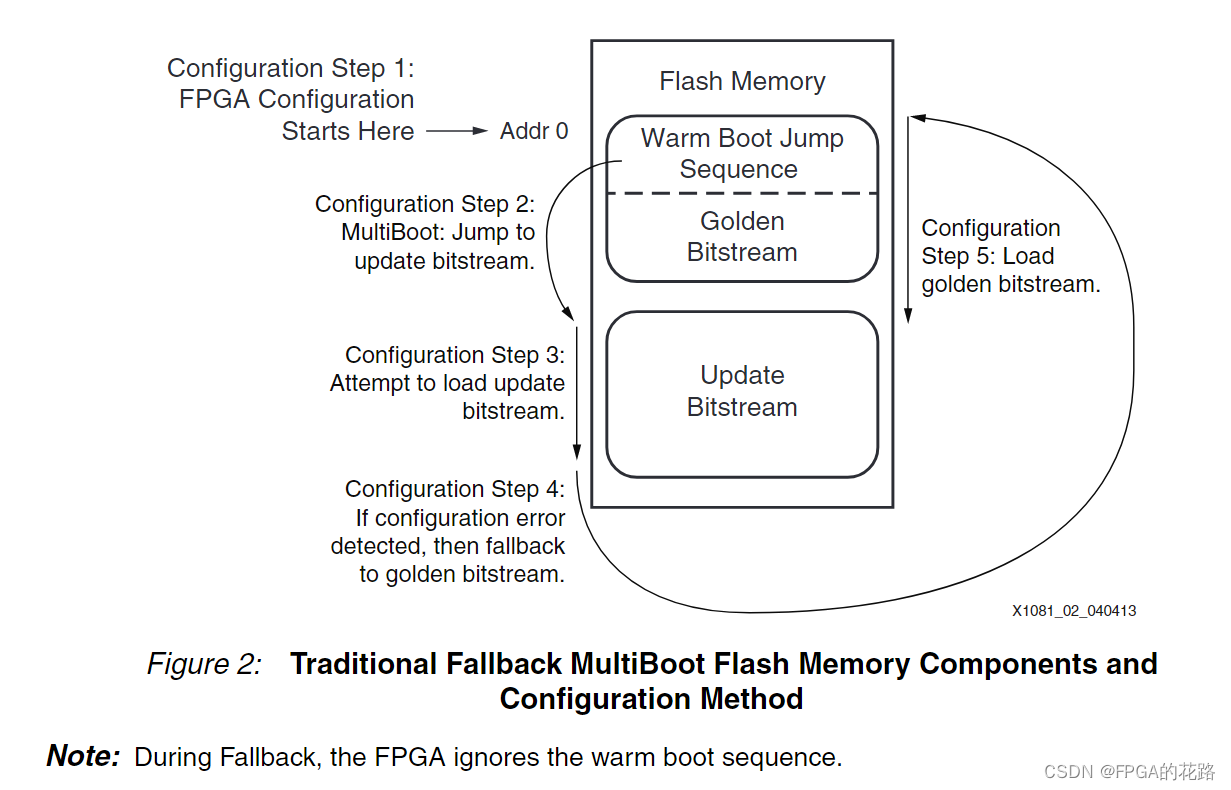

7系列 MultiBoot 功能可用于控制 FPGA 加载两个及以上程序,可指定 FPGA 从指定的 Flash 地址加载程序。

- Fallback 加载 golden 程序

- MultiBoot 加载 update 程序

注:Virtex®-7 HT FPGA不支持 Fallback MultiBoot 功能。

当触发 Fallback 时,内部会产生复位脉冲复位整个 configuration logic,除了 dedicated MultiBoot logic、WBSTAR 寄存器(the warm boot start address)、BOOTSTS寄存器(the boot status)。复位脉冲会拉低 INIT_B 和 DONE 信号,清除 configuration memory,最后从 FLASH 地址 0 重新加载,重新加载会忽略 WBSTAR 和 IPROG 命令。

MultiBoot 实现方式

有以下两种方式可以实现 MultiBoot 功能:

- 设置 bitstream 属性

- 使用 ICAPE2 原语

设置 bitstream 属性

golden 程序从 Flash 的地址0开始存储;当设置了 WBSTAR 属性时,IPROG 会自动嵌入到 bitstream 中。

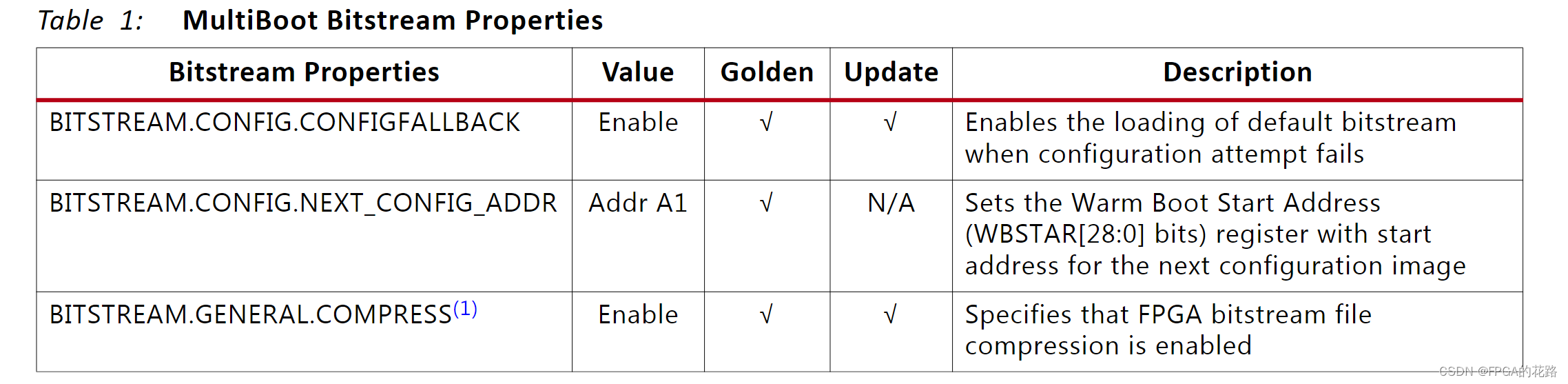

golden 和 update 的 bitstream 属性设置如下,其中 update 不需要设置 NEXT_CONFIG_ADDR 属性。

注:

1、GENERAL.COMPRESS 使能这个属性可减少程序烧写时间和加载时间;

2、通过 xdc 约束直接修改 bitstream 属性相比使用 Vivado GUI 设置更节约时间,因为通过 GUI 设置得先完成实现步骤才能设置,而且更改完还需要重新综合实现。

##Golden 程序 xdc 约束

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x0400000 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 1 [current_design]

##Update 程序 xdc 约束

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 1 [current_design]

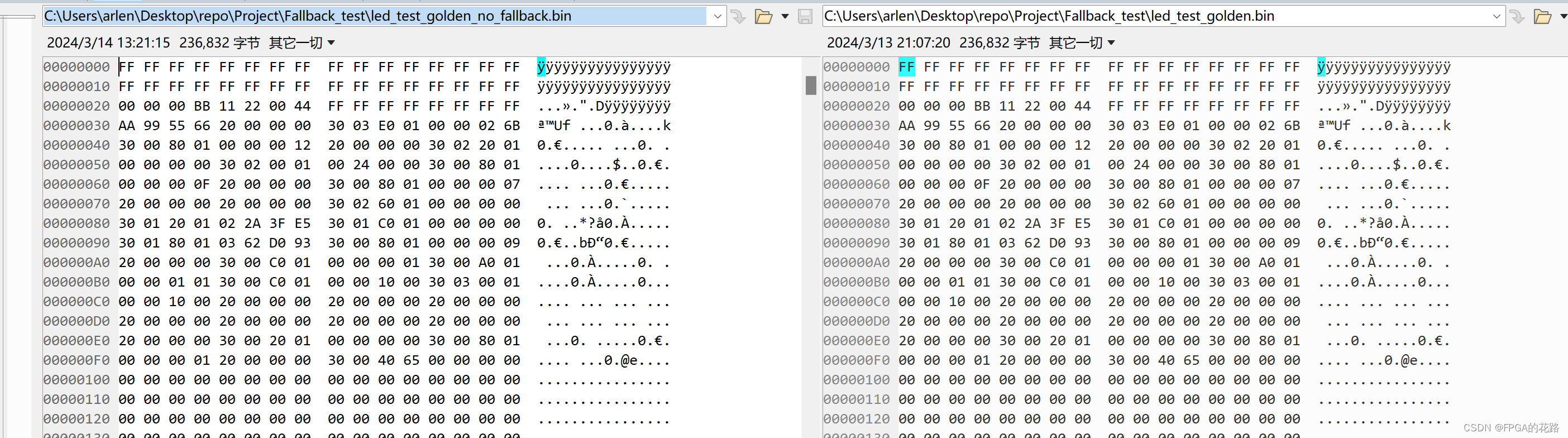

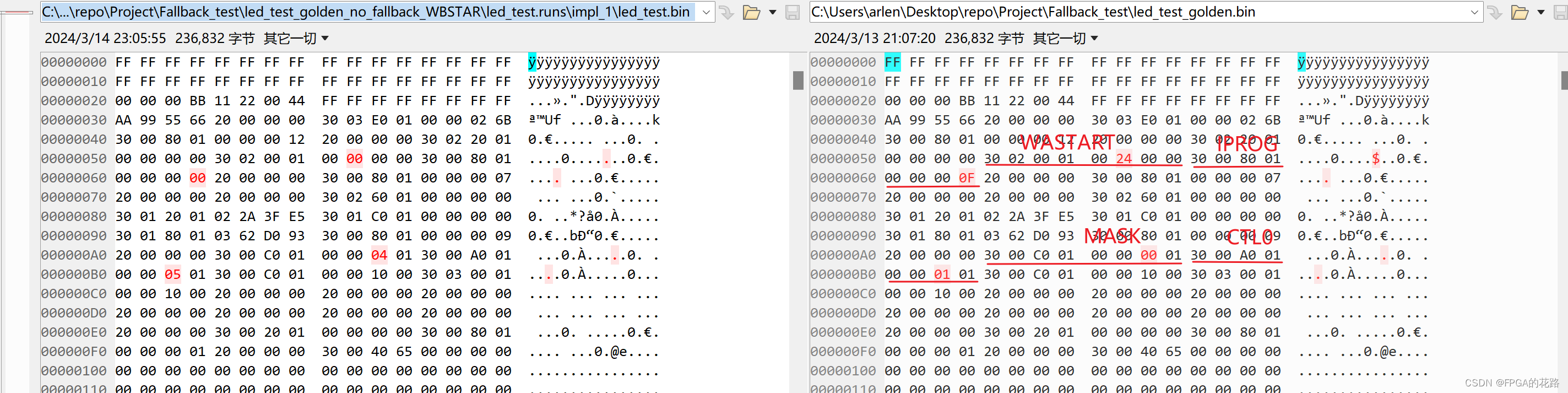

golden 程序约束 NEXT_CONFIG_ADDR, 不管约不约束 CONFIGFALLBACK ENABLE,BIN 文件都没有区别。

golden 程序不约束 CONFIGFALLBACK ENABLE,且不约束 NEXT_CONFIG_ADDR,BIN 文件才禁用 fallback,且删除 IPROG 命令。

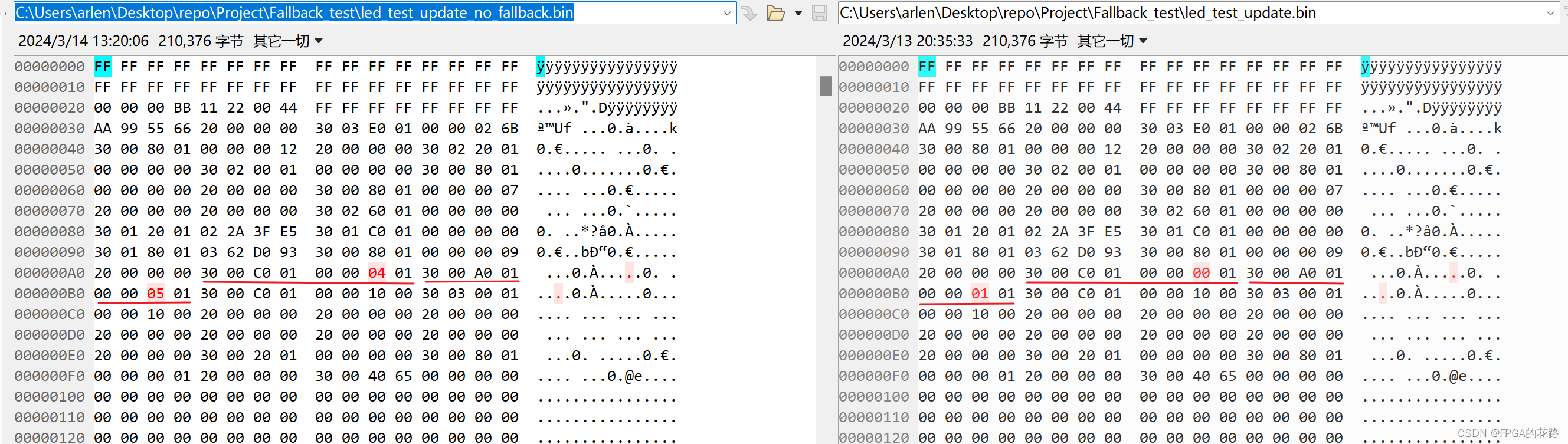

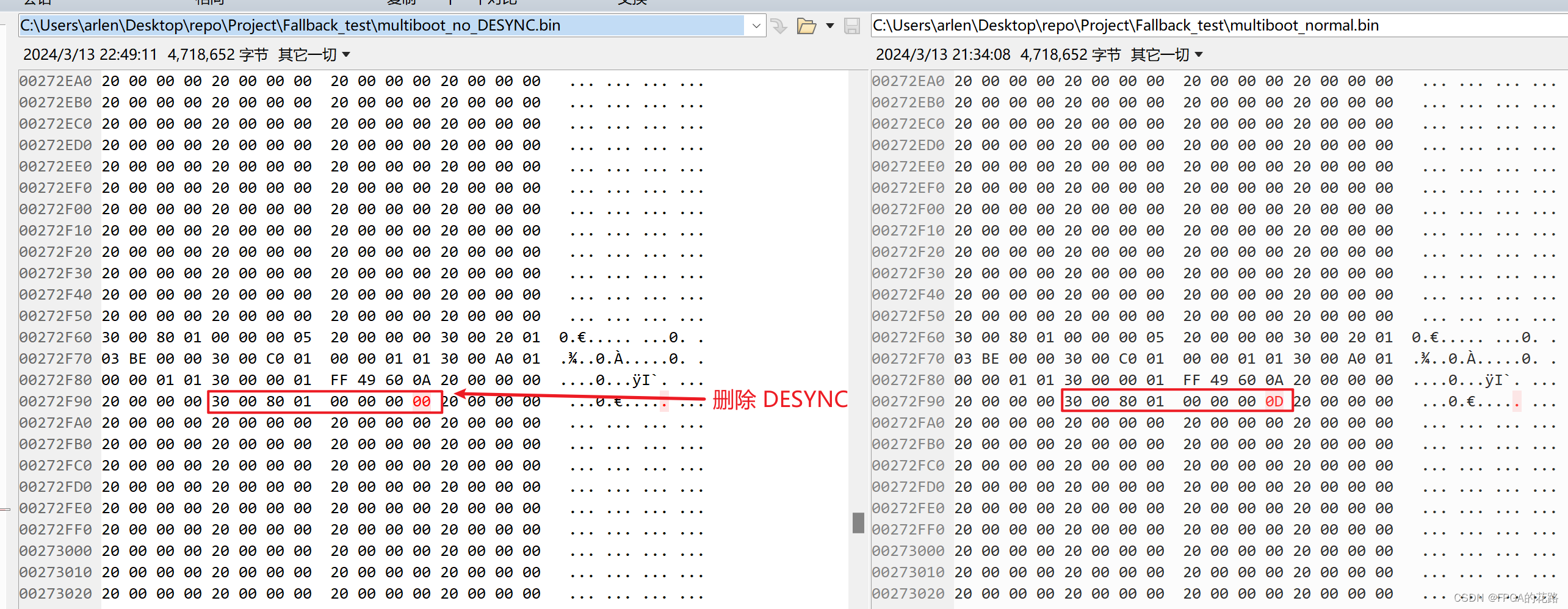

update 程序不约束 CONFIGFALLBACK ENABLE,BIN 文件比较如下,默认禁用 fallback,CRC 错误不会触发回退。

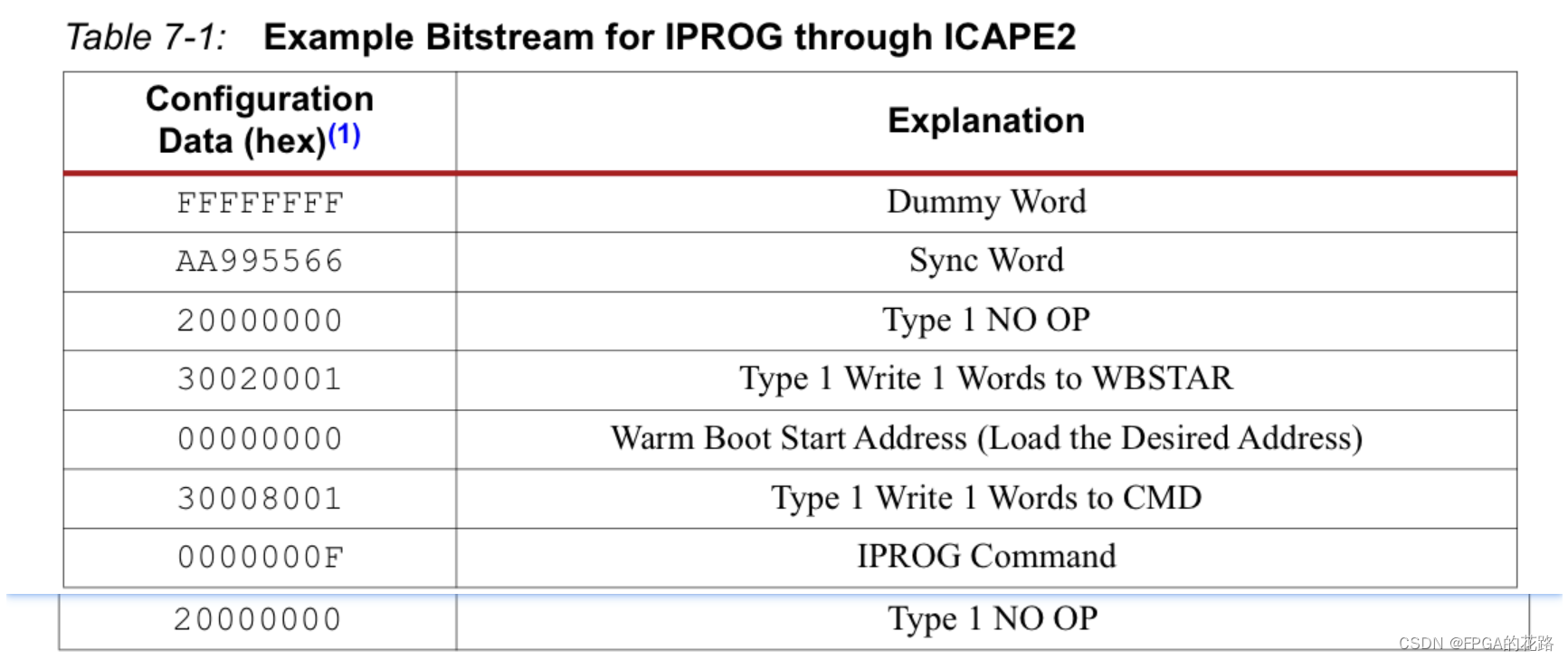

使用 ICAPE2 原语

-

通过逻辑控制 ICAPE2 原语

-

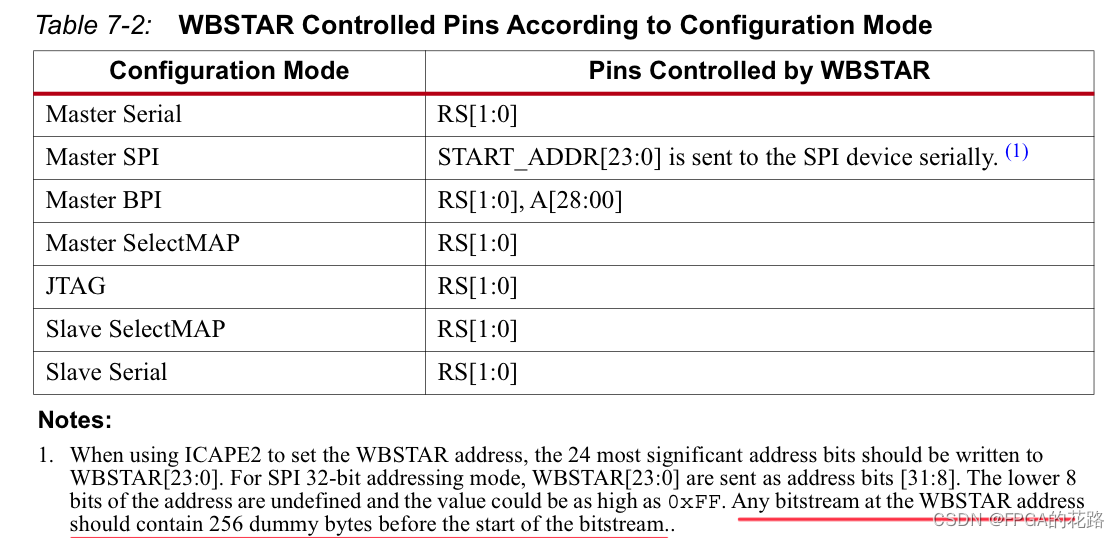

发送流程:同步字 -> WBSTAR -> IPROG

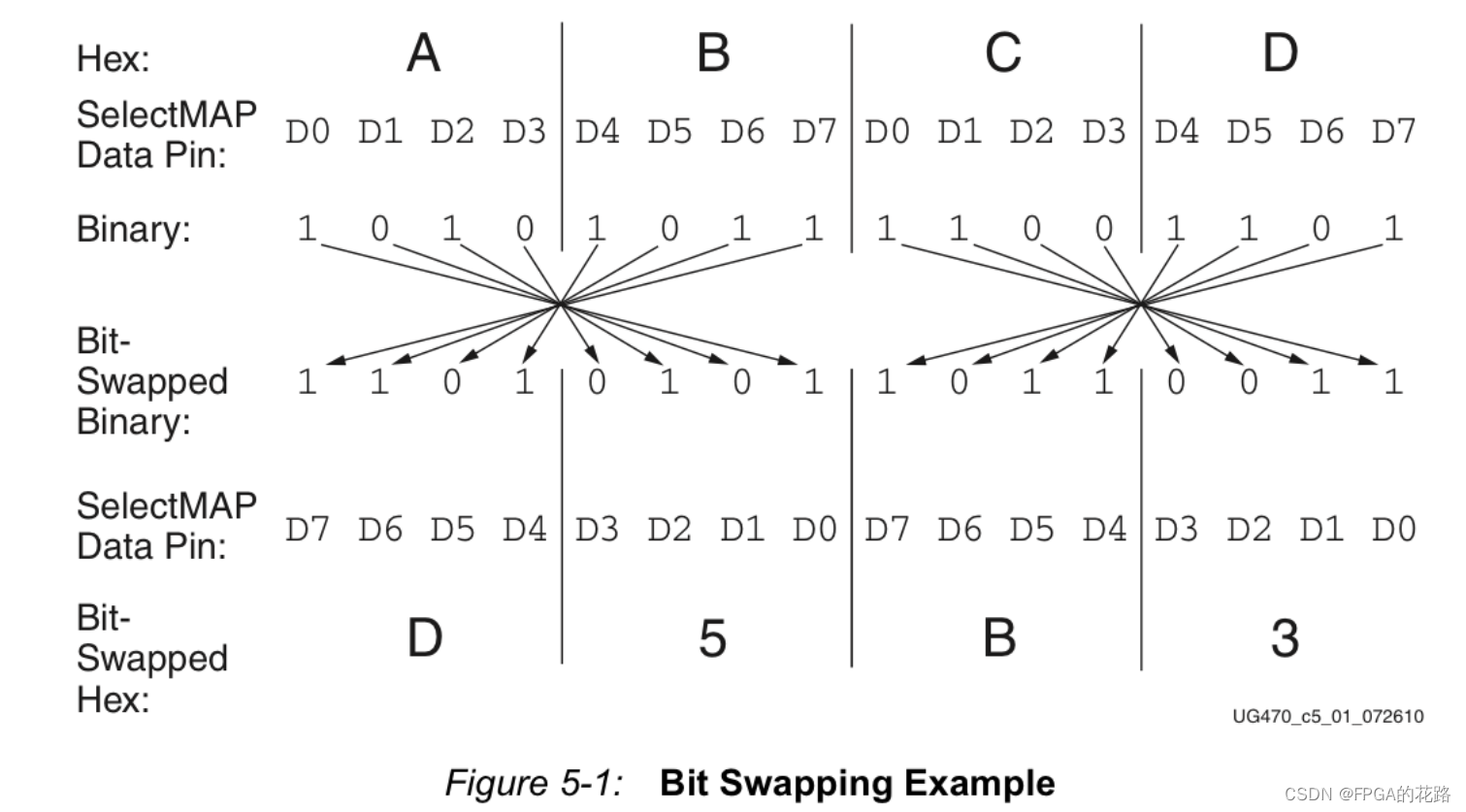

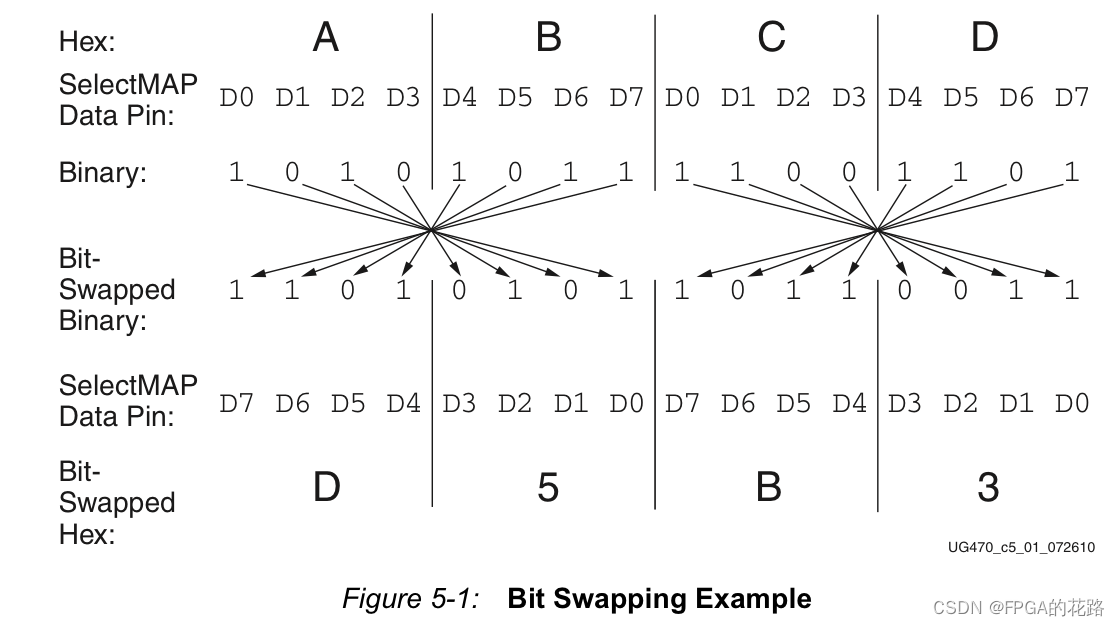

注:输入配置信息需要位转换

WBSTAR 寄存器定义

执行 IPROG 指令后,FPGA 会从 WBSTAR 指示的地址开始进行加载

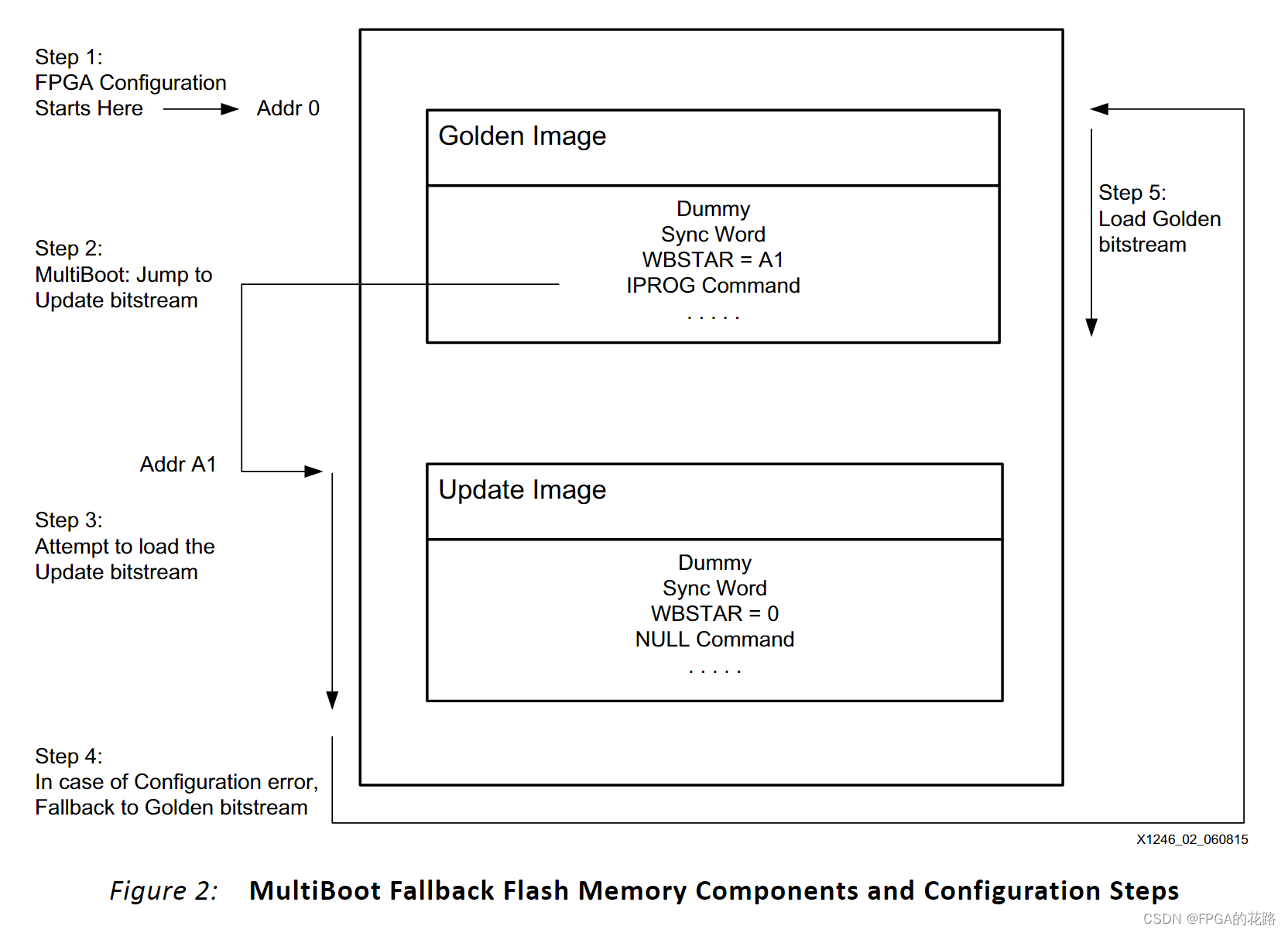

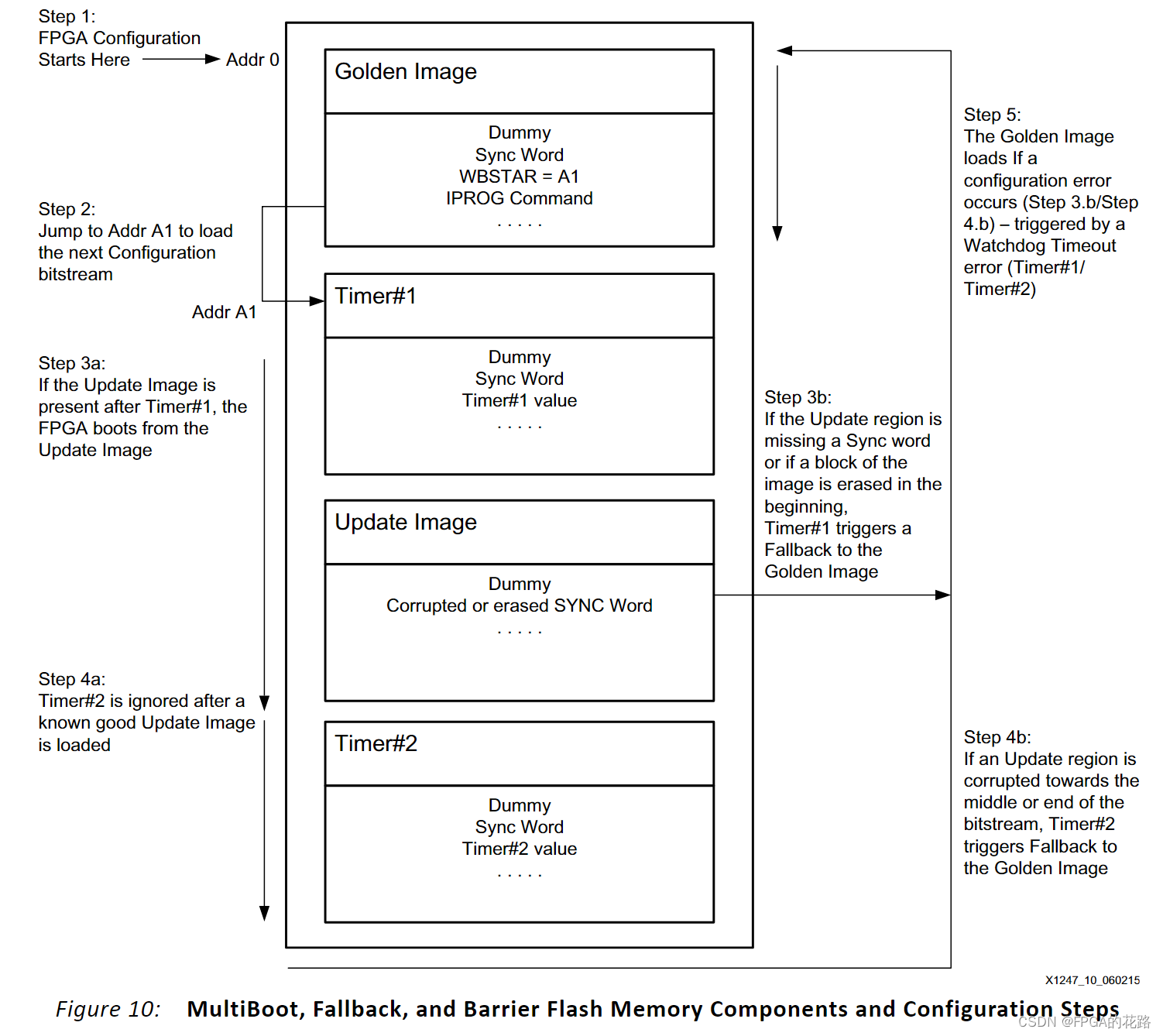

MultiBoot 工作流程

1、执行 IPROG 命令,控制 FPGA 从 WBSTAR 指定的地址开始加载 update 程序;

2、若加载失败则触发 Fallback,然后加载 golden 程序。

注:当触发 Fallback 时,内部会产生复位脉冲复位整个 configuration logic,除了 dedicated MultiBoot logic、WBSTAR 寄存器(the warm boot start address)、BOOTSTS寄存器(the boot status)。复位脉冲会拉低 INIT_B 和 DONE 信号,清除 configuration memory,最后从 FLASH 地址 0 重新加载,重新加载会忽略 WBSTAR 和 IPROG 命令。

生成mcs固化文件 Tcl 指令

write_cfgmem -format mcs -interface SPIX1 -size 16 -loadbit "up 0 <path>/golden.bit up 0x0400000 <path>/update.bit" <path>/filename.mcs

Fallback

以下三种情况会触发 Fallback:

- CRC error

- IDCODE error

- Watchdog timer time-out error

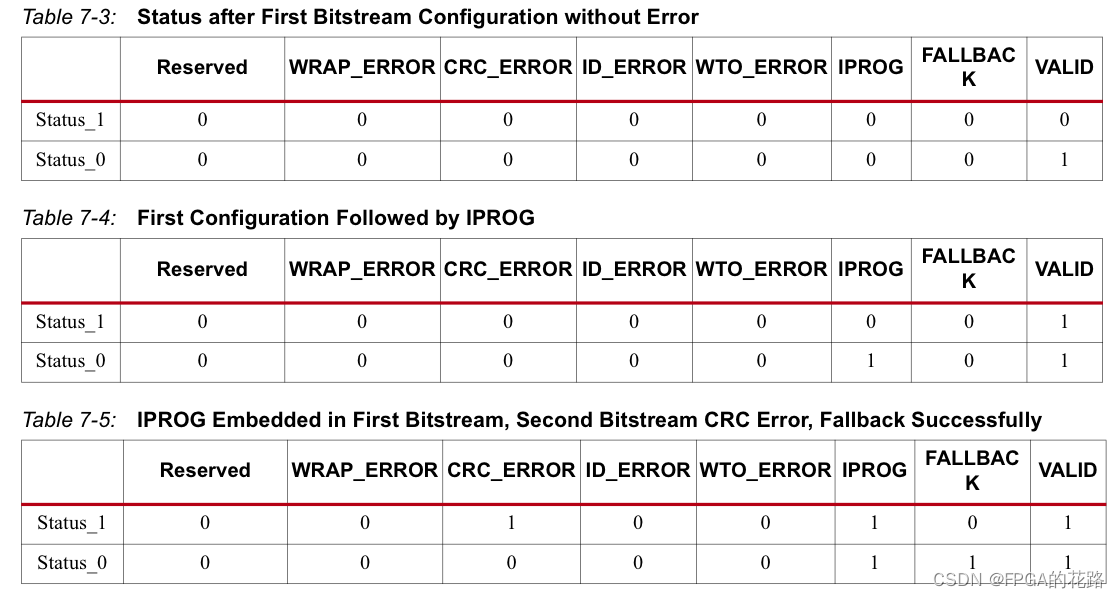

状态寄存器

- BOOTSTS 用于存储配置历史;

- Valid 用于只是当前 Status 是否有效;

- Status_0 用于记录最新配置状态; Status_1 用于记录上一次配置状态;

- Status_1 表示执行了 IPROG,检测到 CRC 错误;

- Status_0 表示回退加载成功,同时也有 IPROG,只是回退重配置忽略 IPROG 指令,但是同样记录状态

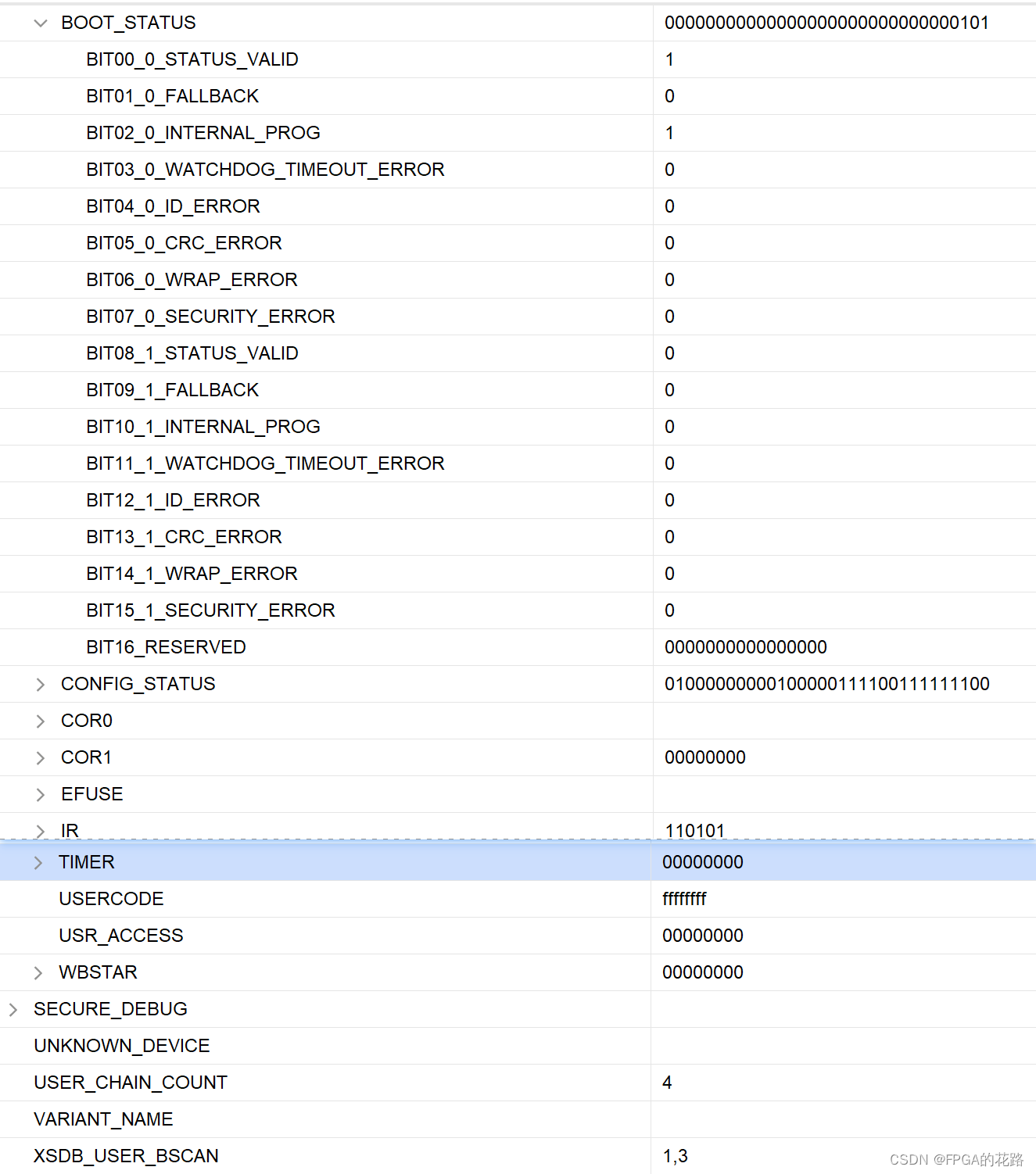

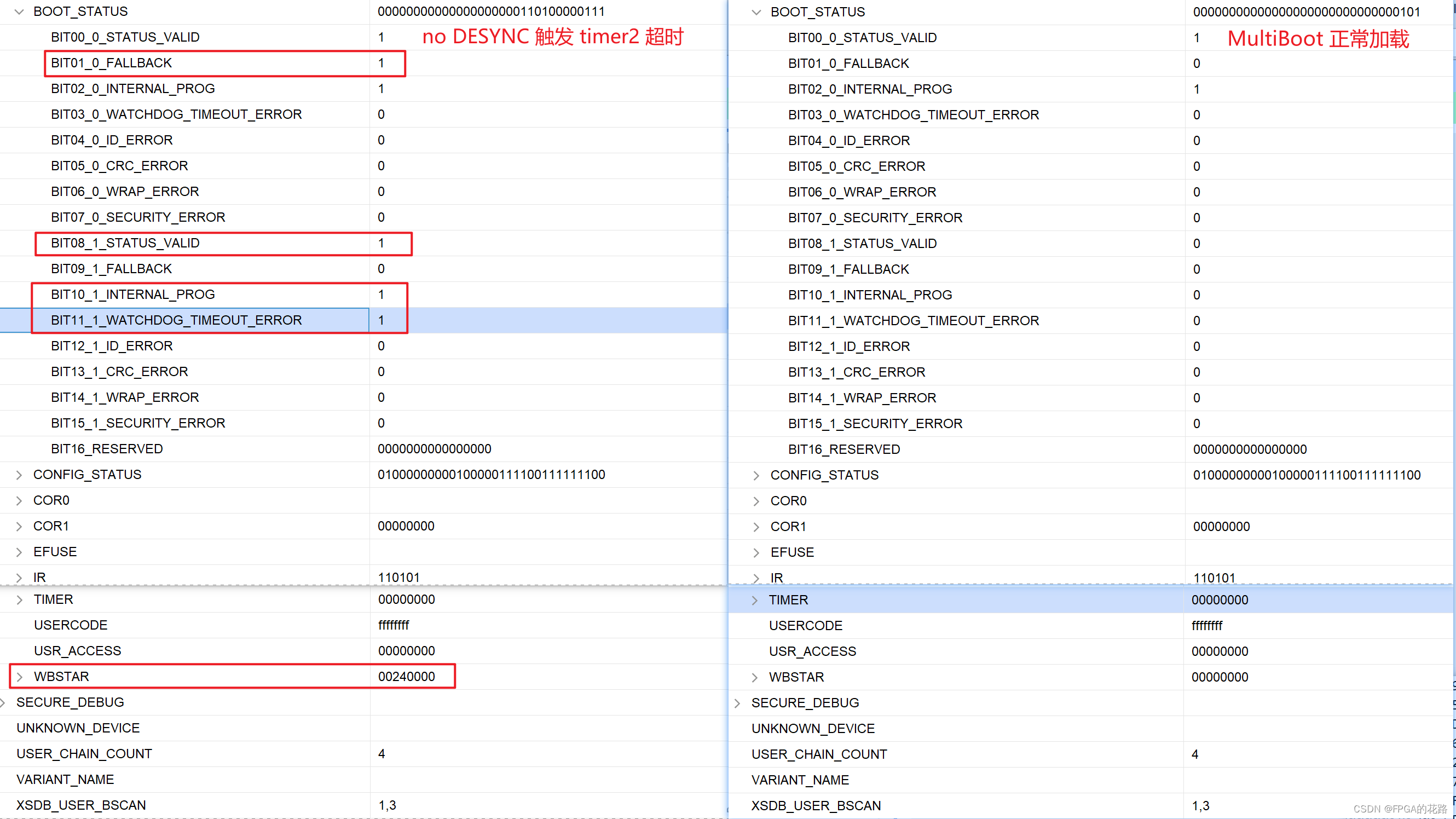

MultiBoot 正常加载状态

MultiBoot 正常加载,FPGA 加载 Update 程序。

状态寄存器如下所示:

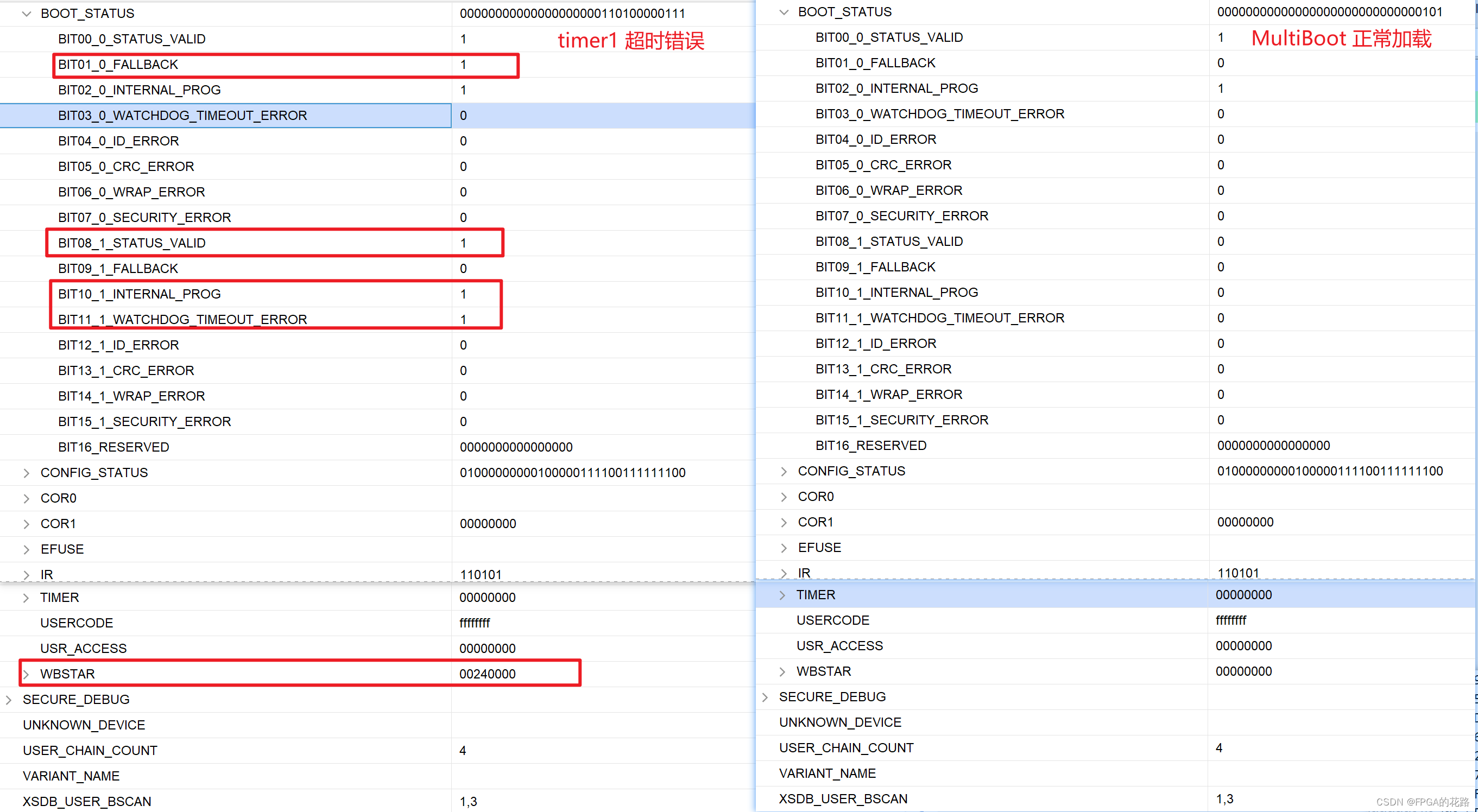

看门狗1超时状态

升级文件删除 update 部分,触发 timer1 超时错误 Fallback,FPGA 加载 Golden 程序。

状态寄存器如下所示:

看门狗2超时状态

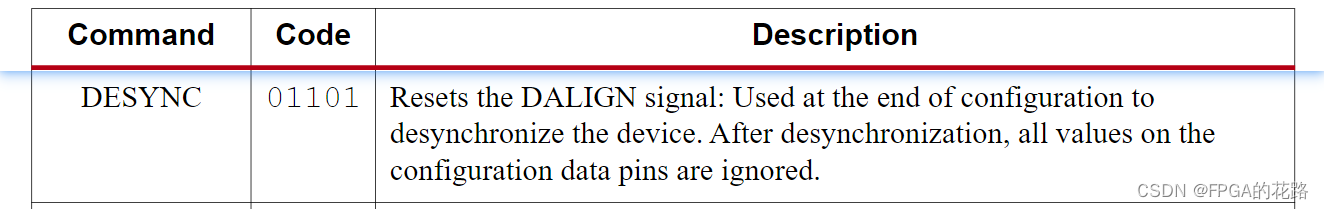

删除 update 部分的 DESYNC 命令,触发 timer2 超时错误 Fallback,FPGA 加载 Golden 程序。

状态寄存器如下所示:

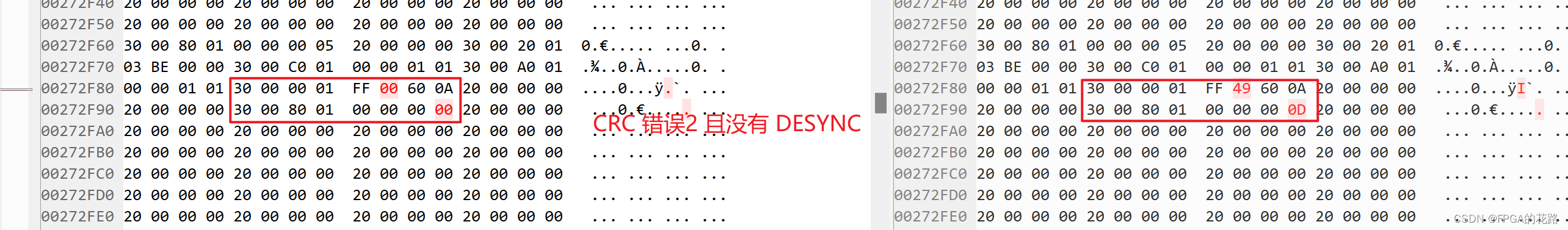

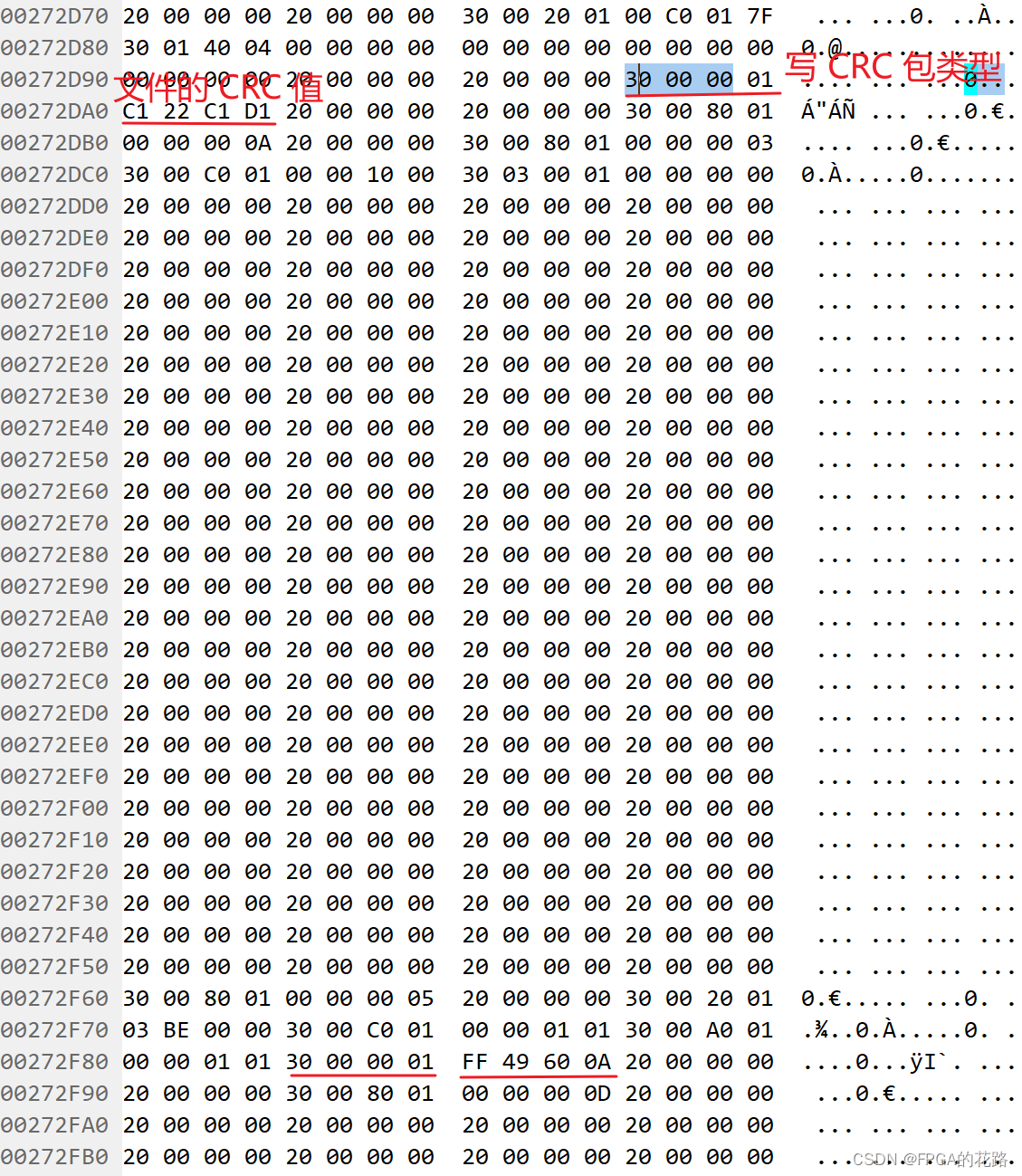

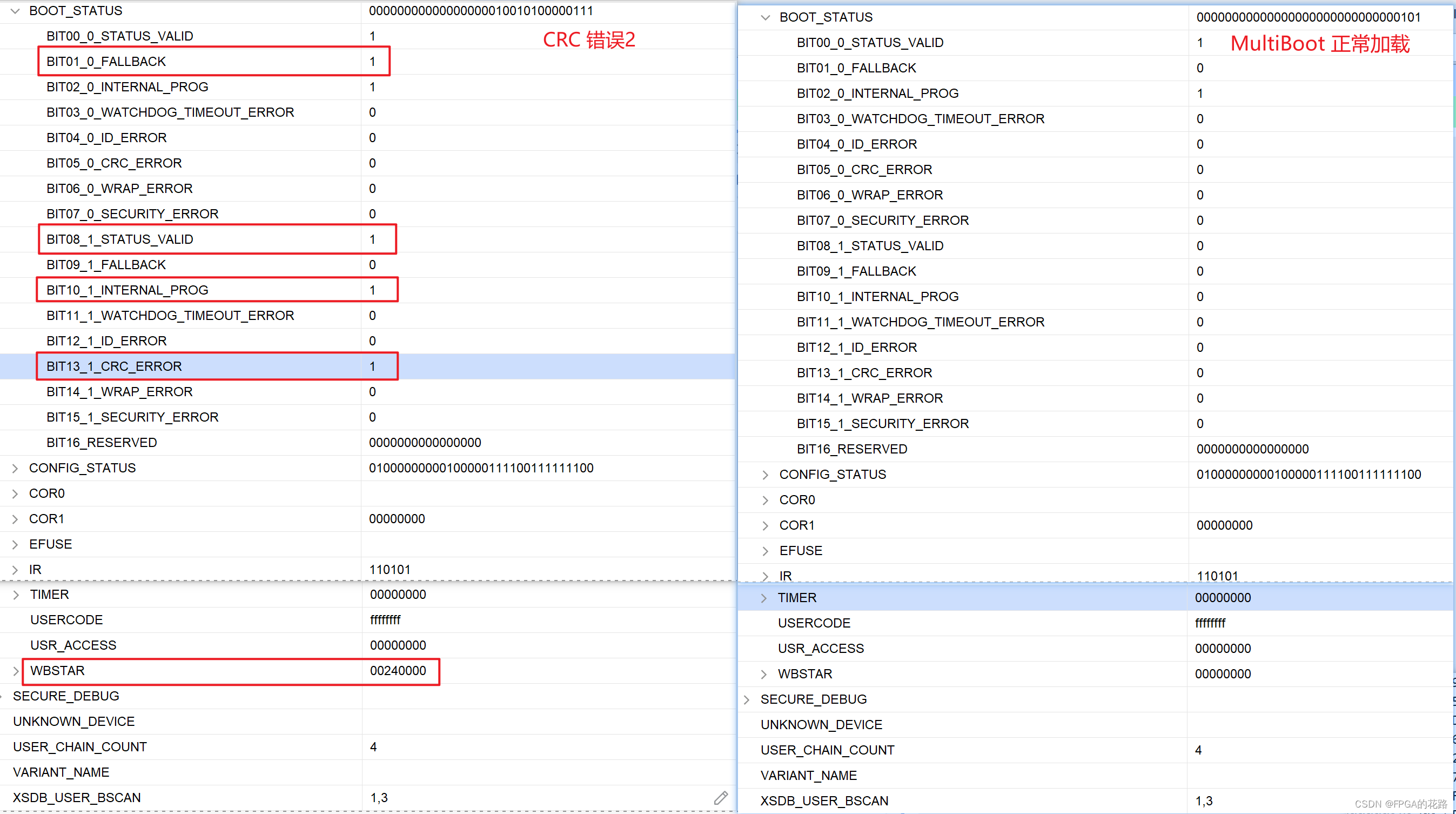

CRC 错误和无 DESYNC 命令

修改 Update 程序的写 CRC 寄存器值,并删除 update 部分的 DESYNC 命令,会先触发 CRC 错误 Fallback,FPGA 加载 Golden 程序。

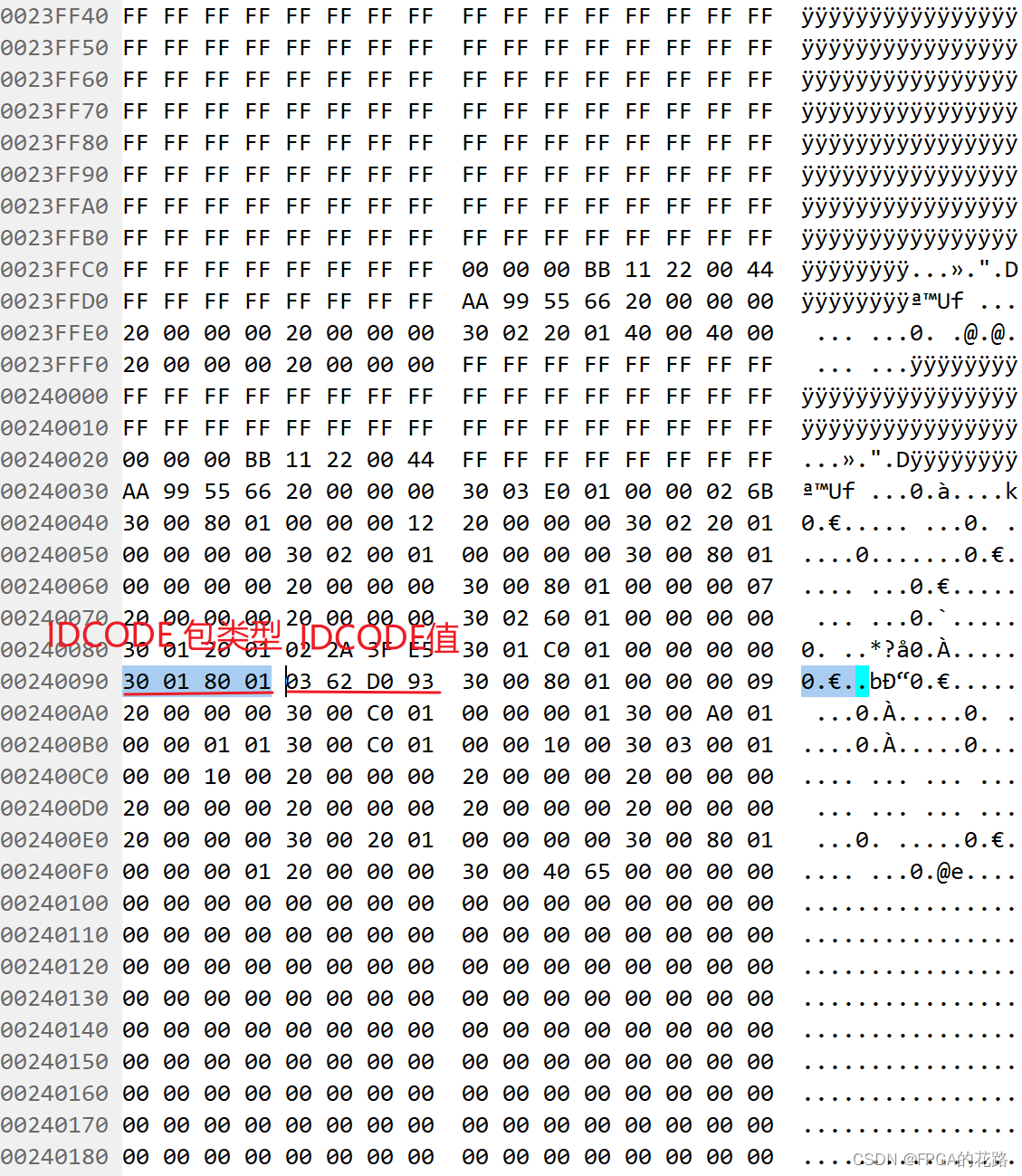

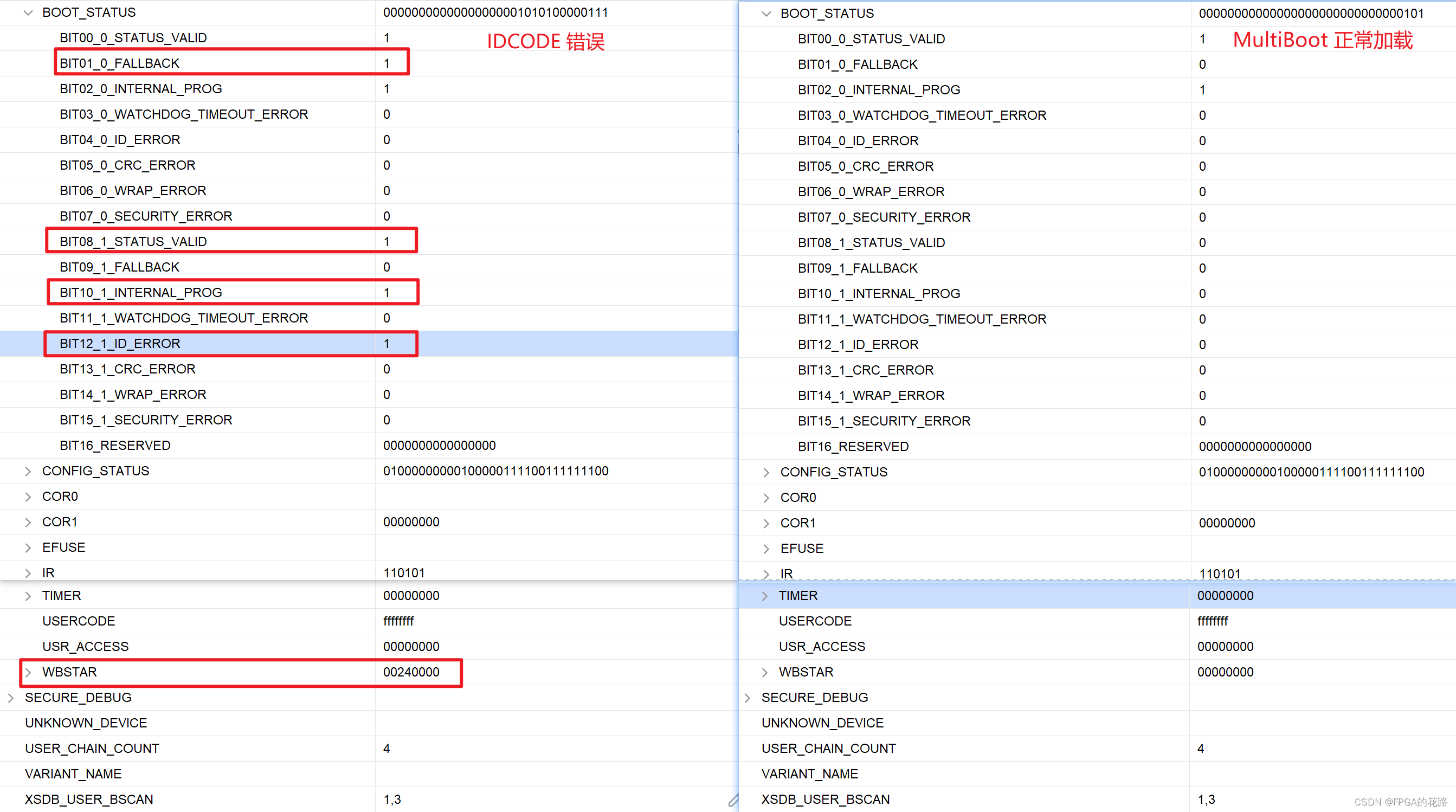

IDCODE 错误状态

修改 Update 程序的 IDCODE值,触发 IDCODE 错误 Fallback,FPGA 加载 Golden 程序。

状态寄存器如下所示:

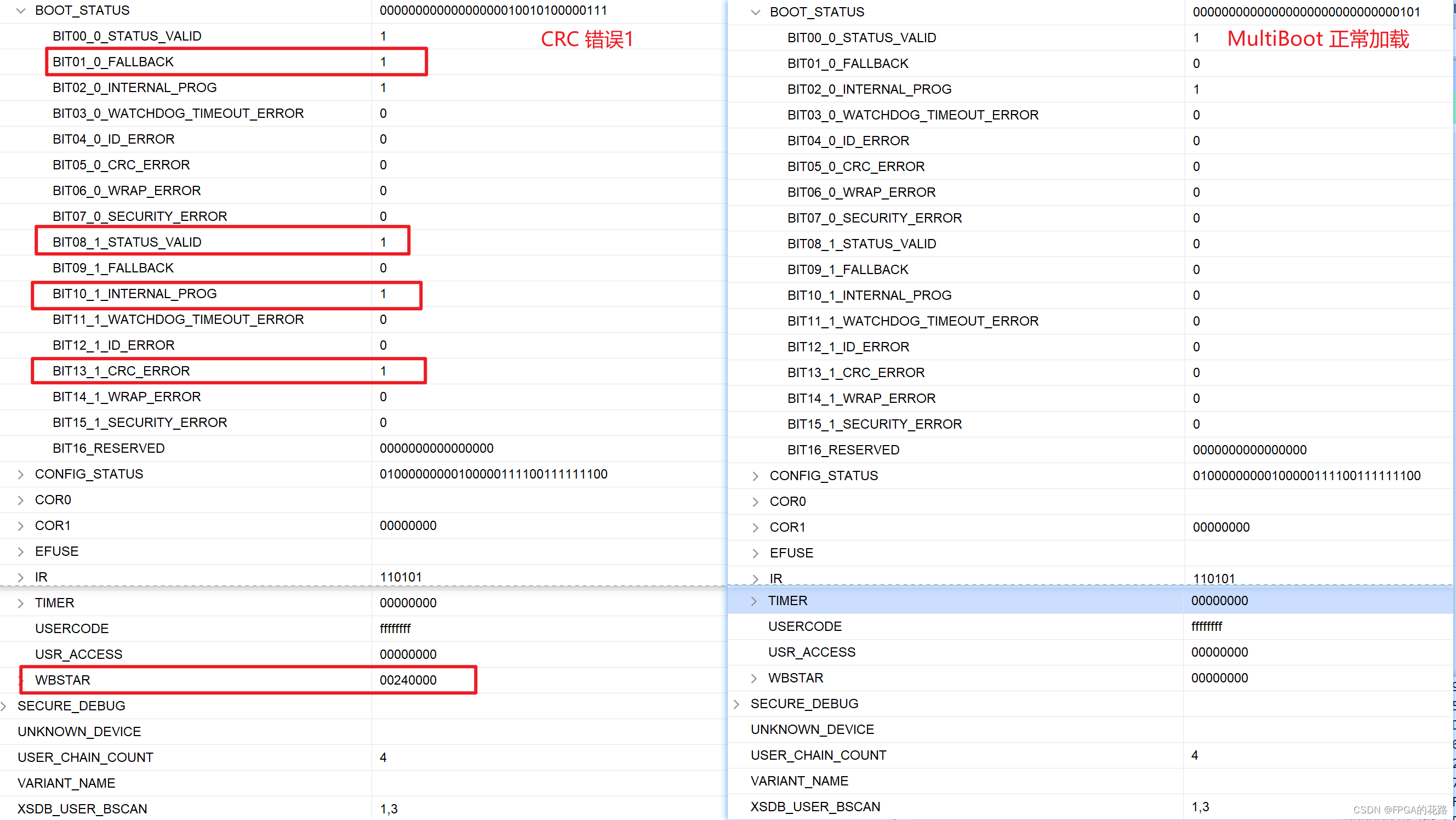

CRC 错误状态

FPGA 加载过程中会一直计算 CRC 值,收到最后一个数据后会跟写的 CRC 寄存器值进行比较,通过修改 Update 程序的写 CRC 寄存器值,触发 CRC 错误 Fallback,FPGA 加载 Golden 程序。

状态寄存器如下所示:

Watchdog Timer

xdc 约束设置看门狗定时器属性,定时器计时时钟为 CFGMCLK

set_property BITSTREAM.CONFIG.TIMER_CFG <Timer Value> [current_design]

下面有另一种方法实现看门狗定时器的功能,省去了需要计算精确的 TIMER_CFG 计时值。

使用 Timer 的工作流程

注:确保 golden、timer1、timer2 区域保持不变,升级只进行 update 区域更改。

- 执行 IPROG 命令,控制 FPGA 从 WBSTAR 指定的地址(Timer1 的位置)开始加载;

- 当 Timer1 后一直没有检测到同步头,则会触发 timer1 超时,进而触发 Fallback,然后加载 golden 程序;

- 当 update 程序正常加载,则 timer2 会被忽略;

- 当 update 程序最后缺少 DESYNC 命令,则会加载到 timer2 区域,然后触发 timer2 超时,进而触发 Fallback,然后加载 golden 程序。

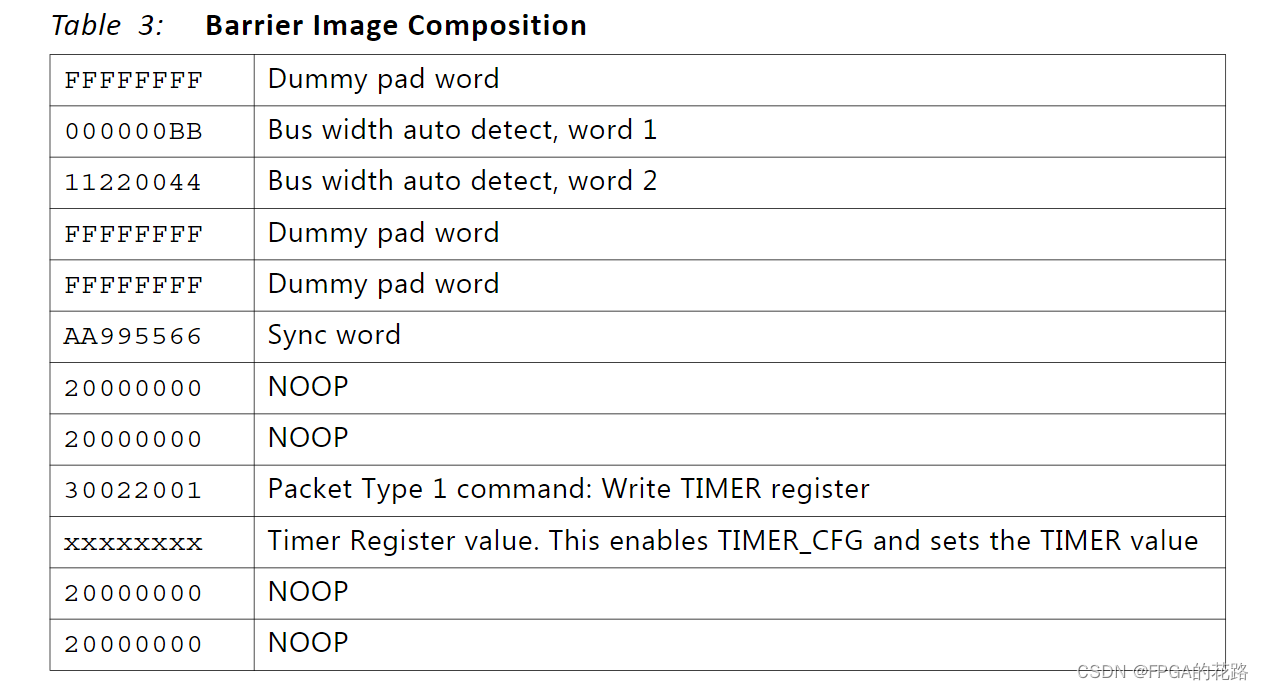

timer1 和 timer2 数据格式

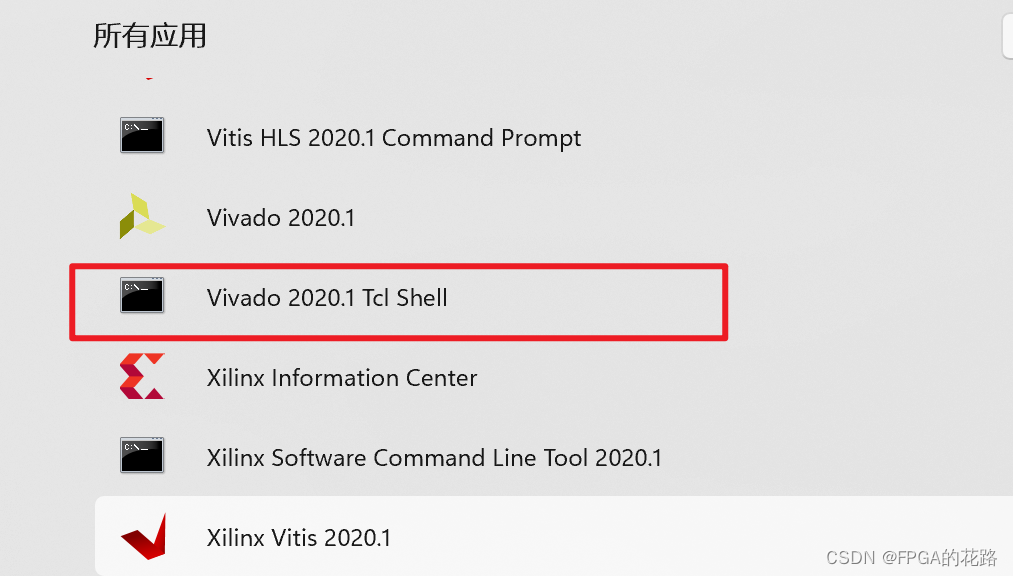

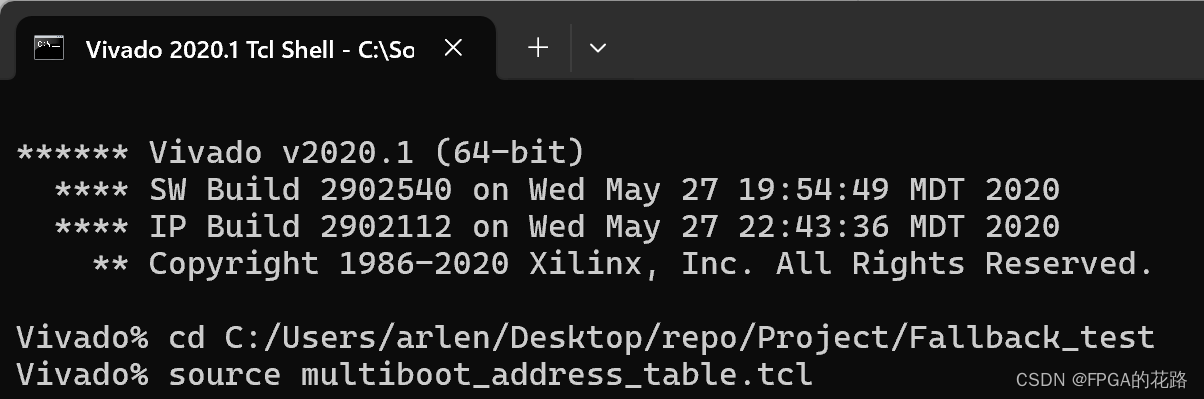

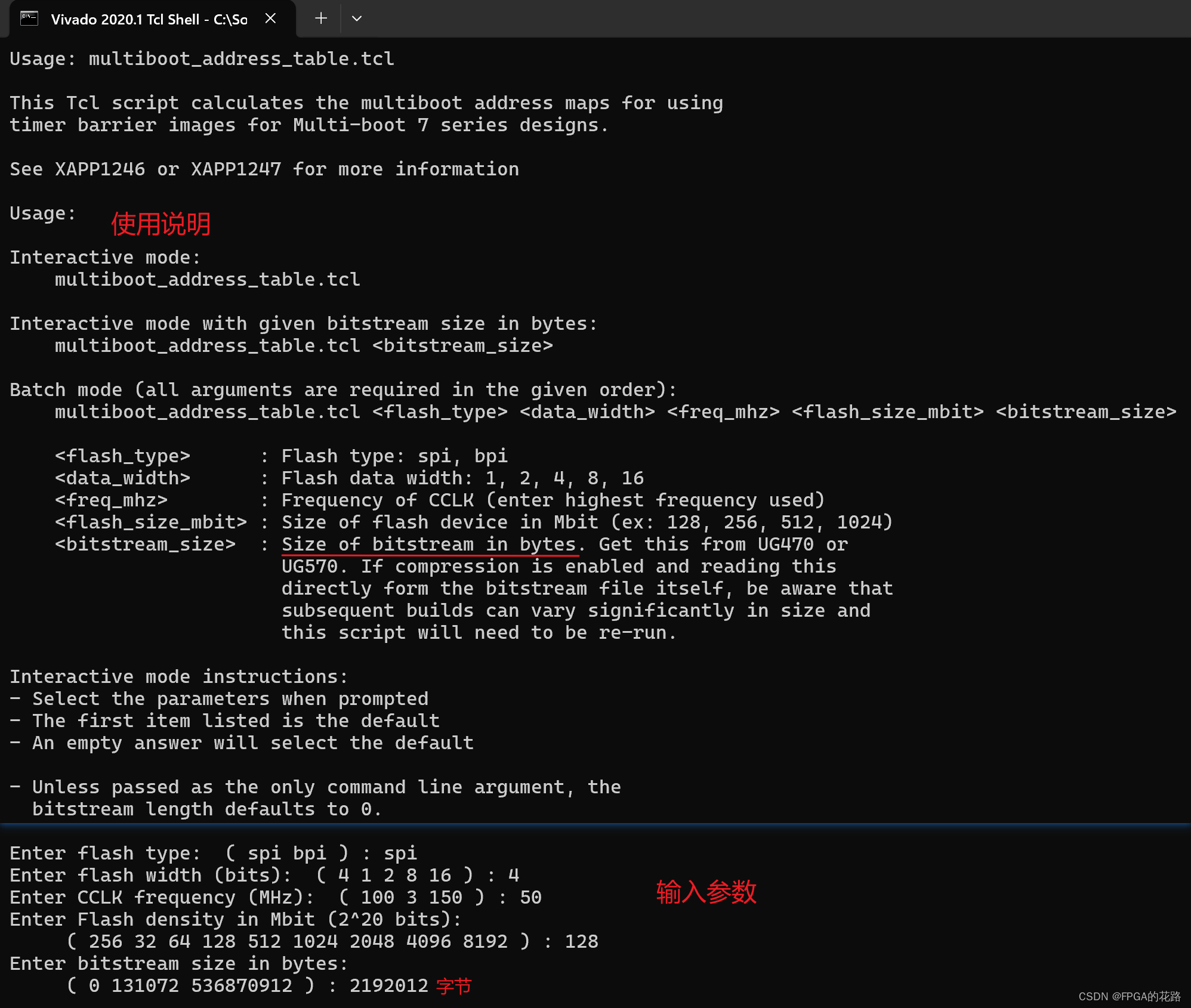

通过 Tcl 指令生成程序文件

- 打开 Vivado Tcl Shell

- 切换到 multiboot_address_table.tcl 文件所在目录

cd C:/Users/arlen/Desktop/repo/Project/Fallback_test

- 运行 multiboot_address_table.tcl 文件

source multiboot_address_table.tcl

- 输入参数

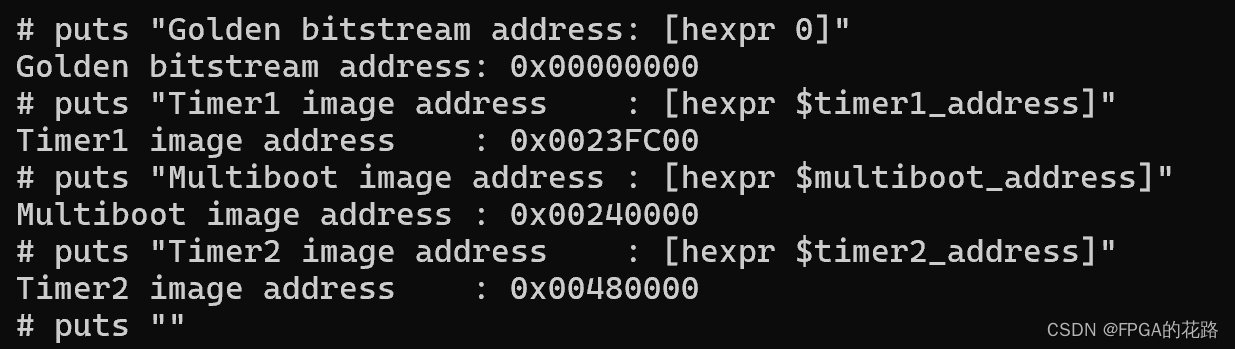

- 生成地址信息、timer1.bin、timer2.bin

- golden 添加如下 bitstream 属性约束

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x00240000 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 1 [current_design]

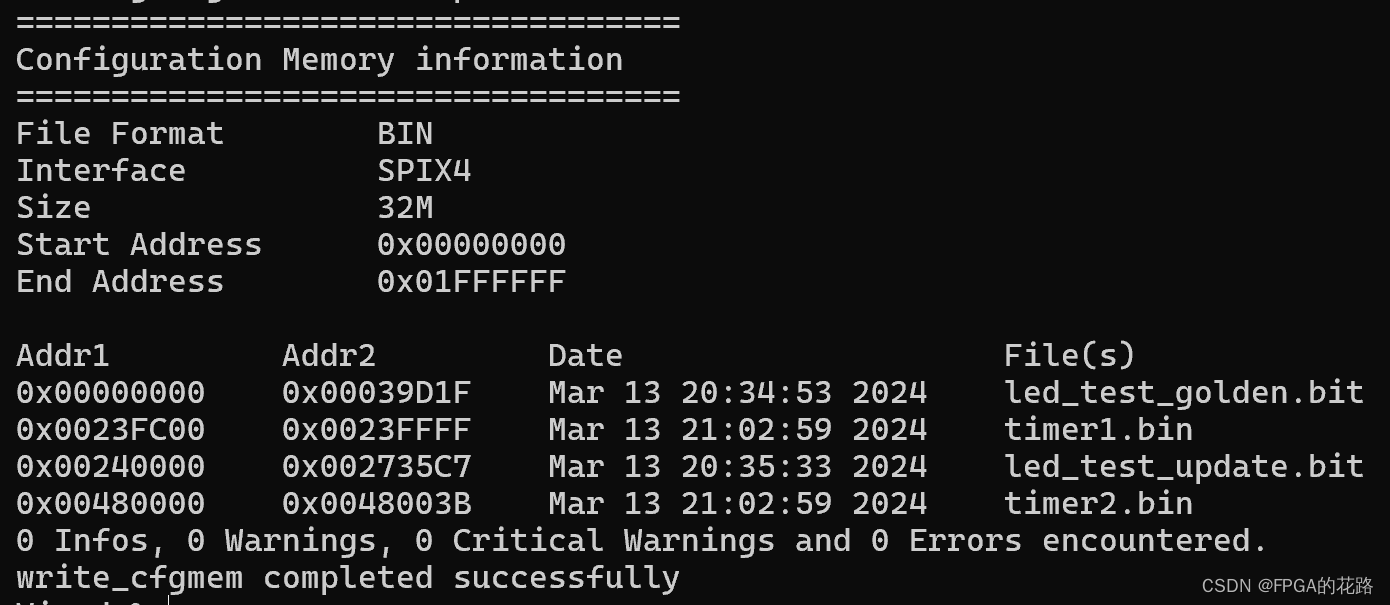

- 将 golden.bit、update.bit、timer1.bin、timer2.bin 放在一个文件夹,运行以下命令

## 生成 mcs 文件

write_cfgmem -force -format mcs -size 32 -interface SPIx4 -loadbit {up 0x00000000 led_test_golden.bit up 0x00240000 led_test_update.bit} -loaddata {up 0x0023FC00 timer1.bin up 0x00480000 timer2.bin} multiboot_normal.mcs

## 生成 bin 文件

write_cfgmem -force -format bin -size 32 -interface SPIx4 -loadbit {up 0x00000000 led_test_golden.bit up 0x00240000 led_test_update.bit} -loaddata {up 0x0023FC00 timer1.bin up 0x00480000 timer2.bin} multiboot_normal.bin

write_cfgmem -force -format bin -size 32 -interface SPIx4 -loaddata {up 0x00000000 led_test_golden.bin up 0x00240000 led_test_update_no_fallback.bin up 0x0023FC00 timer1.bin up 0x00480000 timer2.bin} multiboot_update_no_fallback.bin

- 生成结果窗口打印信息

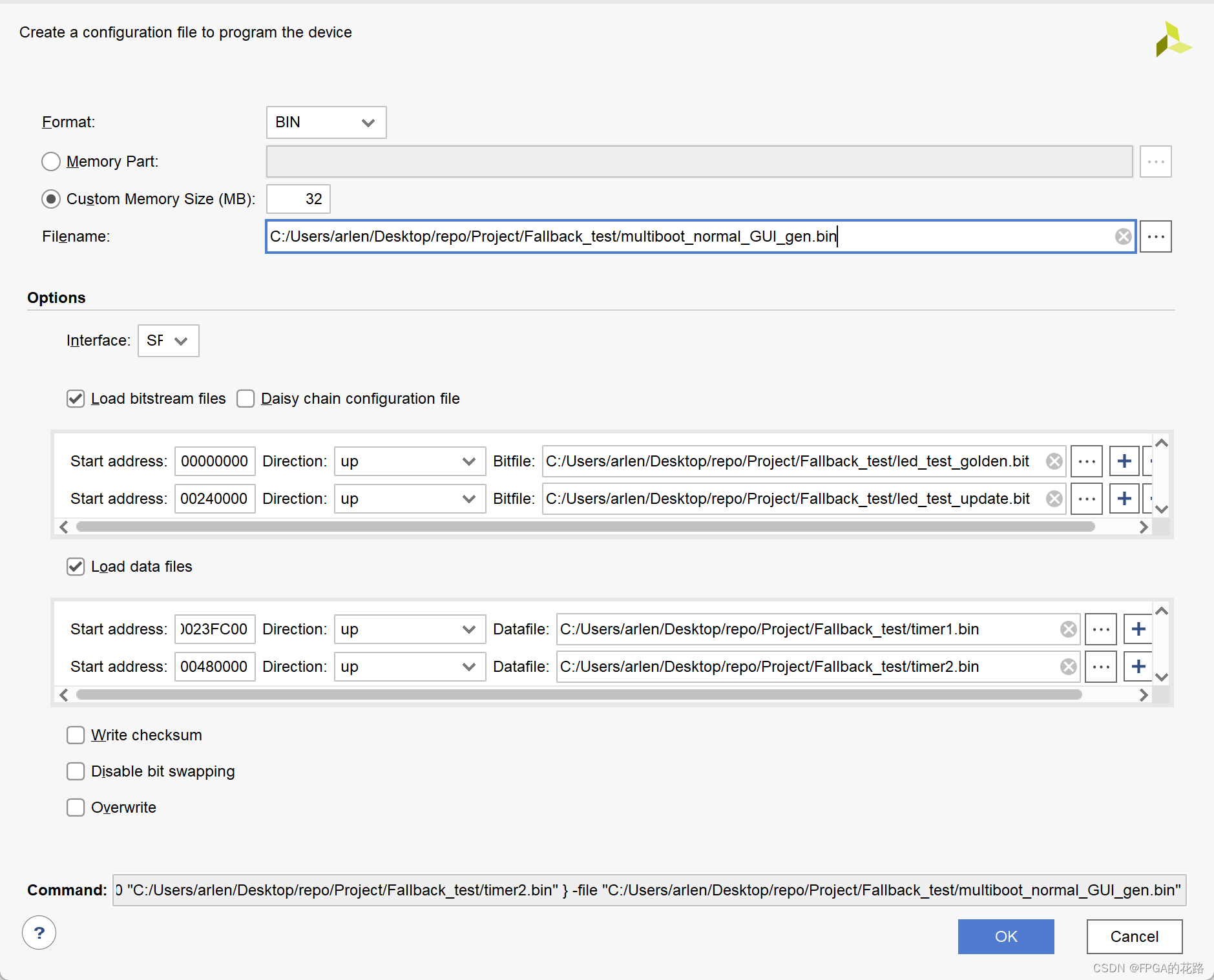

通过 Vivado GUI 生成

对应 Tcl 指令

write_cfgmem -format bin -size 32 -interface SPIx4 -loadbit {up 0x00000000 "C:/Users/arlen/Desktop/repo/Project/Fallback_test/led_test_golden.bit" up 0x00240000 "C:/Users/arlen/Desktop/repo/Project/Fallback_test/led_test_update.bit" } -loaddata {up 0x0023FC00 "C:/Users/arlen/Desktop/repo/Project/Fallback_test/timer1.bin" up 0x00480000 "C:/Users/arlen/Desktop/repo/Project/Fallback_test/timer2.bin" } -file "C:/Users/arlen/Desktop/repo/Project/Fallback_test/multiboot_normal_GUI_gen.bin"

QuickBoot

支持 4 种配置模式

- SPI mode

- BPI mode

- Encrypted bitstreams

- Multiple FPGA configuration daisy-chains

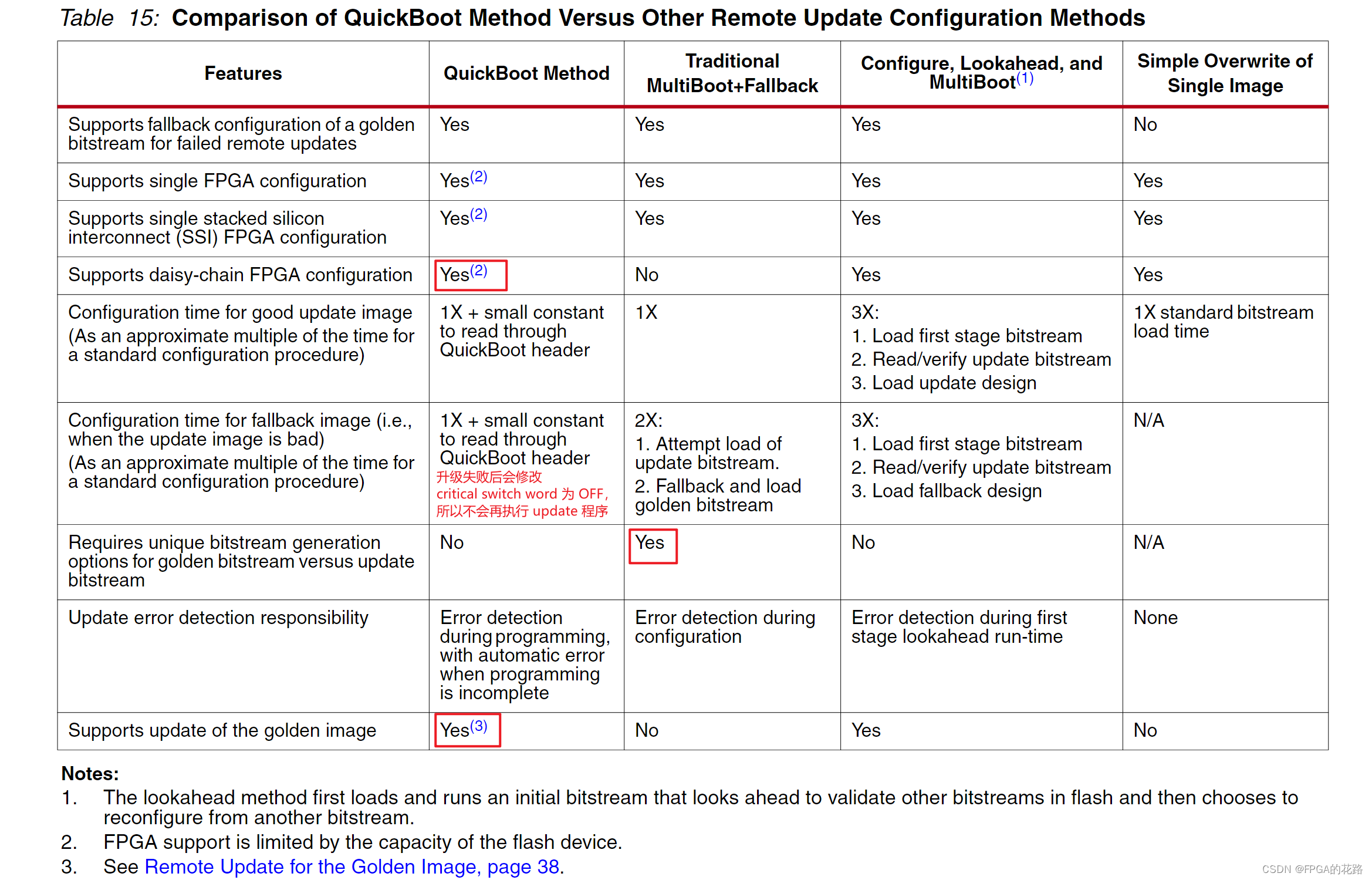

传统 MultiBoot 远程升级方式

MultiBoot 的两个程序都需包含 warm boot jump sequence,warm boot jump sequence 包含 WBSTRA(用于指定程序加载地址)、IPROG(用于重启 FPGA 配置并从 WBSTAR 指定的地址开始加载)

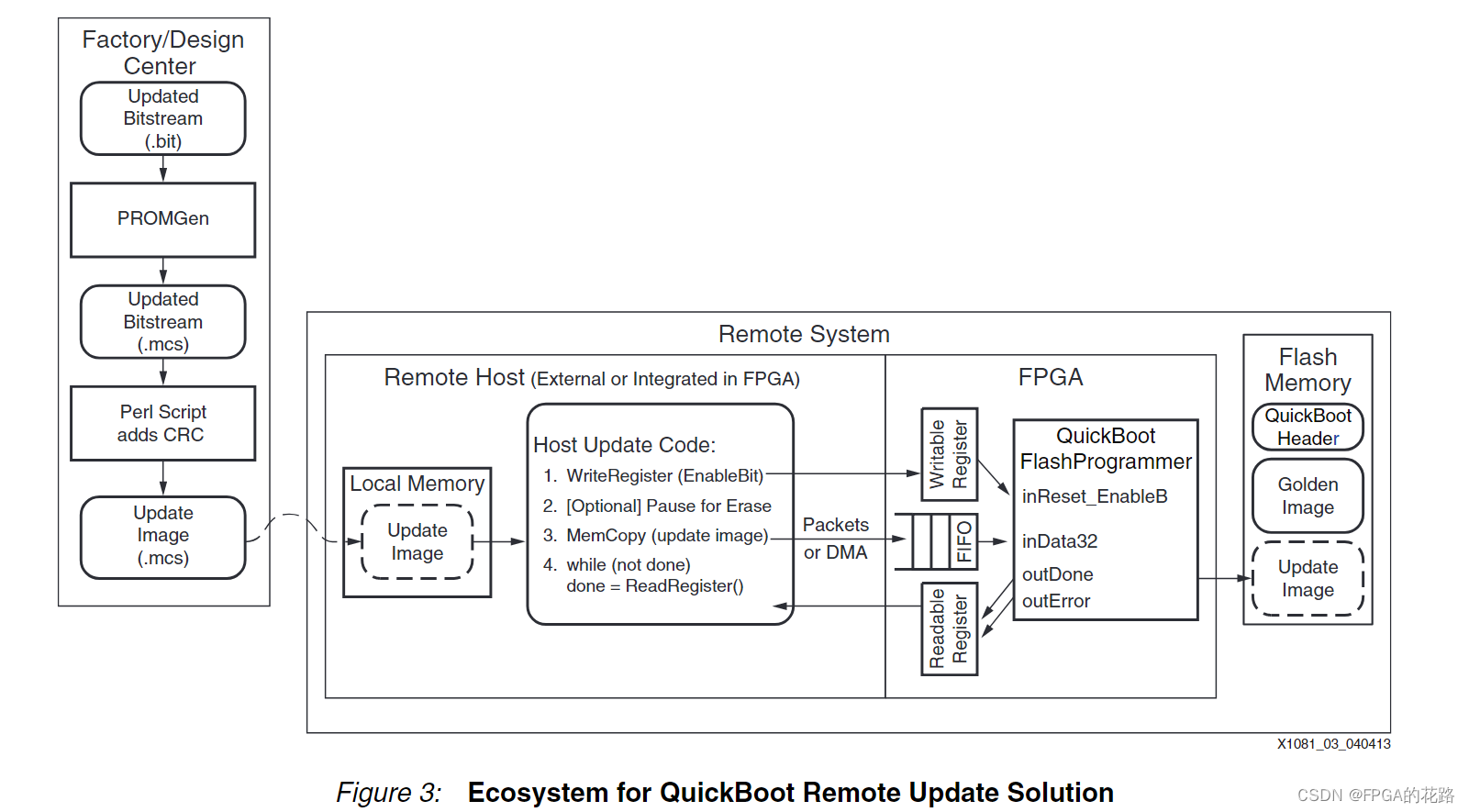

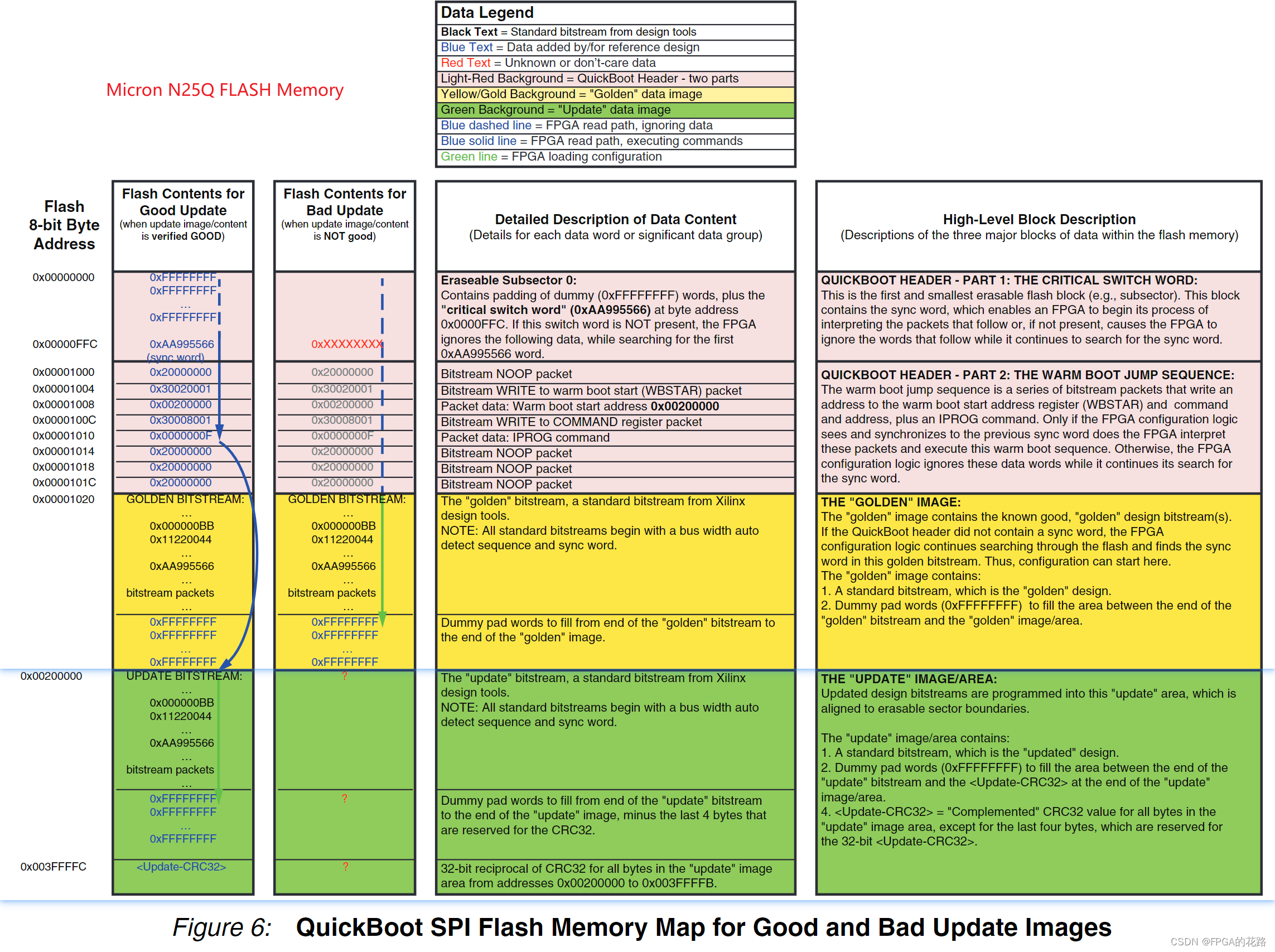

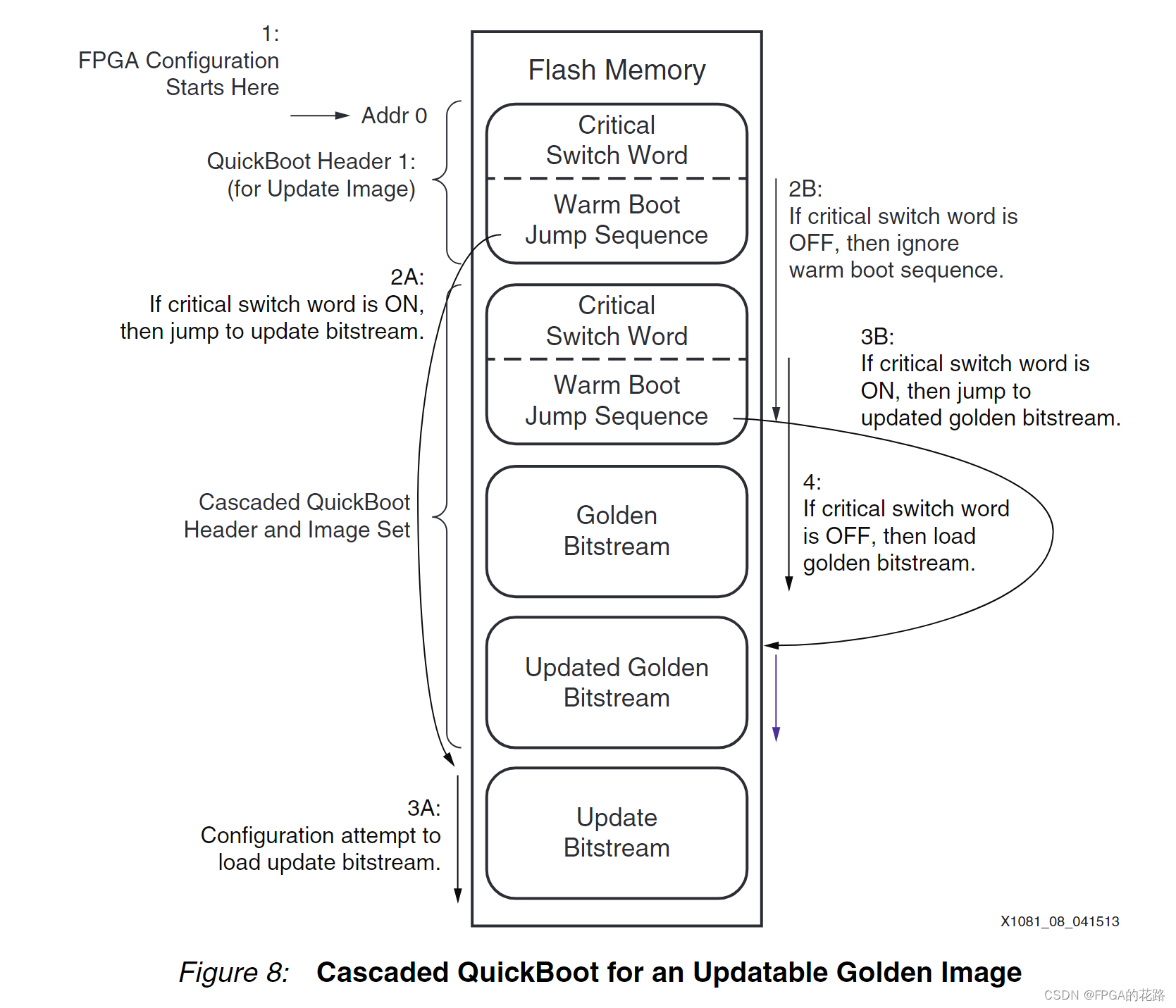

QuickBoot 远程升级方式

系统架构

升级程序组成

QuickBoot 程序包含 3 部分

-

QuickBoot header

-

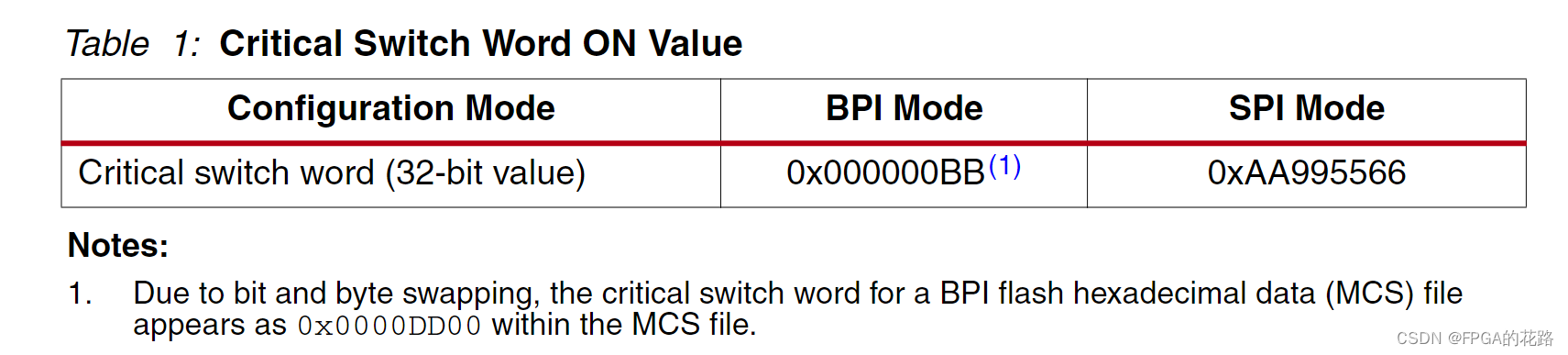

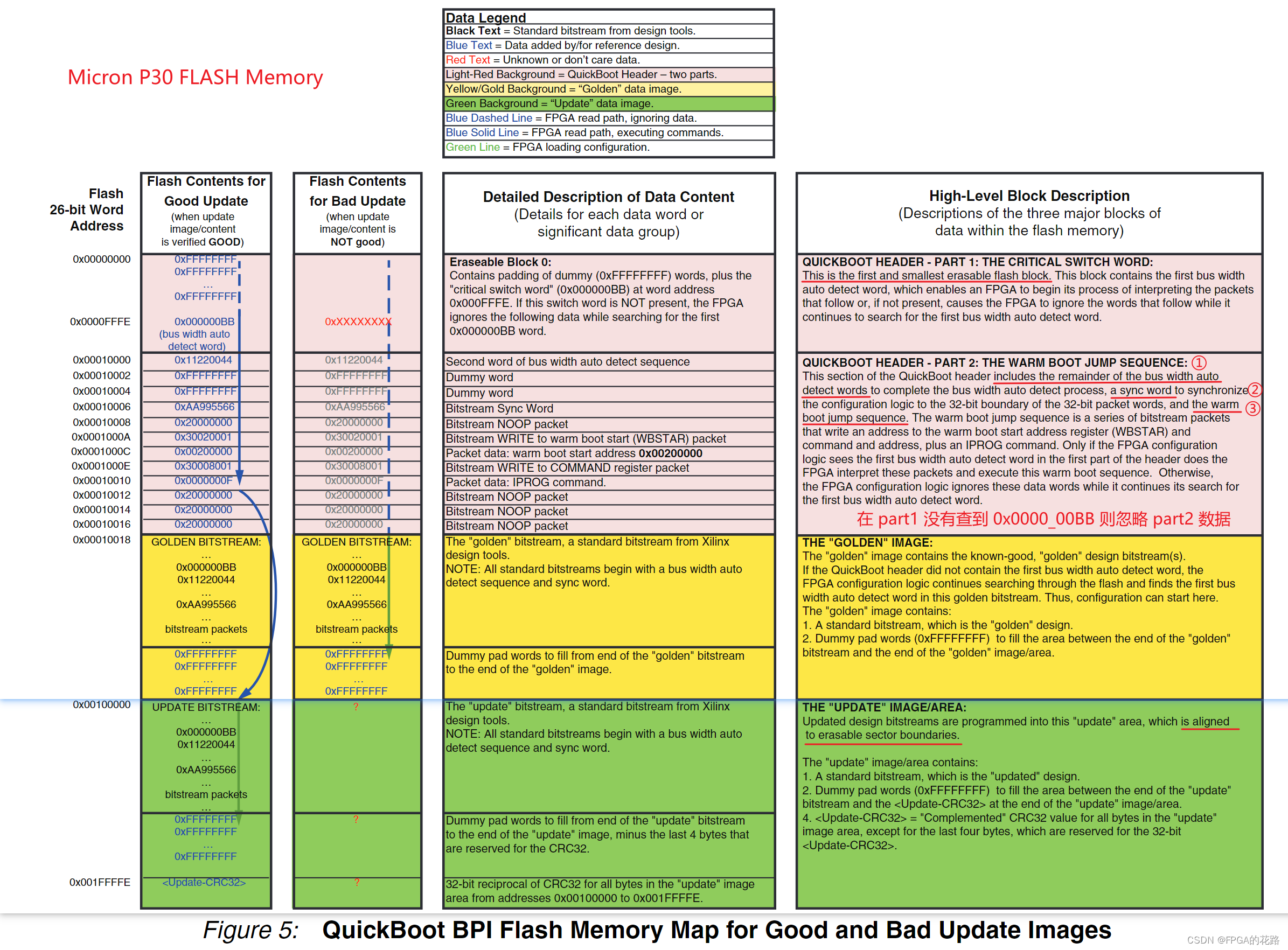

critical switch word:用于指示 FPGA 是否执行 warm boot jump sequence

-

warm boot jump sequence:包含 WBSTRA(用于指定程序加载地址)、IPROG(用于重启 FPGA 配置并从 WBSTAR 指定的地址开始加载)

-

-

golden bitstream image area

-

update bitstream image area

升级步骤

QuickBoot 远程升级步骤

- 先修改 critical switch word 值为 OFF;

- 进行 update 程序烧写;

- 回读校验 update 程序是否烧写正确,若正确则修改 critical switch word 值为 ON。

注:golden 和 QuickBoot hear 的第二部分内容 (warm boot jump sequence) 都不允许更改

写 NOR Flash 步骤

- 将要进行写操作的 segment 进行擦除操作,变为 1 状态;

- 将写数据中的 0 写入 Flash

Bitstream 在 flash 中的位置(要适配 flash 最小擦除单位 segment)

- QuickBoot header

- critical switch word:第 1 个 segment

- warm boot jump sequence:第 2 个 segment

- gloden bitstream image:跟在 warm boot jump sequence 后面

- update bitstream image:跟在 golden 后面,但是不能跟 golden 共用一个 segment

BPI Flash Memory Map (Micron P30)

SPI Flash Memory Map (Micron N25Q)

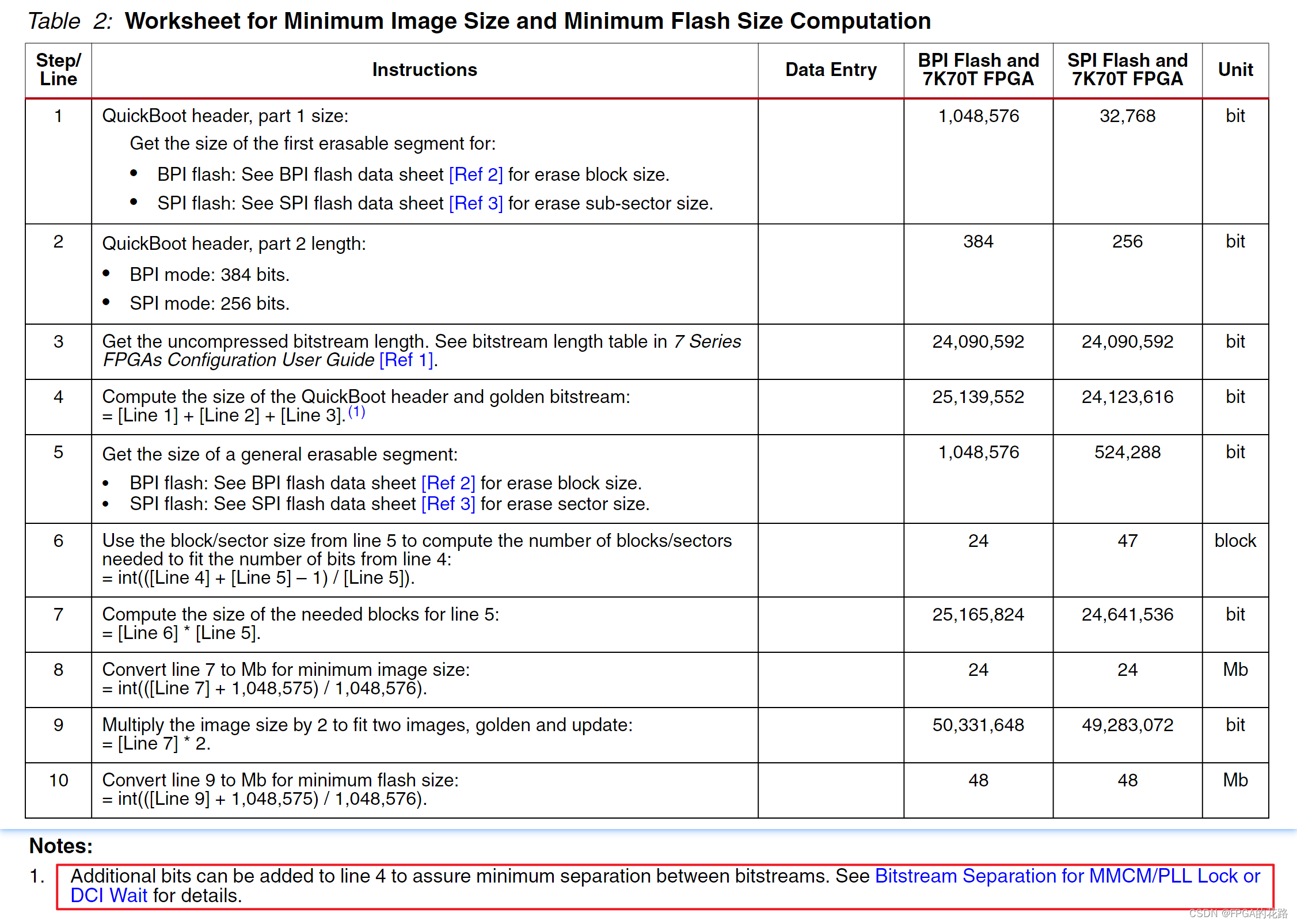

Bitstream 及 FLASH 大小计算

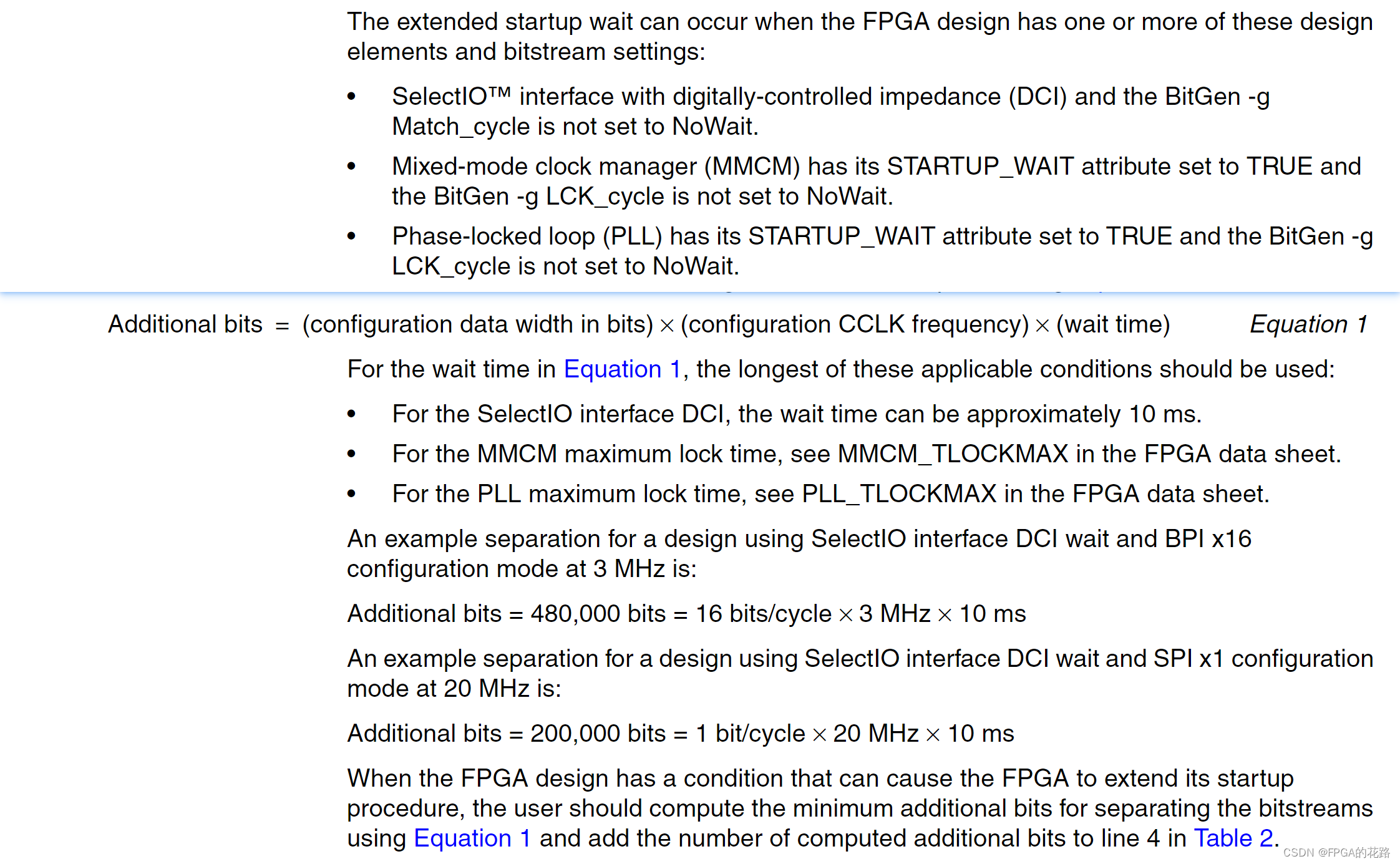

Bitstream Separation for MMCM/PLL Lock or DCI Wait

FLASH 中的两个 bitstream 间要填充足够的数据,保证第一个程序加载完之前不会加载到下个 bitstream 的数据。

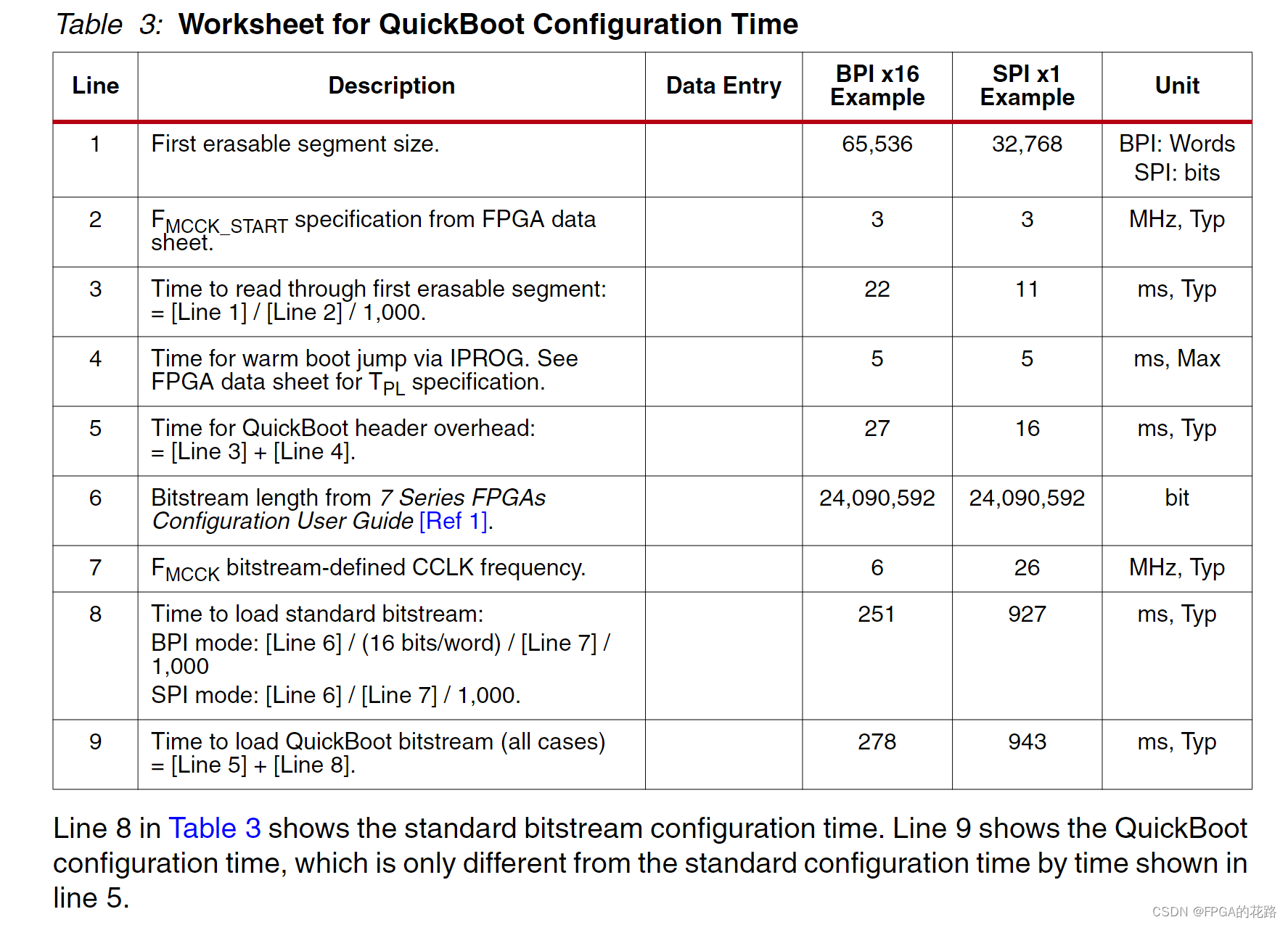

QuickBoot Configure Time

参考设计

BPI

BpiFlashProgrammer.vhd is the programming state machine that implements the QuickBoot programming algorithm for BPI flash. The BpiFlashProgrammer interfaces directly with the BPI flash.

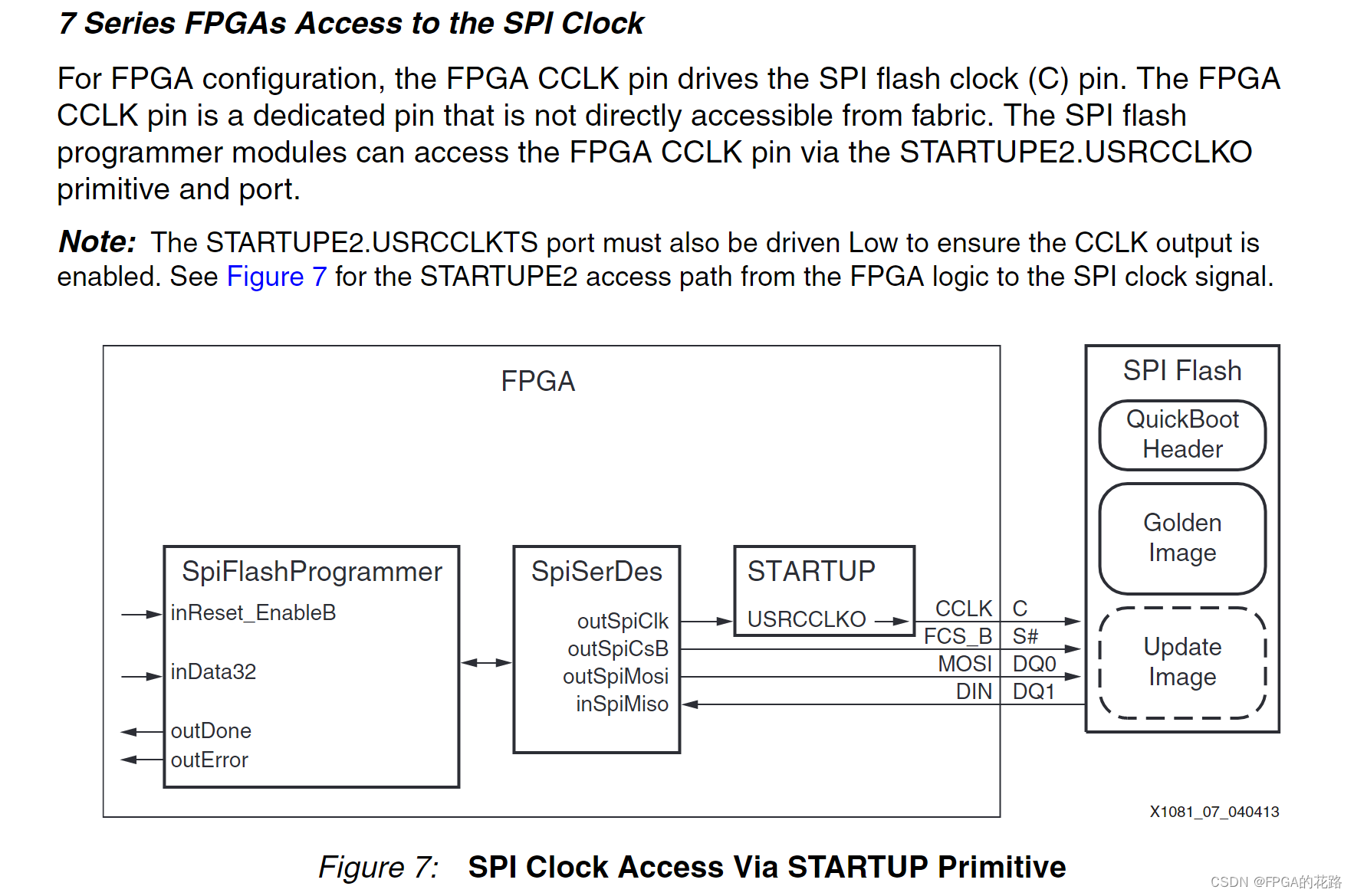

SPI

-

SpiFlashProgrammer.vhd: QuickBoot flash programmer state machine for SPI flash

-

SpiSerDes.vhd: Serializer/deserializer interface to the SPI bus

更快进行 QuickBoot 加载的方法

第 1 个 segment 为 warm boot jump sequence,跳转地址为第 2 个 segment 的最后一个 word (critical switch word),这样可以节省读完第一个 segment 的时间。

可进行 Golden Image 升级的方法

远程升级方式对比

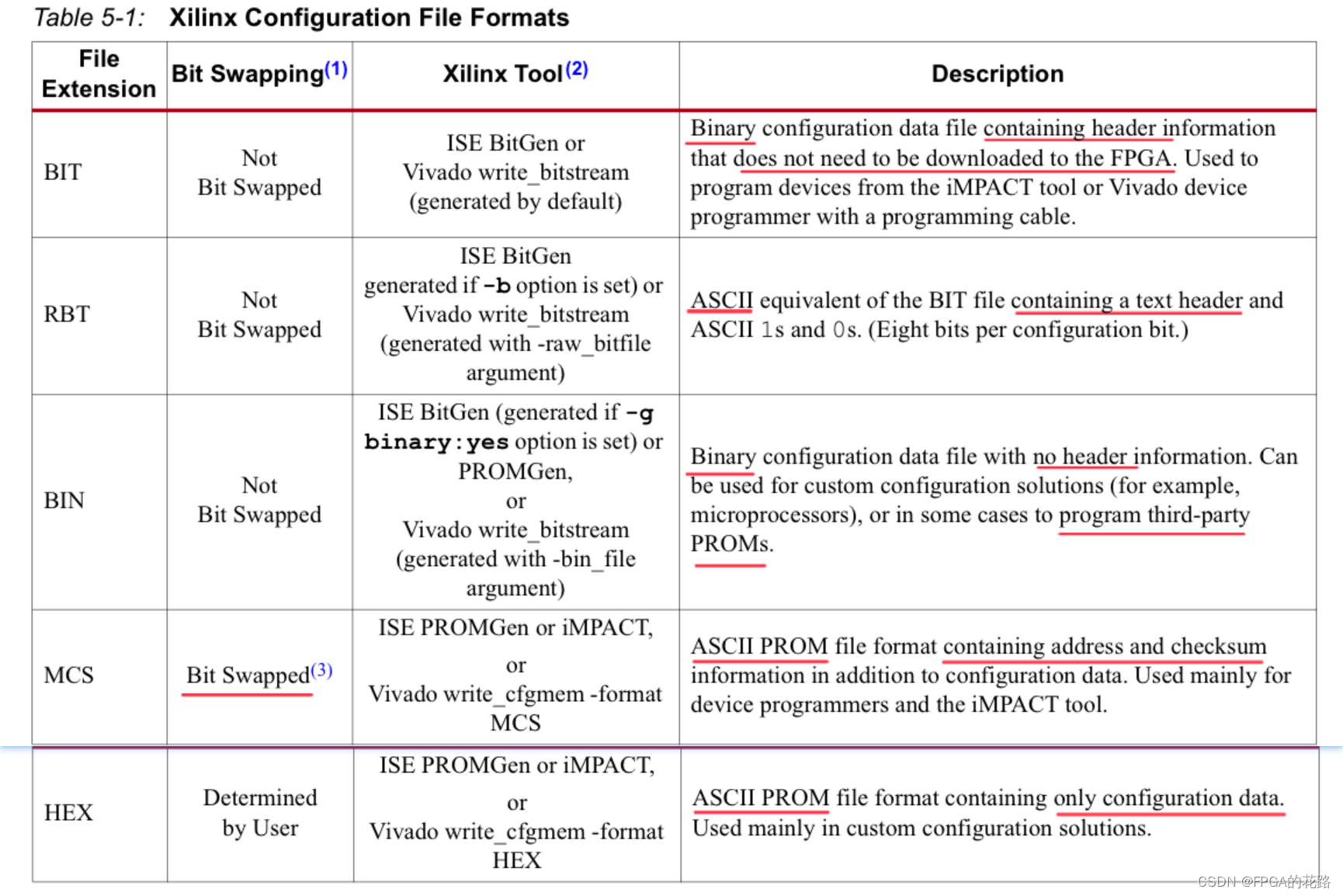

配置文件格式

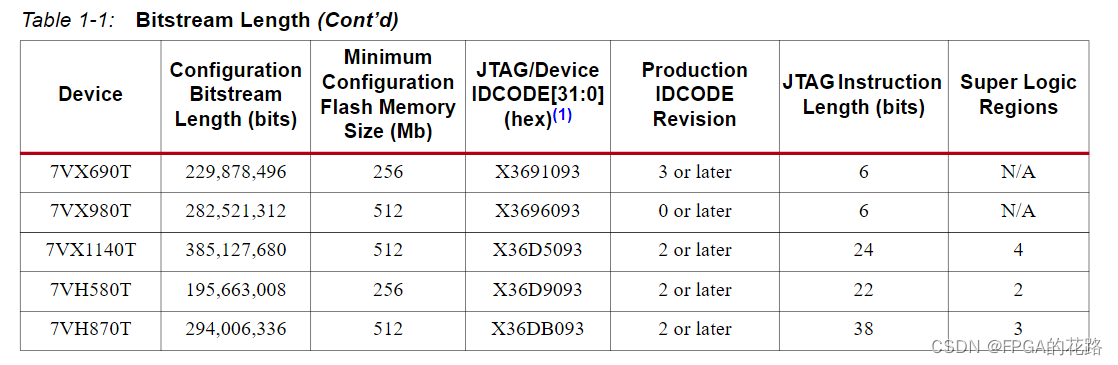

7 系列 bitstream 大小

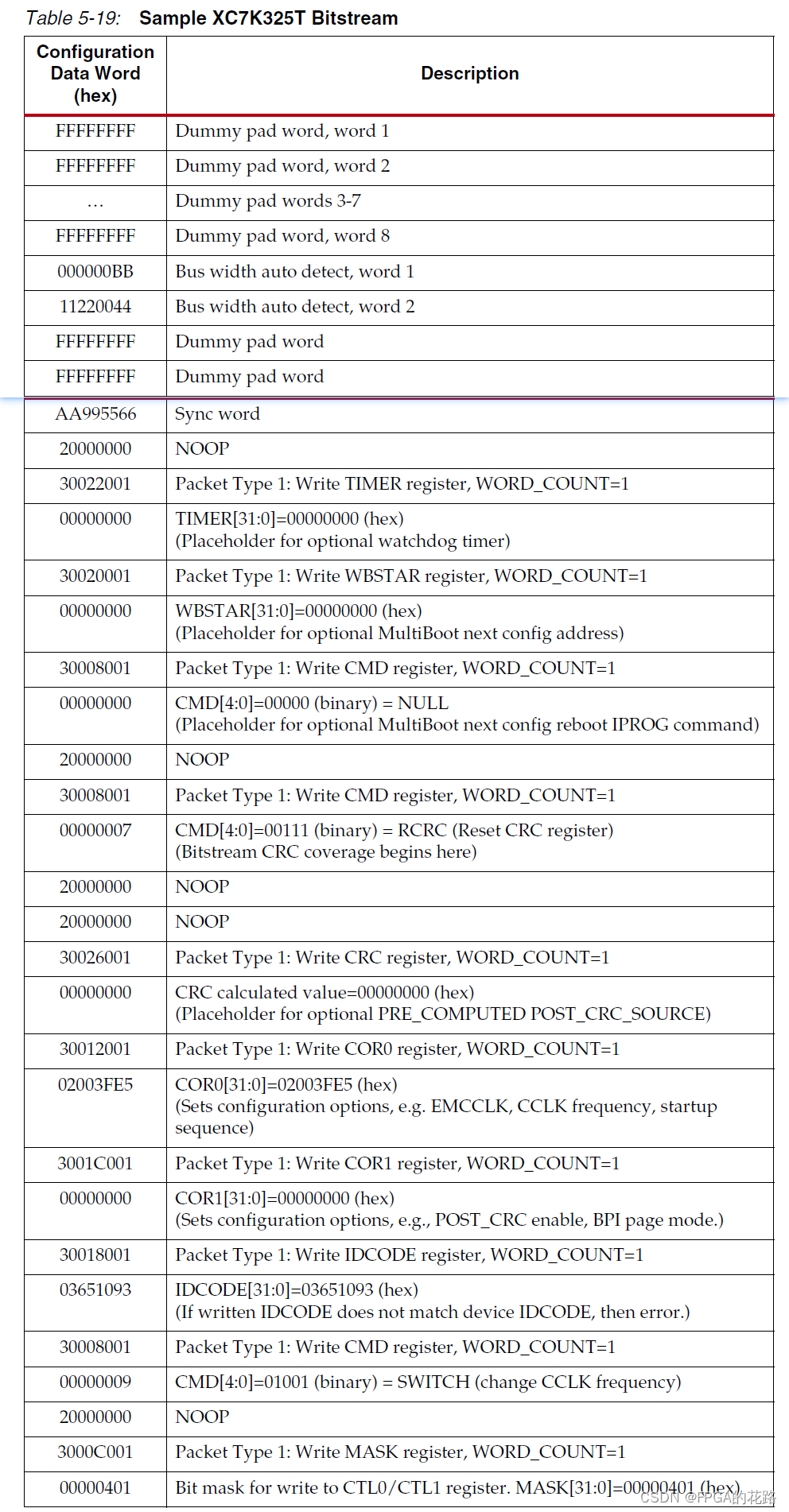

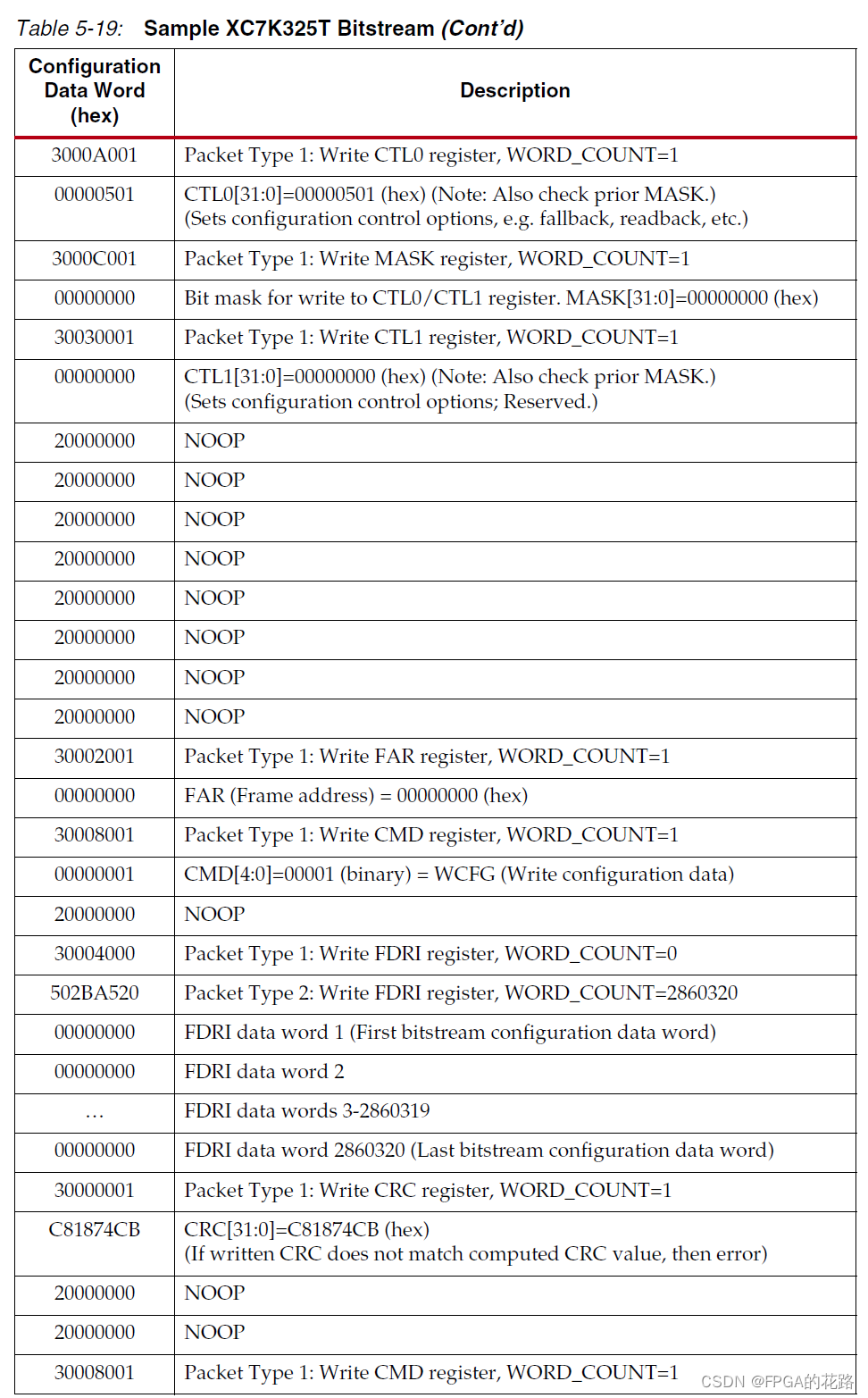

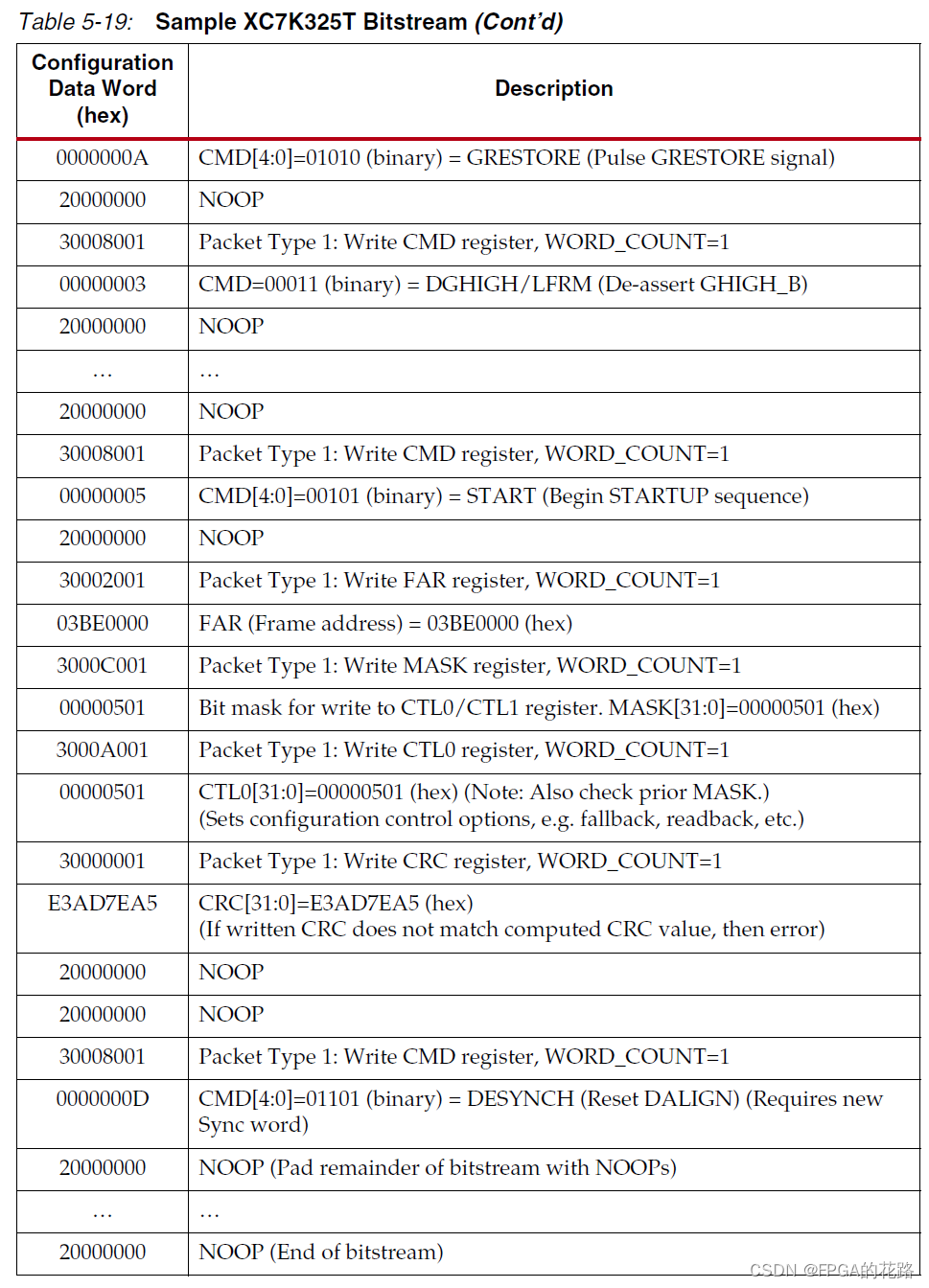

7 系列 bitstream 格式

Bitstream 组成

bitstream文件中的字类型

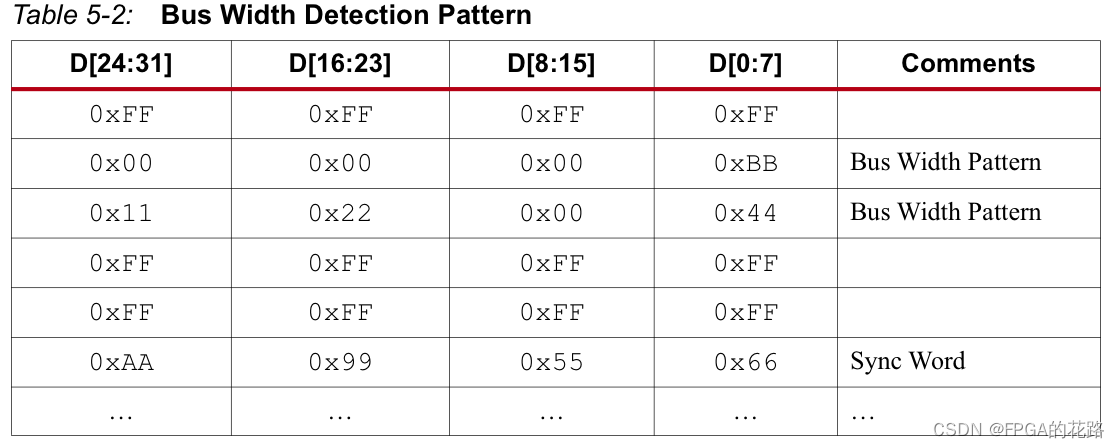

- Bus width auto detection word:只存在于 BPI 、SelectMAP 配置模式下的文件头

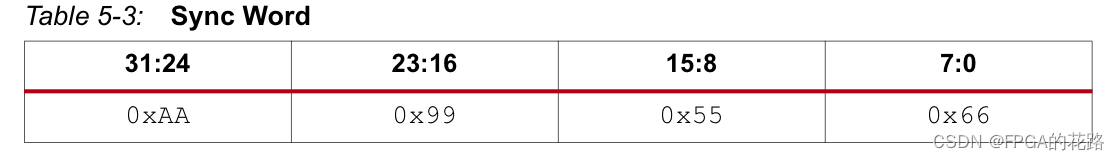

- Sync word:32-bit 边界同步

- Packet header:描述写寄存器的寄存器地址和待写数据的字计数

- Packet command or data words:命令字或者数据字内容

Xilinx design tools 生成的 bitstream 包含:

- bus width auto detection words

- sync word

- data packets

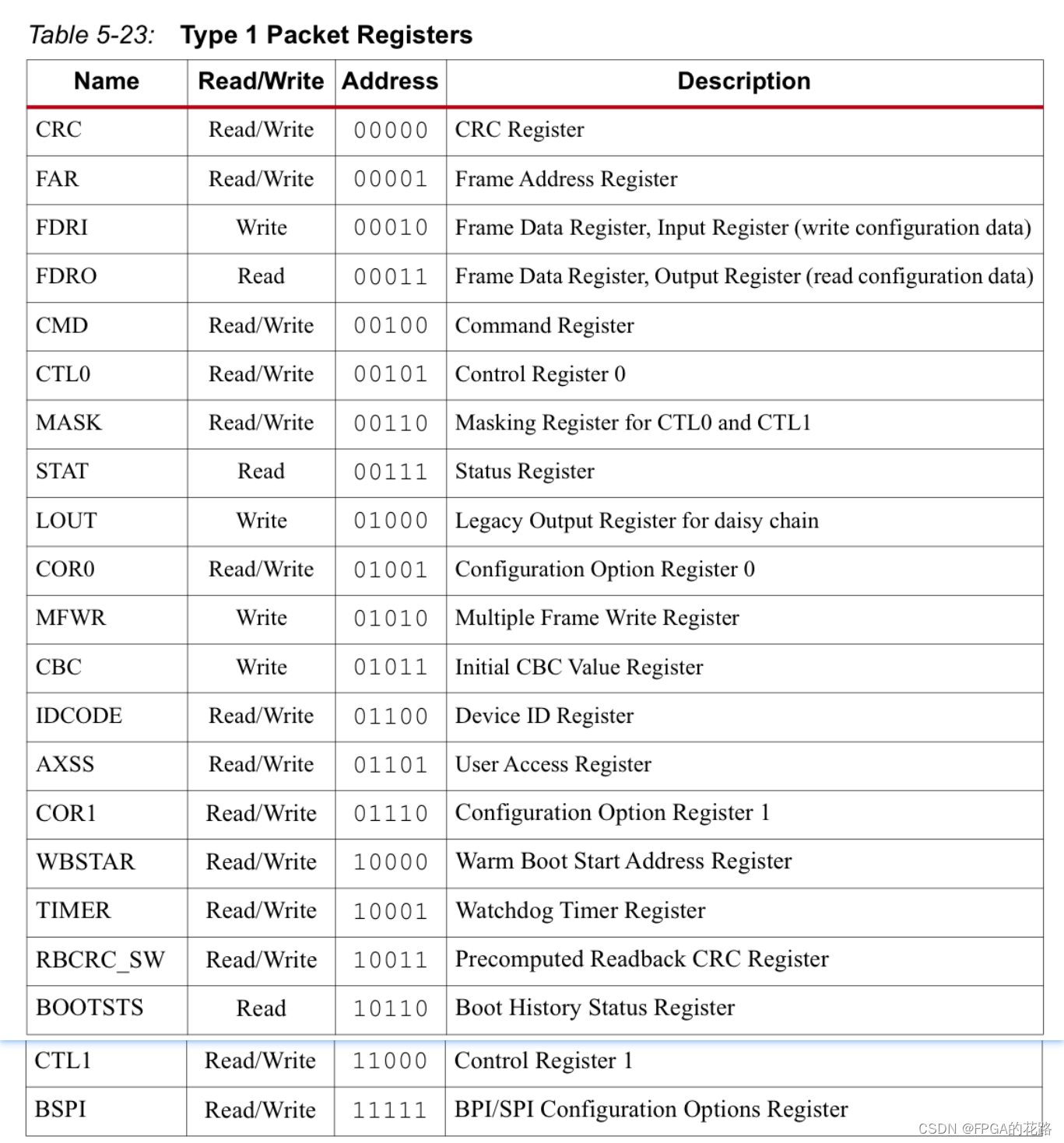

配置寄存器

总线位宽自动检测

- Serial、JTAG、SPI模式不支持总线位宽自动检测功能;

- 只检测D[7:0]的值,检测到0xBB,若下一次检测到0x11,则为x8;若下一次检测到0x22,则为x16;若下一次检测到0x44,则为x32;然后立即切换总线位宽,开始检测同步字

同步字

- 识别到同步字前没有其他包数据

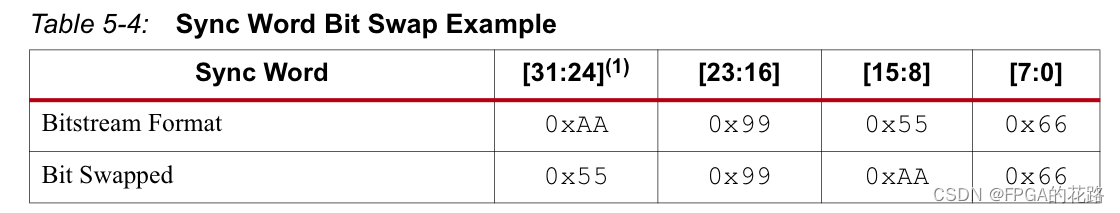

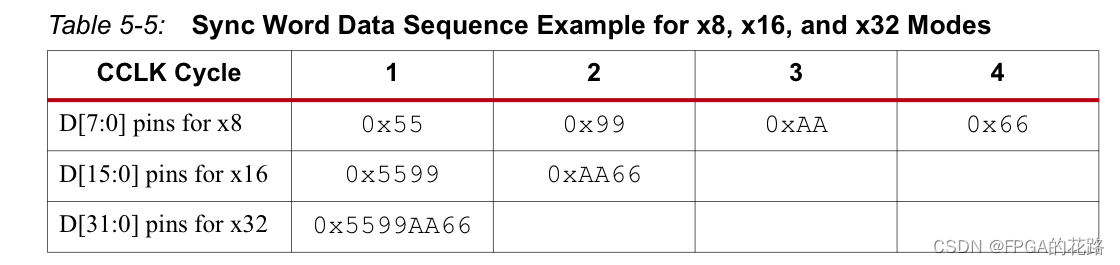

位交换和总线字序

参考资料

注:所有参考资料都在该文档绑定的下载资源里面,需要可以下载!

625

625

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?