注意:部分图片和表述来源于网络,引用处会说明。

一、PCIE简介

PCIE总线技术,也叫计算机内部总线技术”Peripheral Component Interconnect”,即外围组件互联。PCIe一般用在大型数据中心,可以接显卡,网卡等片外设备。

1.1 PCIe相关概念

PCIe的基本结构包括根组件(Root Complex),交换器(Switch)和各种终端设备(Endpoint)

- 设备类型

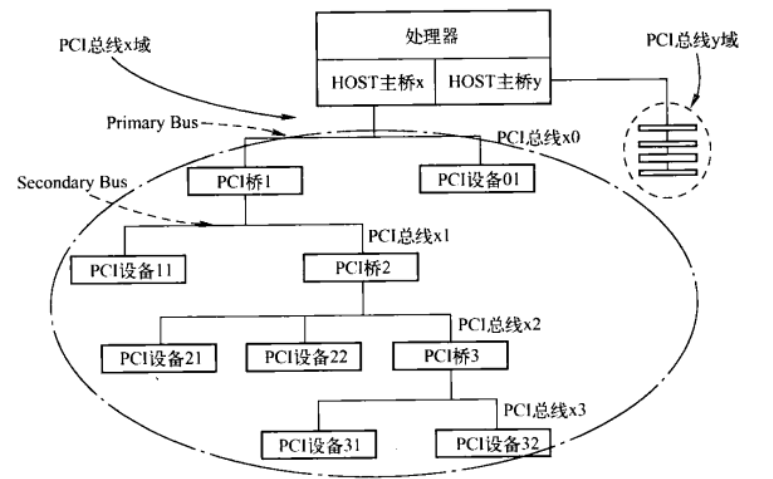

PCIe子系统有4种设备类型,分别是Root Complex(RC),PCIe switch,PCIe End Point和PCIe Bridge。如下图所示,switch设备和RC设备可以向上或向下连接PCIe总线,PCIe总线的最底层为EP设备。

-

RC

在PCI规范中也被称为HOST主桥,RC模块需要接受操作系统相关的硬件信号(例如接口寄存器、状态寄存器、异常寄存器、数据缓存等,小型状态机等),主要完成的事务有:

1)PCI域与IO域地址映射机制

2)实现兼容PCI设备的中断映射以及PCIe中断写事务机制

3)实现核与PCIe接口间的报文与消息类型转换

4)存储PCIe设备的配置数据 -

switch

switch的实现通常将PCIe控制器的事务层bypass,从数据链路层的数据直接发送到用户逻辑中

-

EP

RC和EP在PCIE树形结构中扮演的角色不一样,Rp是根,EP是叶结点。从PCIE角度来看,RP可以发起CFG Rd和Wr,但是EP是不可以的。

二者在物理层和部分链路层来说可以相互访问,但是传输层却不行 -

bridge

PCIe bridge可以用于扩展PCI总线,也可以用于连接慢速设备,在PCI总线树中起到呈上起下的作用。例如pcie转网卡bridge、pcie转USBbridge等

如图,PCI总线可以通过PCI桥组成一个胖树结构,其中每一个桥片都是父节点,而PCI Agent设备只能是子节点,每一个PCI总线的下方都可以挂接一个到多个PCI桥,每个PCI桥都可以推出一条新的PCI总线。在同一条PCI总线上的设备之间的数据交换不会影响其他PCI总线

-

PCIe的数据传输速率计算

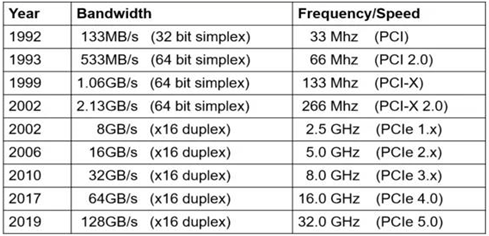

如下图所示是PCI到PCIe 5.0的所有版本的带宽和数据传输频率。

以PCIe3.0 x16情况举例,由于PCIe是一种全双共传输总线,因此计算其双向传输带宽和频率的关系为:8GHz * 16bit / 8bit * 2 = 32 GB/s

实际上由于PCIe采取8/10bit、128/130bit编码传输,实际有效代码需要乘以对应的系数。

参考链接:PCIe带宽的计算 -

NTB

有些特殊场景下,比如传统存储系统中的多个控制器,它们之间需要同步很多数据和控制信息,希望使用PCI-E链路直接通信。但是在switch上有多个RC设备时并不可以直接通信,因为主机的BIOS或者OS在枚举同一堆PCIe总线内的设备,并为其分配访问地址,此时会出现冲突。为了满足这个需求,出现了NTB技术。

其基本原理是地址翻译,因为两个不同的系统(术语System Image,SI)各有各的地址空间,会产生重叠。那么只要 在PCI-E Switch内部将对应的数据包进行地址映射翻译,便可以实现双方通信。这种带有地址翻译的桥接技术叫做None Transparent Bridge,非透明桥。 -

PCIe总线的缺点

- 由于采用了基于总线的共享传输模式,在PCI总线上不可能同时传送两组以上的数据,当一个PCI设备占用总线时,其他设备只能等待;

- 随着总线频率从33MHz提高到66MHz,甚至133MHz(PCI-X),信号线之间的相互干扰变得越来越严重,在一块主板上布设多条总线的难度也就越来越大;

- 由于PCI设备采用了内存映射I/O地址的方式建立与内存的联系,热添加PCI设备变成了一件非常困难的工作。目前的做法是在内存中为每一个PCI设备划出一块50M到100M的区域,这段空间用户是不能使用的,因此如果一块主板上支持的热插拔PCI接口越多,用户损失的内存就越多;

- PCI的总线上虽然有buffer作为数据的缓冲区,但是它不具备纠错的功能,如果在传输的过程中发生了数据丢失或损坏的情况,控制器只能触发一个NMI中断通知操作系统在PCI总线上发生了错误

-

ARI功能

参考链接:link -

PCI和PCIe的关系

-

PCI是共享型总线,多个设备共享一条总线,这种情况下必然存在总线总裁。PCIe则是点对点连接,一个设备直接连接到另一个设备,不存在总线竞争和仲裁。

-

PCI总线上是单向传输,任意时刻只有一个方向的传输,PCIe则是任意时刻都可以双向传输。

-

PCI有很多的边带控制信号,如FRAME#, IRDY#, TRDY, STOP#等。PCIe总线上传输的都是基于包(packet),控制和其他处理都嵌入在包里。

1.2 PCIe板级电气特征

本节主要参考《PCI Express® Card Electromechanical Specification 3.0》一文,主要针对PCIe的板级设计

参考链接:1.2 PCIe——PCIe电气特征

1.3 PCIE 硬件主要模块

参考链接:1.3 PCIe——硬件实现架构

1.4 PCIe地址空间划分

二、PCIe协议层次结构

PCI Express是一种分层协议,由设备核心层、传输事务层,数据链路层和物理层组成。

2.1 设备核心层(Host)

该层级是PCIe协议栈的上层逻辑,负责地址转换、host逻辑接口、DMA等。

2.2 事务层(TL)

传输事务层定义了PCIe总线使用的总线事务,这些事务可以通过switch等设备传送到RC等其他PCIe设备,R

本文全面介绍了PCIe技术,包括其架构、协议层次结构、运行机制、软件驱动等内容,并探讨了PCIe控制器的设计与验证方法。

本文全面介绍了PCIe技术,包括其架构、协议层次结构、运行机制、软件驱动等内容,并探讨了PCIe控制器的设计与验证方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

334

334

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?