一、信号描述

根据PCIe CEM 3.0手册,PCIe电气信号可分为链路信号和辅助信号

1.1 辅助信号

PCIe CEM定义了诸多辅助信号,其中部分信号功能可选。

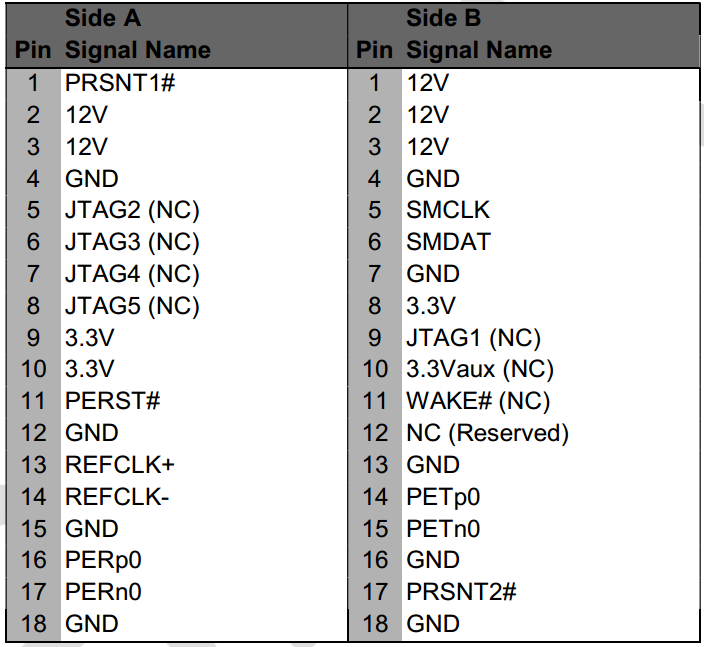

如下图所示是PCIe x1情况下的slot的正反面信号:

(1)REFCLK+/-

必须,差分时钟信号

(2)PERST#

必须

(3)WAKE#

可选,低电平有效,用于唤醒PCIe链路的主电源和参考时钟。处于L2低功耗状态的PCIe设备可以通过WAKE#引脚生成一个唤醒事件以便通知系统转至L0工作状态

(4)SMBCLK/SMBDAT

可选,SMBus接口信号

(5)TRST#, TCLK, TDI, TDO, and TMS

可选,JTAG接口信号

(6)PRSNT1#

必须,add-in-card在位检测引脚

(7)PRSNT2#

必须,add-in-card在位检测引脚

1.2 链路信号

二、PCIe PCB设计

PCB板材

PCIe从3.0发找到5.0,板级设计始终使用普通的FR4板材和廉价接插件,主要源自两个方面的改进,一是使用128b/130b编码来代替8b/10b编码,使得编码效率大幅提高;另一个是使用动态均衡技术,来代替先前代的静态均衡技术

三、PCIe的板级电路设计案例分析

Slot电路分析

金手指电路分析

注意:在针对PCIe设备的PCB的板级设计时,PCIe Gen3的差分阻抗为300欧,而gen4是 85欧

案例一

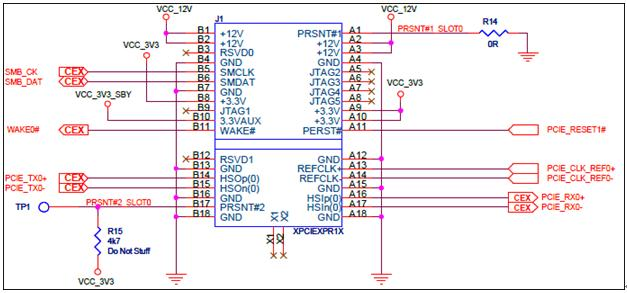

如图所示为x1的PCB原理图:

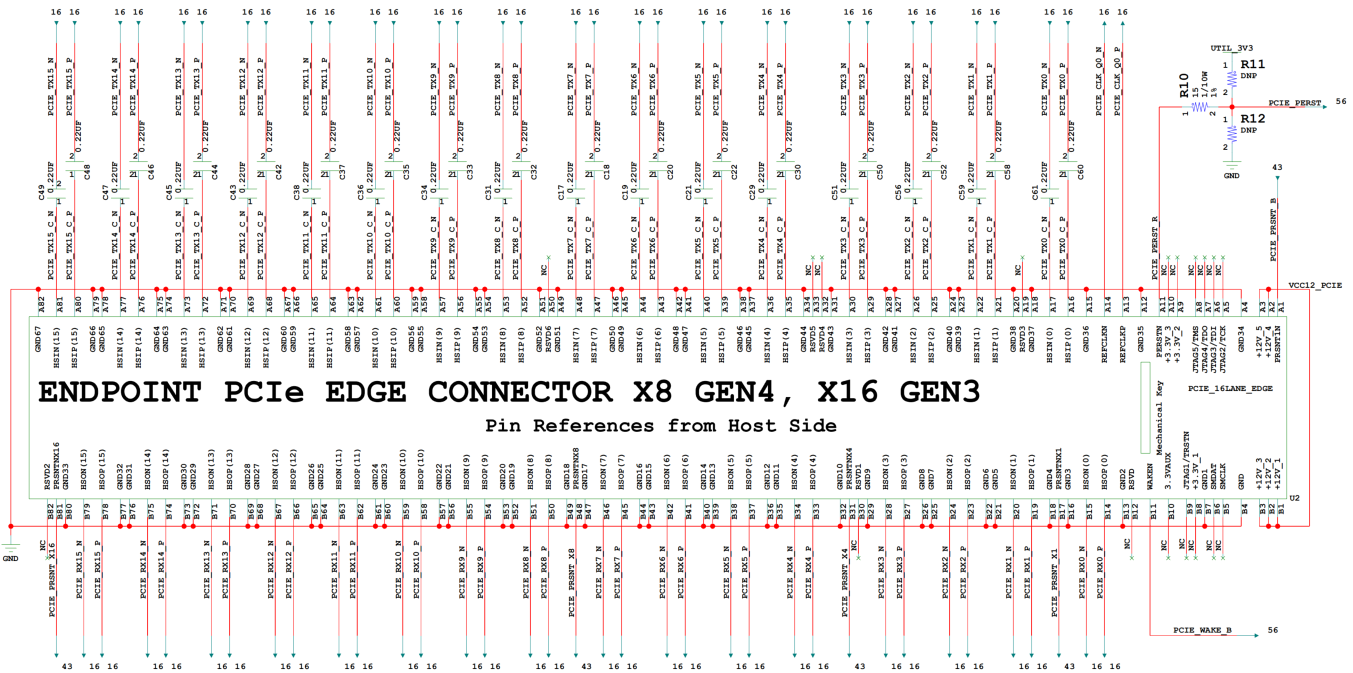

案例二:VCU118

如图是FPGA VCU118的PCIe板级设计电路原理图:

32

32

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?