一、概述

1.1 UCIe技术特征

并行接口,单端传输,直流耦合

线带宽密度:1.317 TB/s/mm

面带宽密度:1.35 TB/s/mm^2

传输速率:2/4/8/12/16/24/32 GT/s

传输延迟:<2 ns (发送端到接收端经过各自的adapter+physical layer的mainband接口的时间差,但不包括信号在有机衬底或者Interposer上的走线延迟)

1.1.1 封装要求

UCIe 1.0协议目前不适用于3D封装,适用于标准封装(2D)和先进封装(2.5D).

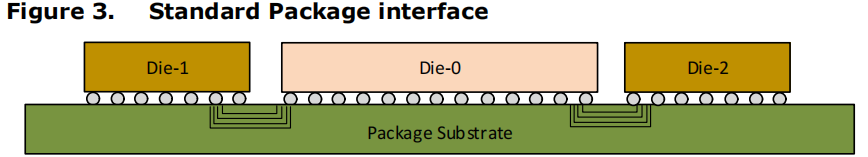

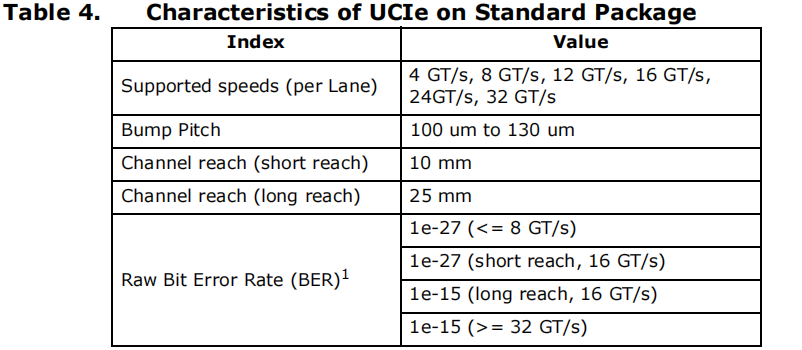

(1)标准封装

die直接在有机衬底上进行布局布线,适用于低成本、长线距(10mm ~ 25mm)互联的应用场景,相比封装外serdes互联方式,该方式能提供更好的误码率。

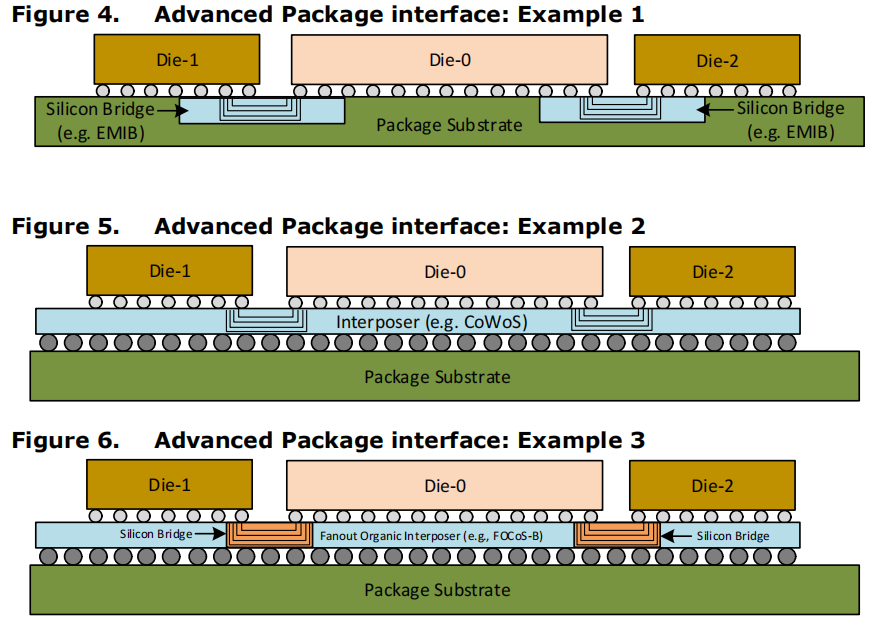

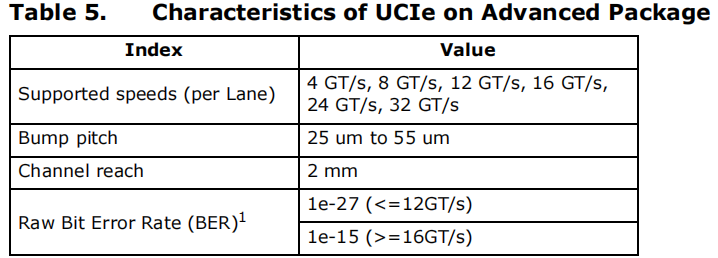

(2)先进封装

Die一般通过interposer或者silicon bridge互连。该封装方式成本较高,应用于更高带宽和更低延迟,能效比更好的场景。

先进封装可参考连接:

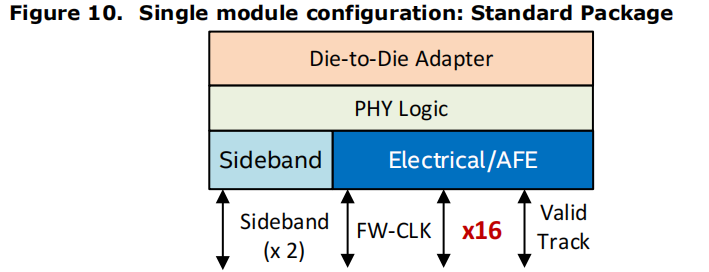

1.1.2 UCIe的module配置

- single module

标准封装下数据通道最多为x16,先进封装下数据通道最多为x64。

在设计中可以例化多个single module,每个被例化的single module都可以被独立操作,传输不同的协议

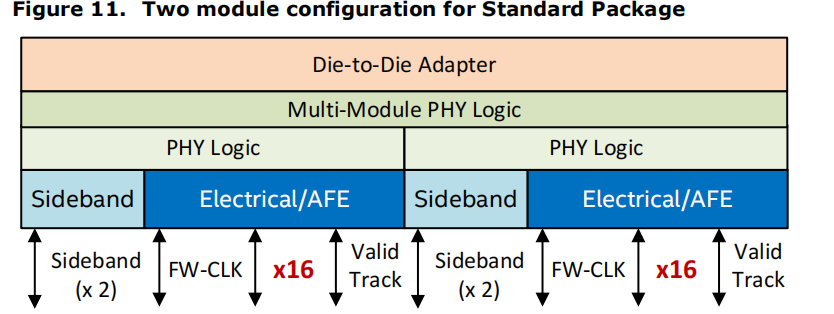

- multi module

该模式下有两种配置方式,分别是双模块和四模块配置。多个模块信号必须传输同一协议,且传输必须同步。

multi module的出现可以理解为扩展data channel的数量

1.1.3 bump pitch

凸块间距

1.1.4 Raw mode

针对UCIe protocol layer的一种数据透传模式,即flit报文中所有字段均由协议层填充,适配层不再填充CRC/FEC/retry等字段。通常用于UCIe retimer的设计,retimer只需完整的传递Flit报文即可,无需添加校验信息等。

用户自定义的协议层也可能会用到该模式

1.2 UCIe retimer

打通封装内互联和片间互联的通路,本质上是将单端的并行信号转换为差分的串行serdes信号。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1327

1327

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?