我们谈集成安全,就意味着其中有安全隐患,那么汽车芯片安全隐患到底来自哪里呢?

根据ISO 26262标准,进行安全验证的目的是避免汽车系统发生两种失效:一种是系统性失效,这种失效是决定性的,是设计所固有的;另一种是随机失效,包括永久性故障和瞬时性故障,这种失效不是决定性的,可能是由使用条件所引起的。

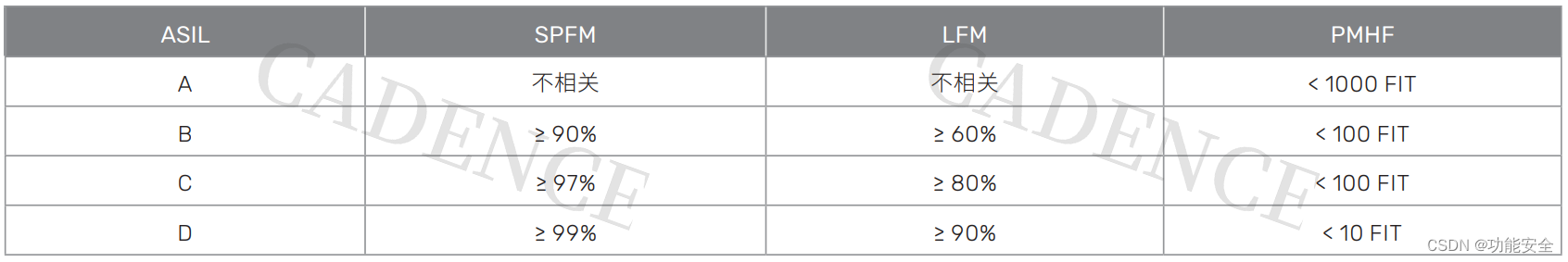

当然,我们不必对所有汽车芯片的安全验证一视同仁,在有些功能模块中,安全隐患的容忍度相对较高,比如空调控制芯片的安全性要求就要比制动器控制系统的芯片低很多。因此,ISO 26262 标准定义了四种不同的汽车安全完整性等级(ASIL):A、B、C 和 D,对应的单点故障指标(SPFM)、潜在故障指标(LFM)和硬件随机失效指标(PMHF)也有所不同,其中ASIL D 的级别最高。

图 | ASIL-A/B/C/D的硬件架构指标的目标值

一次 FIT (PMHF) 等于每十亿小时发生一次故障

如何加强芯片集成安全?

事实上,和其他行业一样,要系统性地规避一些安全隐患,除了要有强烈的安全意识外,还得靠机制、流程规范来助力。因此,在ISO 26262标准中,就提到了一种FMEDA方法。

什么是FMEDA?FMEDA是英文Failure Modes Effects and Diagnostic Analysis的缩写,也就是我们所说的失效模式影响与诊断分析。FMEDA通常是系统安全研究的第一步,通过在设计周期的早期进行准确评估,引导工程师完成硬件组件及其子部件的安全设计、验证和优化,在加快芯片面世周期的同时,还能辅助降低芯片设计、制造的风险成本。

对于FMEDA过程来说,有三大关键阶段:第一,架构性FMEDA,用于无芯片设计数据时的早期估计;第二,详细的FMEDA,拥有完备的RTL或网表时,根据设计和估计的诊断覆盖率得出基本失效率;第三,FMEDA验证,在RTL或网表的基础上,通过形式分析或仿真计算出更准确的诊断覆盖率。

一颗芯片要满足功能安全标准,除了安全验证以外,还需要匹配兼顾安全性的实现方法。而Cadence正在提供一整套完整的安全解决方案,在一个集成的流程中协同工作,并将安全要求从 Genus Synthesis 传递到 Innovus Implementation P&R,加速汽车系统级芯片(SoC)实现安全、质量和可靠性目标。

文章探讨了汽车芯片的安全隐患来源,主要分为系统性失效和随机失效,并介绍了ISO26262标准定义的不同安全完整性等级。FMEDA作为失效模式影响与诊断分析,是芯片设计早期评估安全的重要工具,涉及架构性、详细和验证三个关键阶段。Cadence提供了一整套安全解决方案,支持汽车SoC的安全、质量和可靠性目标实现。

文章探讨了汽车芯片的安全隐患来源,主要分为系统性失效和随机失效,并介绍了ISO26262标准定义的不同安全完整性等级。FMEDA作为失效模式影响与诊断分析,是芯片设计早期评估安全的重要工具,涉及架构性、详细和验证三个关键阶段。Cadence提供了一整套安全解决方案,支持汽车SoC的安全、质量和可靠性目标实现。

1976

1976

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?