Verilog中unsigned与signed加法结果的比较

参考阅读:1. verilog中有符号数和无符号数在赋值、运算中的区别

2.关于Verilog中的signed类型

这块知识在学习的过程中,还需要注意Verilog中的数据长度可以用户定义,存在算数截断的问题,在运算的时候不但要考虑类型,还要考虑位宽,所以在运算的过程中,又会复杂一些,其中这篇很好的通过实验展示这块知识点

3.Verilog有符号与无符号的数值运算

首先计算机中,负数为什么用补码表示?

可以用钟表来类比,因为计算机的位宽是有限的,用有限的位数来表示无限的世界,钟表就是用12个小时来代表无限的时间,钟表倒拨五个小时,和正拨7个小时是一样的,不一样的是人们如何去理解,其中对于8位的二进制而言,就是-1,相当于倒拨一位,总的长度位256,那么和正拨255(8’b1111 1111)是一样的,其中1+255 = 256,负数以及其补码之间位“互补”的关系,且找到了补数,就可以用加法代替减法运算,也相当于钟表永远只顺时针针旋转,这也就回答了使用补码代替负数,节约一个减法器,简化了计算机的硬件设备。

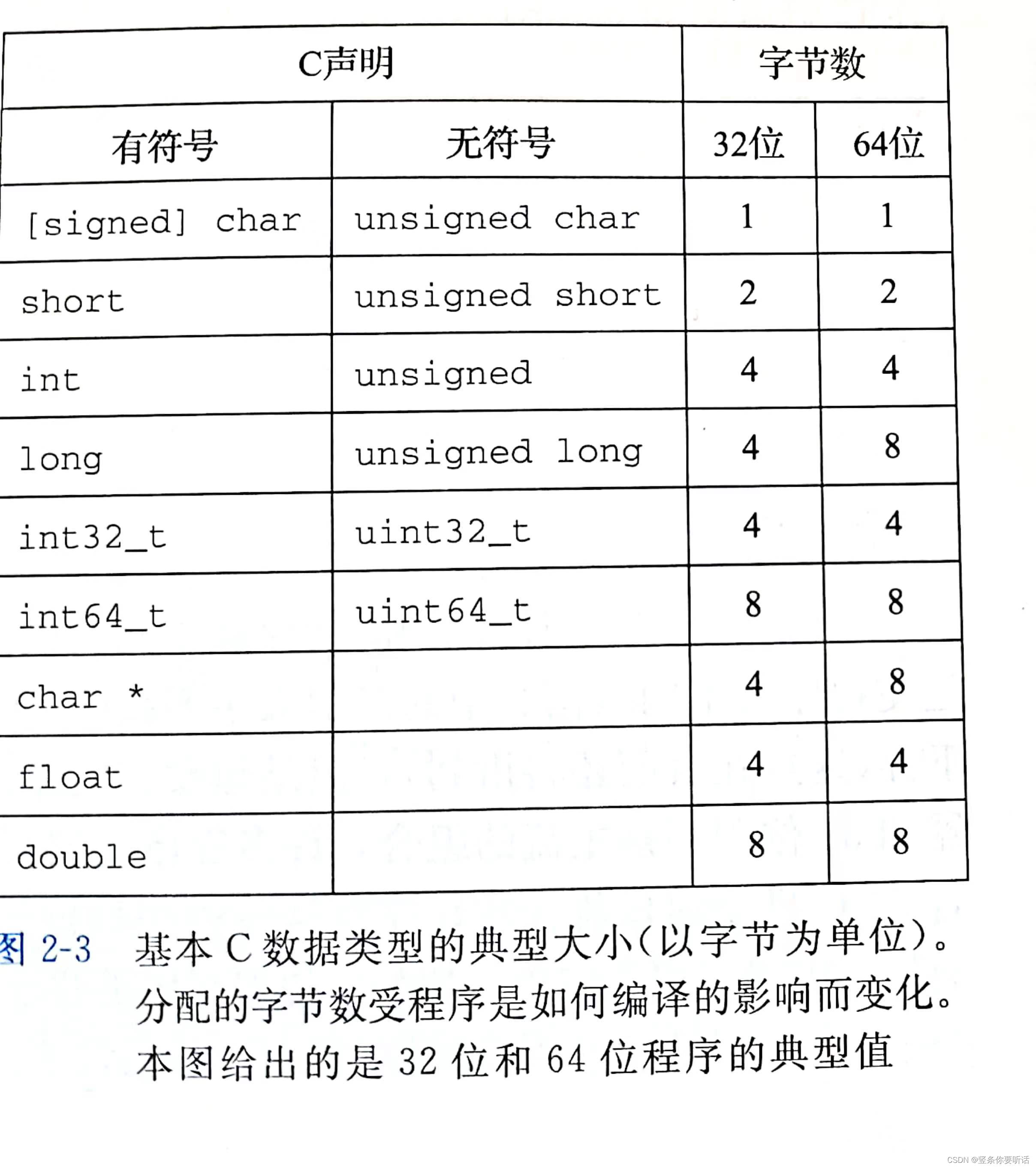

对于计算机中数的表示,如下图所示表示的机器字长(32位,64位)不同,基本的C数据类型的典型大小,以及每个类型的表示范围,可以看到正负数不是对称的,负数比正数多一个,原因以8位数据为例,表示正数时,范围为0-255,能够表示256个数据,当表示有符号数据时,高位为符号位,则表示的为-127-0-127,其中0有+0和-0,表示了256个数据,如果0只用一个表示,实际只表示了255个数据,为了避免浪费,所以负数的表示范围为:-128 -+127,其中-1 补码表示为8‘b1111 1111.

1. 赋值

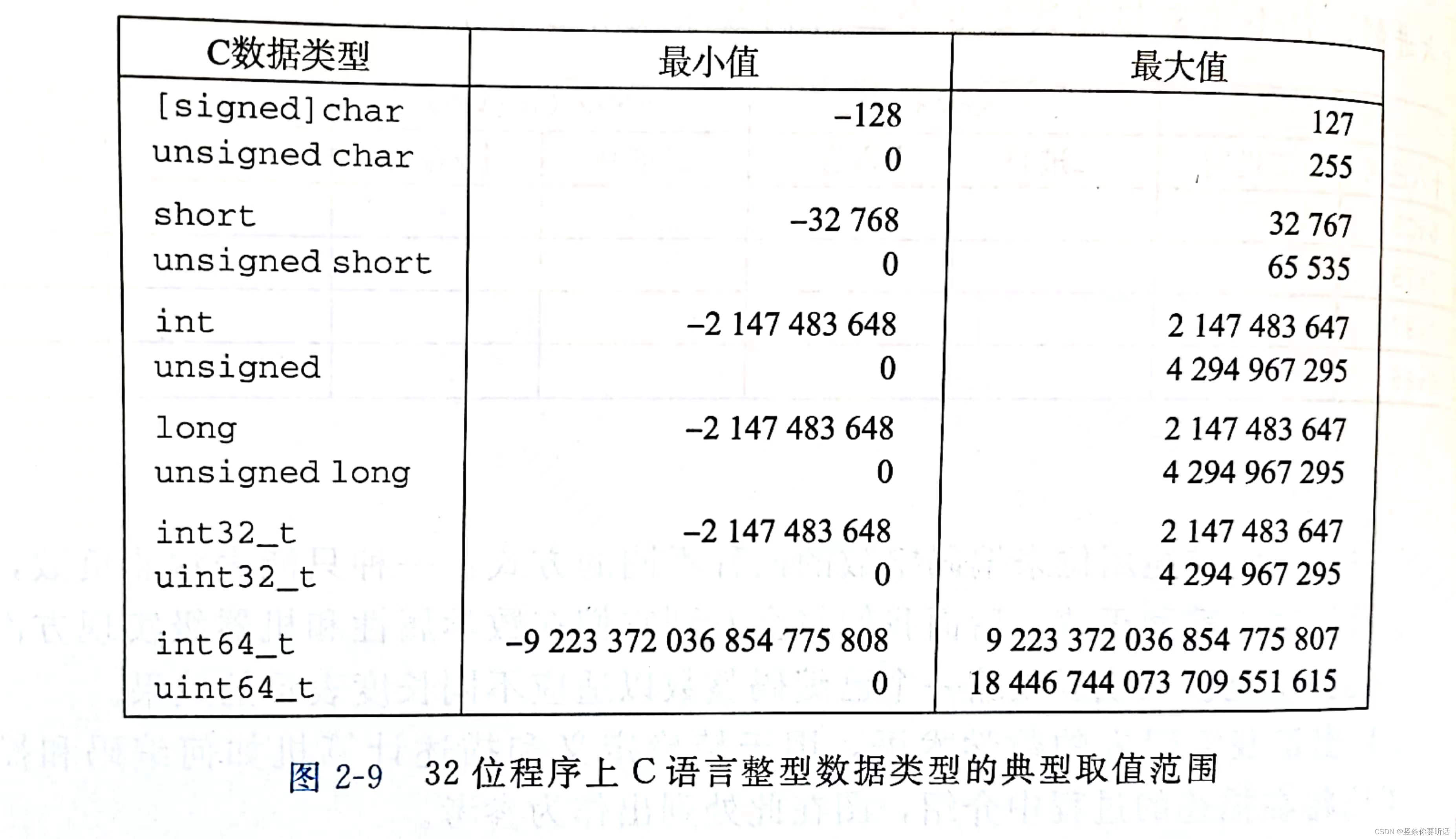

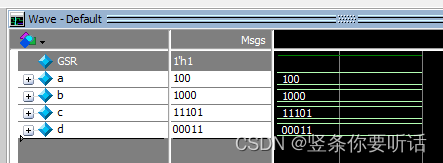

verilog默认的寄存器类型(reg)和线网类型(wire)的值是无符号数的,但同时verilog提供了signed关键字作为有符号数的标志,是否为有符号数,是人为加上的概念,数具体的表示的值取决于你如何看待,对于8‘1000_0001,因为正数和负数的表示不是一一对应的,当将其看为有符号(129)和无符号(-127)表示的数值不同,首先来测试一下有无signed关键字对于赋值上的影响。代码段如下所示:

module Numbertest(

input clk,

output wire none //默认reg,wire是无符号类型的,默认常熟为32位

//将一个常数赋值给变量时,会根据位宽变换给的时补码

//输入输出端口中不能指定unsigned

);

reg signed [7:0] a;

reg [7:0] b;

reg [7:0] bb_unsigned;

reg signed [7:0] bb_signed;

reg signed [7:0] aa_signed;

reg [7:0] aa_unsigned;

reg [7:0] cc_add;

reg signed [7:0] cc_signed_add;

initial begin

a = -1; //有符号

b = -1; //无符号

end

always@(posedge clk) begin

bb_unsigned <= b; //255

bb_signed <= b; //255

aa_signed <= a; //-1

aa_unsigned <= a; //8'hff

cc_add <= a + 2'b10; //8'b11111111(-1的补码) + 1'b10 = 8'b0000 0001

cc_signed_add <= a + 2; //-1 + 2 = 1

end

endmodule

可以看出,有无signed关键字对于赋值来说没有任何影响,不论是wire类型的直连还是reg类型的阻塞赋值,本质意义上都是“0”和“1”的传递,是否带符号都是人为加给电路的意义,二进制的形式都是一样的。

通过以上的结论,加下的实验验证对于赋值的类型我们尽量使得运算保持一致

2 移位

在理论上:>>>(算术右移)与>>(逻辑右移)的区别:

逻辑右移就是不考虑符号位,右移一位,左边补零即可。

算术右移需要考虑符号位,右移一位,若符号位为1,就在左边补1,;否则,就补0。

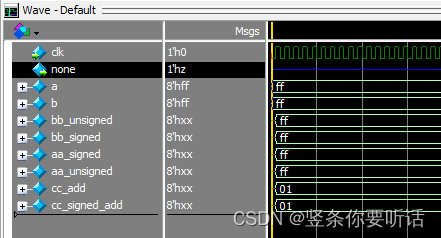

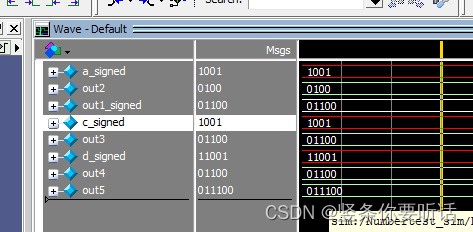

结果如下,其中输出除过out1_signed都和原理相同,其中out1_signed我预期输出值为5‘b0 0100,但代码的输出值为5’b0 1100

思考后,首先将有符号数进行逻辑移位肯定是不推荐。思考背后的原因,a_signed = 4’b1001,表示的是有符号数的-7,其中在逻辑移位时因为移位后的位宽大于当前位宽,所以先进行了赋值拓宽操作,然后再进行逻辑移位,修改代码如下,仿真的验证了设想。

module Numbertest();

//默认reg,wire是无符号类型的,默认常熟为32位

//输入输出端口中不能指定unsigned

reg signed [3:0] a_signed = 4'b1001;

reg signed [3:0] c_signed = -7; //4'b1001

reg signed [4:0] d_signed = -7; //5'b11001

wire signed [3:0] out2;

wire signed [4:0] out1_signed,out3,out4;

wire signed [5:0] out5;

//1移位运算

//1.1逻辑移位

assign out1_signed = a_signed >> 1; //有符号类型和逻辑移位

assign out2 = a_signed >> 1;

assign out3 = c_signed >> 1;

assign out4 = d_signed >> 1; //首先时有符号数的赋值运算

assign out5 = d_signed >> 1;

endmodule

结论:原理是正确的,但因为赋值后的位宽的不同,结果又有不同,容易发生错误,错误的原因主要是,当有符号数在逻辑移位时,移位后位宽一致,则右移补零,当位宽大于移位前的位宽,先将符号位进行拓展,然后右移高位补0。

这里还可以观察到如果有符号变量表示为4‘b1001和直接等于-7,在位宽相同时表示形式一致。

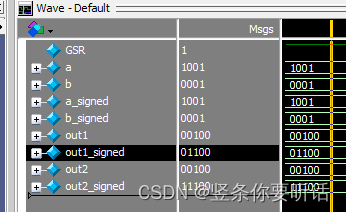

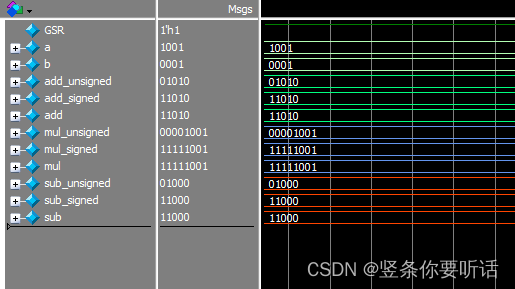

2 加法、乘法、减法(都是signed或者unsigned)

2.1 加法,减法

加、减法无符号时,两者相加后的结果只有位宽加一,才能正确表示相加的结果,且结果同样是无符号数,否则因为溢出截断高位,从而结果不正确。

对于有符号数的加减法,同样结果位宽要进行加一,只不过其中a,b是以补码的形式表示的(正数的补码 = 源码,负数的补码 = 反码+ 1),有符号数和无符号数据的加减法结果是一样的,和移位运算相同,signed的真正作用是决定如何对操作数扩位的问题。

2.2 乘法

乘法同样类似于加法,有符号和无符号的乘法结果是一样的,只是乘法的位宽为原始位宽的之和。

`timescale 1ns / 1ps

module Numbertest();

//默认reg,wire是无符号类型的,默认常熟为32位

//输入输出端口中不能指定unsigned

reg [3:0] a = 4'b1001 ;

reg [3:0] b = 4'b0001;

wire [4:0] add_unsigned, add_signed, add;

wire [7:0] mul_unsigned, mul_signed, mul;

wire [4:0] sub_unsigned, sub_signed, sub;

//加法

assign add_unsigned = a + b; //5'b0_1001 = 9

assign add_signed = $signed(a) + $signed(b); //5'b1_1001 = -7(-8 + 1 = -7)

assign add = {a[3], a} + {b[3],b}; //同add_signed

//乘法

assign mul_unsigned = a * b; //5'b01001

assign mul_signed = $signed(a)*$signed(b); //8'b1111_1001

assign mul = {{(4){a[3]}},a} * {{(4){b[3]}},b}; //同mul_signed

//减法

assign sub_unsigned = a - b; //5'b01000

assign sub_signed = $signed(a) - $signed(b); //5'b11000(-8-1 =-9)

assign sub = {a[3],a} - {b[3],b}; //同sub_signed

endmodule

结论:signed的真正作用是决定如何对操作数扩位的问题

3 有符号数与无符号数运算混用

只有两个操作数都是有符号数,才会把两个操作数都看作有符号数计算,否则无论是有符号数还是无符号数都会按照无符号数计算。

4 $signed用法举例

$signed()任务来强制转换数据

已知wire [2:0] a = 3’d4; wire [3:0] b = 4’d8;

wire [4:0] C= $signed(a ) + $signed(b) >>>2,

wire [4: 0] d = a + b >> 2;

则 C = ? D = ?

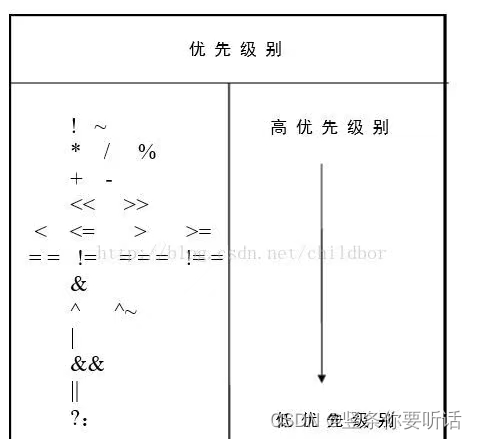

这里要注意加法的优先级高于移位操作,所以按照signed和unsigned的法则进行拓宽后进行计算。

char a, b;

unsigned char c,d;

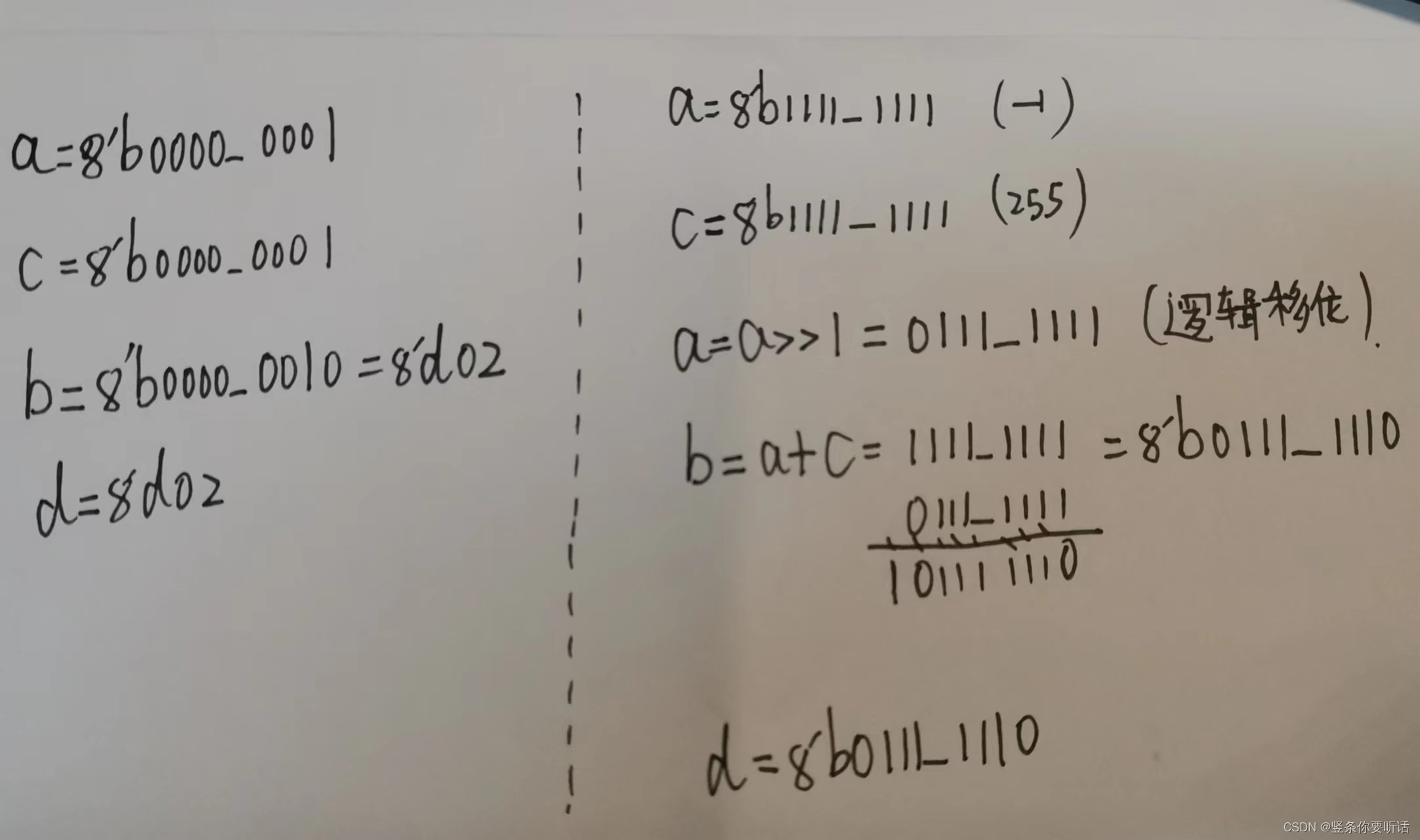

a = 1,c = 1, b = a + c; d = b;请用十六进制表示运算结果b = ?,d = ?

a = -1,c = -1 ,a = a >> 1; b = a + c ; d = b;请用二进制表示运算结果b = ? d = ?

答:前面那张图表示char默认为signed类型,我的答案如下,如果有问题,欢迎评论

本文详细探讨了Verilog中signed和unsigned数据类型的差异,特别是在赋值、移位和算术运算中的表现。通过实例代码展示了有符号数和无符号数在加法、减法、乘法以及移位运算中的行为,并强调了位宽和补码表示的重要性。在处理混合类型运算时,必须谨慎,以避免错误。$signed()函数用于强制转换数据类型。最后,指出在处理加法和移位运算时,位宽的扩展和符号的处理是关键点。

本文详细探讨了Verilog中signed和unsigned数据类型的差异,特别是在赋值、移位和算术运算中的表现。通过实例代码展示了有符号数和无符号数在加法、减法、乘法以及移位运算中的行为,并强调了位宽和补码表示的重要性。在处理混合类型运算时,必须谨慎,以避免错误。$signed()函数用于强制转换数据类型。最后,指出在处理加法和移位运算时,位宽的扩展和符号的处理是关键点。

6701

6701

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?