前言

在之前的一个项目中,我的工程一部分运算中主频达到了400MHz时钟。当时的运算需要用到cnt累加器,但是在最后的综合实现部分,会出现时序问题。而且用一般的时序约束也不管用。为了实现这个功能,在完成加法的运算时就有必要使用器件本身自带的加法器IP核,这样使用器件内部的电路,就可以很好的避免时序问题。那么在FPGA中该如何实现代码中的累加呢?cnt=cnt+1;

一、顺序累加器设计

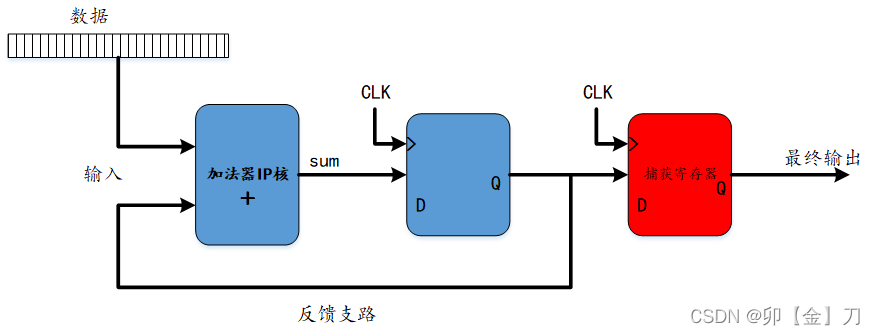

所谓累加最根本的修改是如何将加法‘+’替换为IP核?可以将加法器的求和输出接到寄存器的输入,再将寄存器的输出给到加法器的一个输入,而加法器的另外一个输入接数据源。即按下图进行连接:

reg [31:0] cnt;

reg [31:0

2186

2186

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?