在仿真flyby拓扑时发现插损波形与典型的点对点高速通道预期结果不同(不从0 dB开始),因此该学习笔记对此现象进行记录分析

低频分析

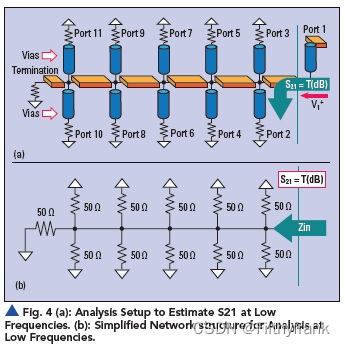

在Fig4(a)的等效电路中,信号(入射波)从端口1发射。由于在低频下分析该电路,因此传输波的波长在物理长度上不会导致幅度和相位变化,可以将所有端口都充当为单个节点。此外,进行另一个基本假设:所有端接均视为50欧姆。做出此假设是为了将结果与EM求解器结果进行比较(因为EM求解器给出的S参数值参考阻抗为50欧姆)。根据这一假设,低频下的等效电路可转化为一个简化网络,如图Fig4(b)所示。

现在,我们求解输入阻抗Z和低频时的S21值:

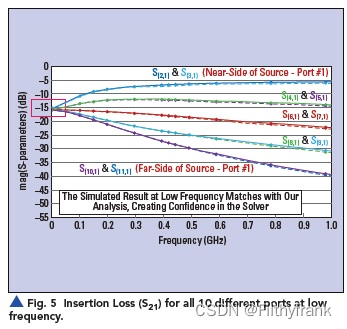

现在,可以确定S21在低频下的值,且使用EM求解器计算结果也是-15dB。Fig5显示了从电磁仿真器(ADS SIPro)获得的10个不同端口在低频时的插入损耗结果。在低频时,EM Solver产生了相同的-15dB结果(用红框突出显示),这表明所有端口都是等效的,从而证实了我们最初的分析假设,即所有端口在低频下都充当单个节点。

现在我们再在高频下分析

高频分析

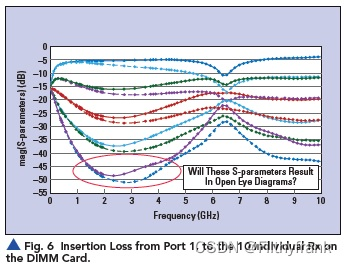

在高频下,入射信号的波长导致幅度和电压沿物理长度变化。这时手动计算的方法不再适用,可使用电磁求解器分析分布式传输线的效应和损耗,以确定所有端口的传输系数T(dB)。Fig6显示了频率高达10 GHz时所有端口的插入损耗:

可以发现Fig6中不同的插入损耗结果并不是我们习惯在高速数字通道中观察到的响应。通常我们期望插入损耗(S21) 在低频时从0 dB开始,且单调下降。这时我们需对这个现象进行解释,以便正确分析多点拓扑。

波形理解

在本次分析中,我们没有经典的点对点高速数字通道来获得期望的插入损耗。

我们可以看到低频下多点拓扑的插损为-15dB,低频插入损耗取决于连接到总线的DRAM数量(导致插入损耗为-15 dB)。同样的结构导致两条线路(与端口10,11有关;远端侧)在50GHz左右的插入损耗约为-3 dB,Fig6所示。我们需要了解,多点拓扑本质上不是阻抗控制的;沿线的每个短截线都存在不匹配。

评估多点总线的性能时,S参数结果与典型的点对点高速通道预期结果大不相同。理想情况下,所有新设计都应首先从预布局模型表示开始,然后再进入物理布局。但是,即使现有布局图稿已用于新设计,使用向导快速构建预布局表示也有助于进行故障排除和进一步优化。

目前已知优化原则:

(1) 减少每个多点Rx端口的C/A信号和时钟之间的偏斜

(2) 减少路径中的阻抗不匹配

(3) 对于每个 Rx 提供相同干扰的激励信号频率,保持短截线为最佳长度和间距

这些设计元素对于在 DDR4 和 DDR5 所需的更高数据速率下实现良好信号完整性是必需的

1759

1759

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?