查看时序报告是FPGA开发过程当中一个关键的分析时序的方法,通过时序报告了解信号在FPGA中布线所经过路径情况。查看时序报告的方法也是FPGA的开发基础之一。开发者可以通过布线路径中的每一条延时情况返过来分析代码设计是否合理,是否存在待优化情况,这一节通过一个工程具体介绍一下时序报告的分析方法。

一、创建时钟约束

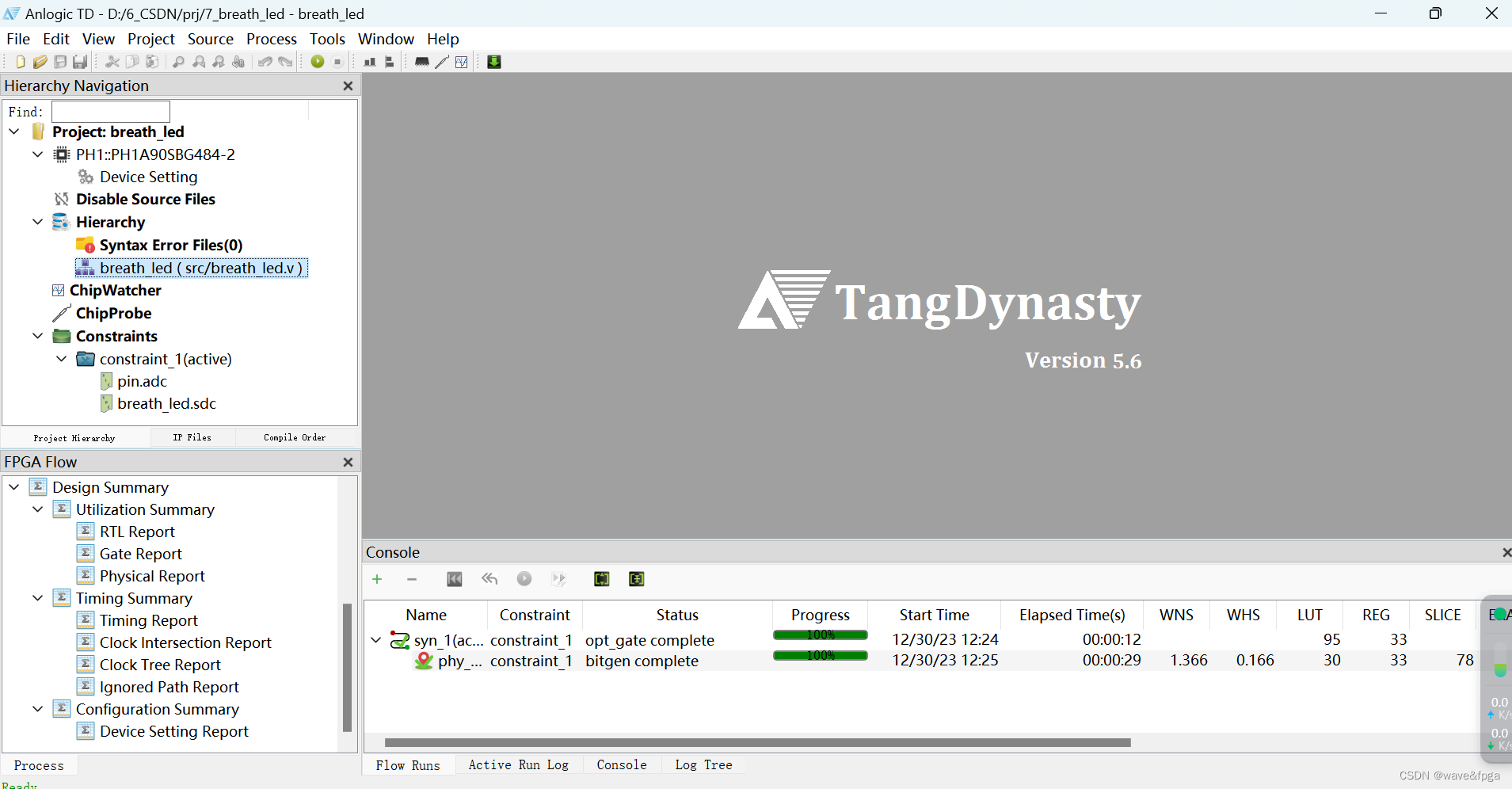

这一个节使用前面讲到的呼吸灯的应用实例工程来进行时序约束,我们来打开工程先看下如下图所示。

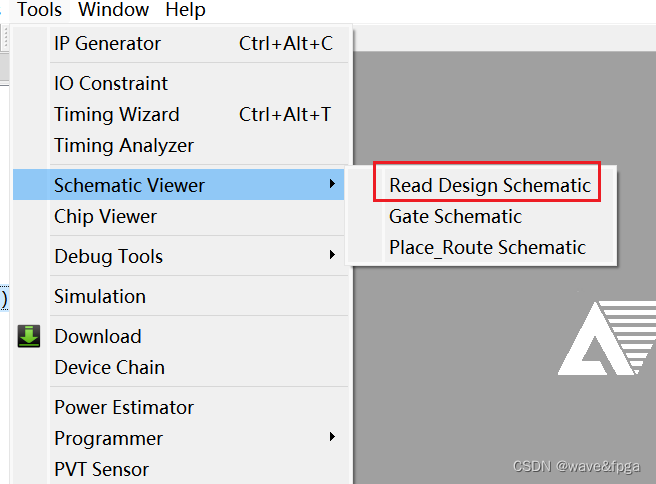

点击综合之后,点击Tools -> Schematic Viewer ->Read Design Schematic可以查看设计的数字电路情况进一步检查代码设计是否合理。

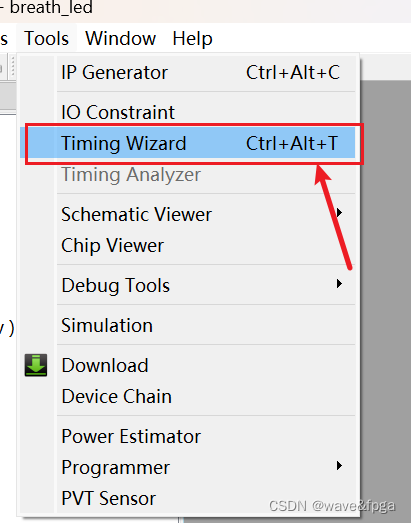

设置时序约束 打开工程之后点击Tools -> Timing Wizard或者按快捷键Ctrl + Alt + T。

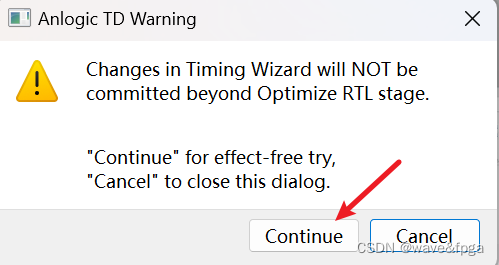

在弹出的对话框中点击Continue。

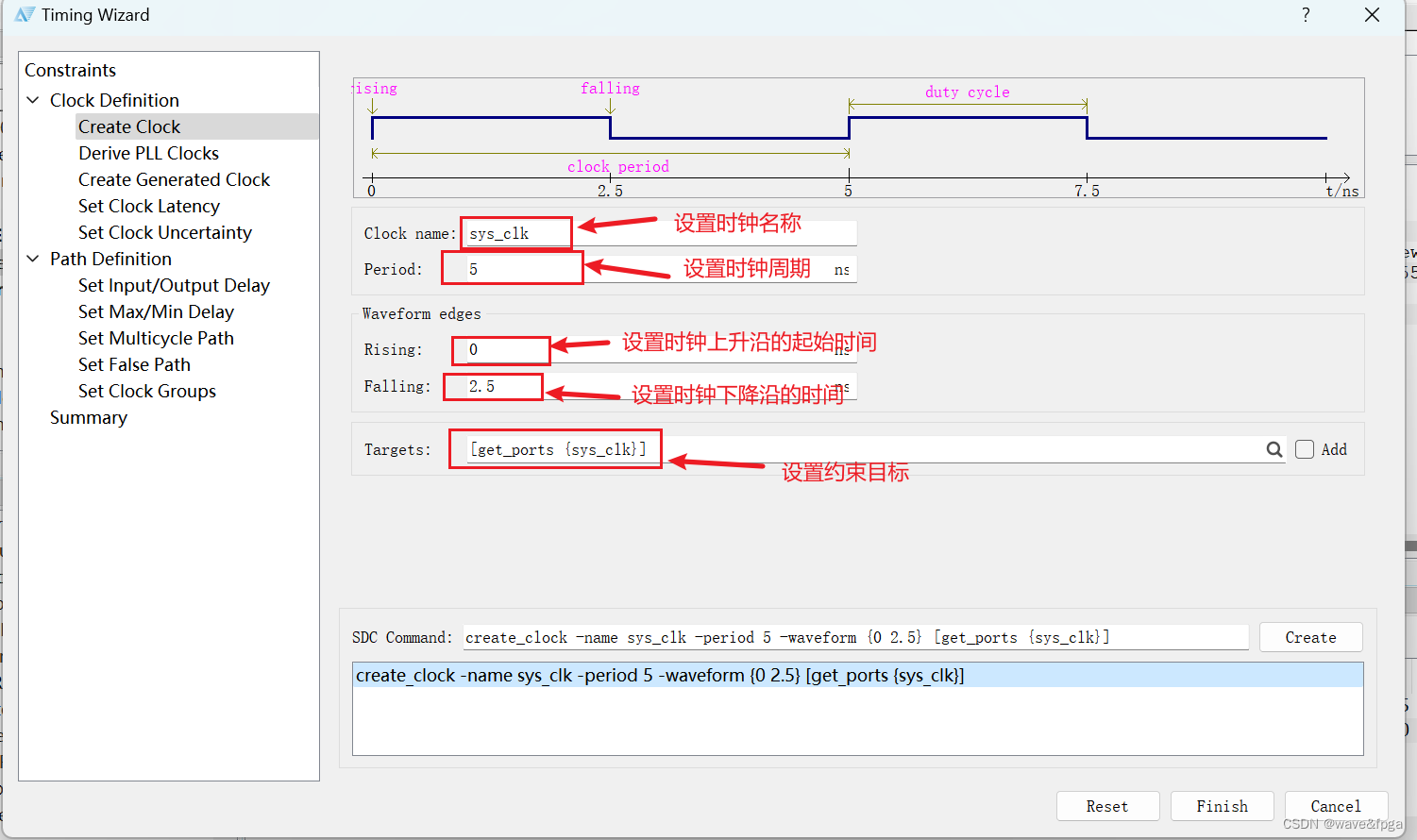

在Clock Definition中点击Create Clock,进行时钟的约束。

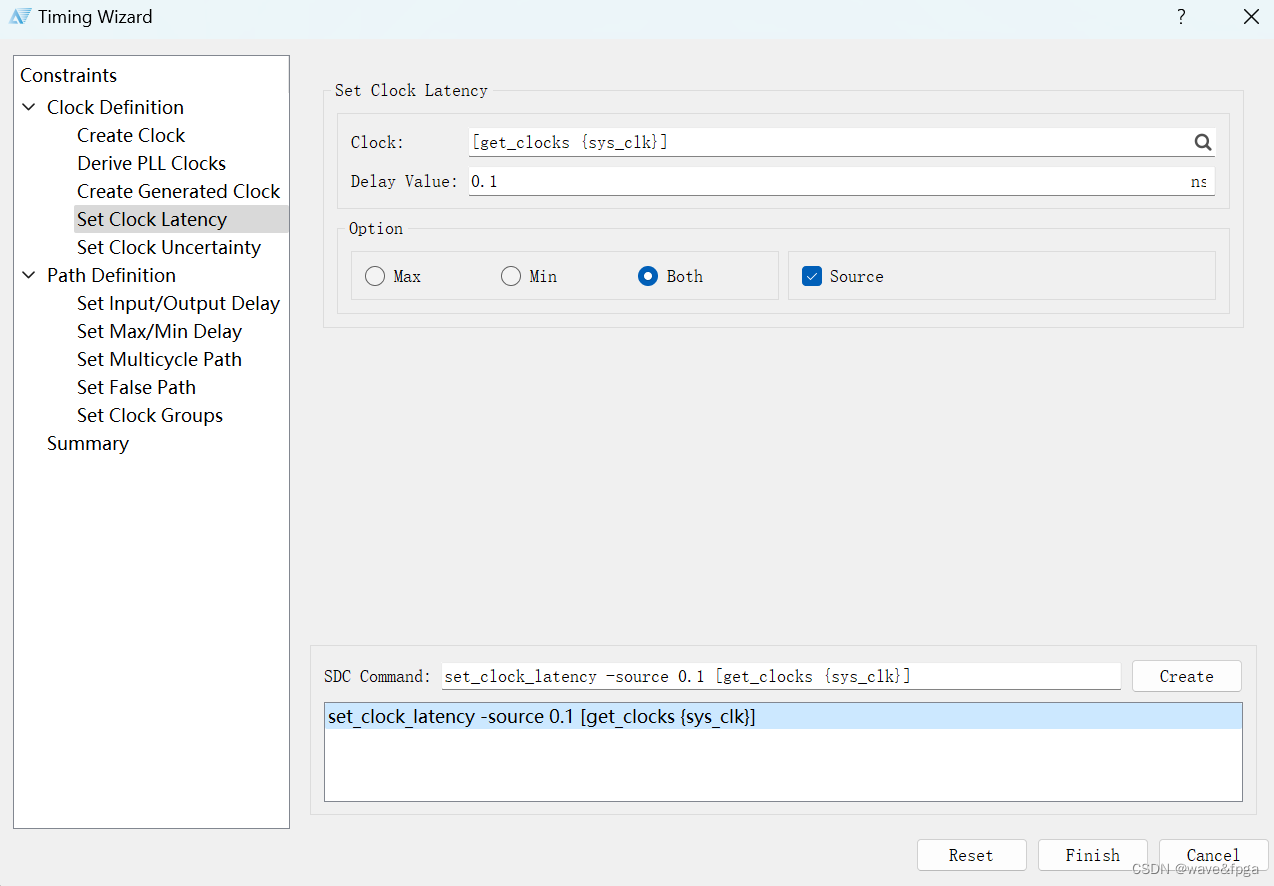

设置时钟延时为0.1ns。时钟延时可以根据具体的调试实际情况确定,如果不考虑时钟延时也可以不进行设置。

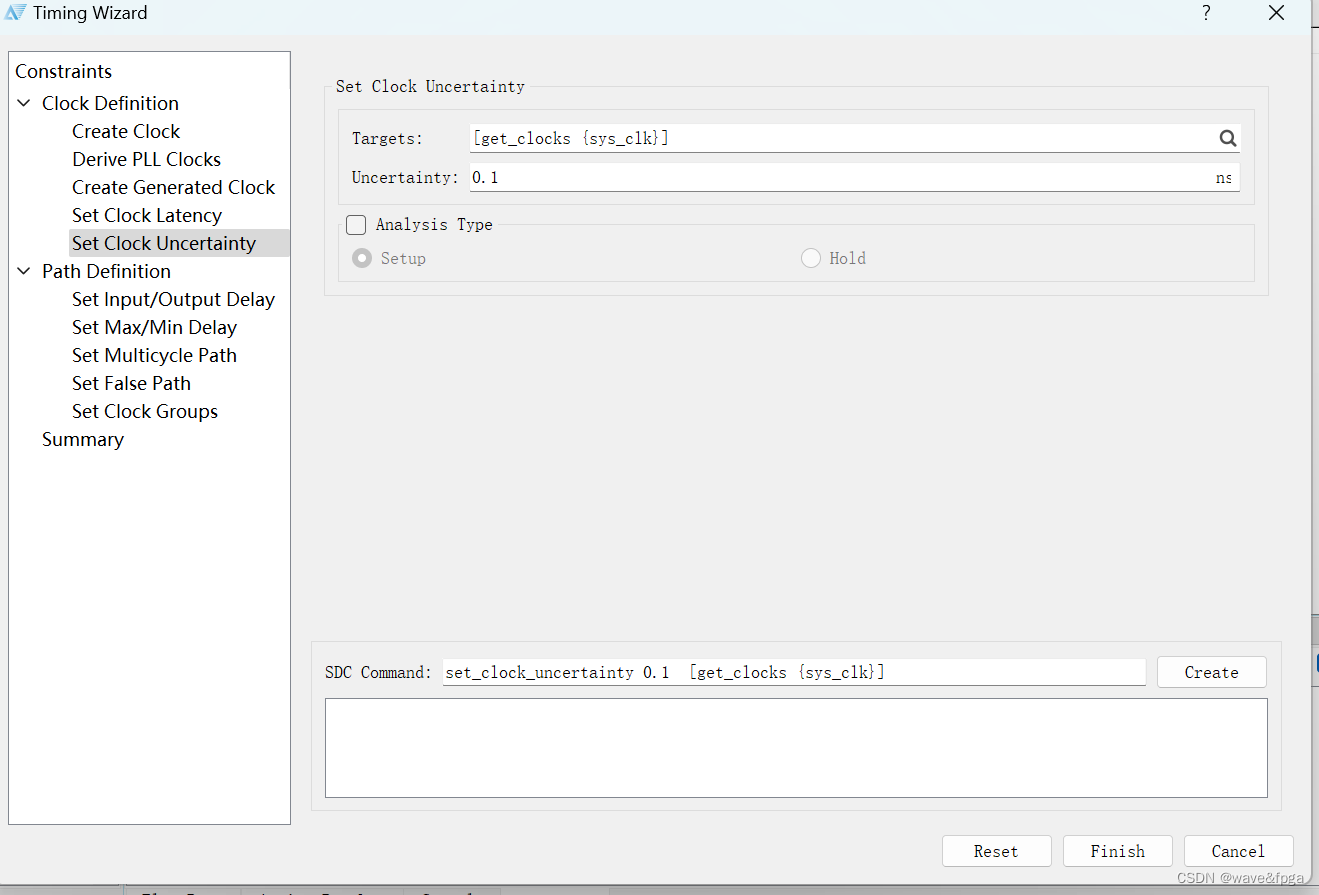

设置时钟不确定性,一般时钟不确定性设置0.1~0.5ns之间,具体根据设计人员的开发调试情况设置即可。

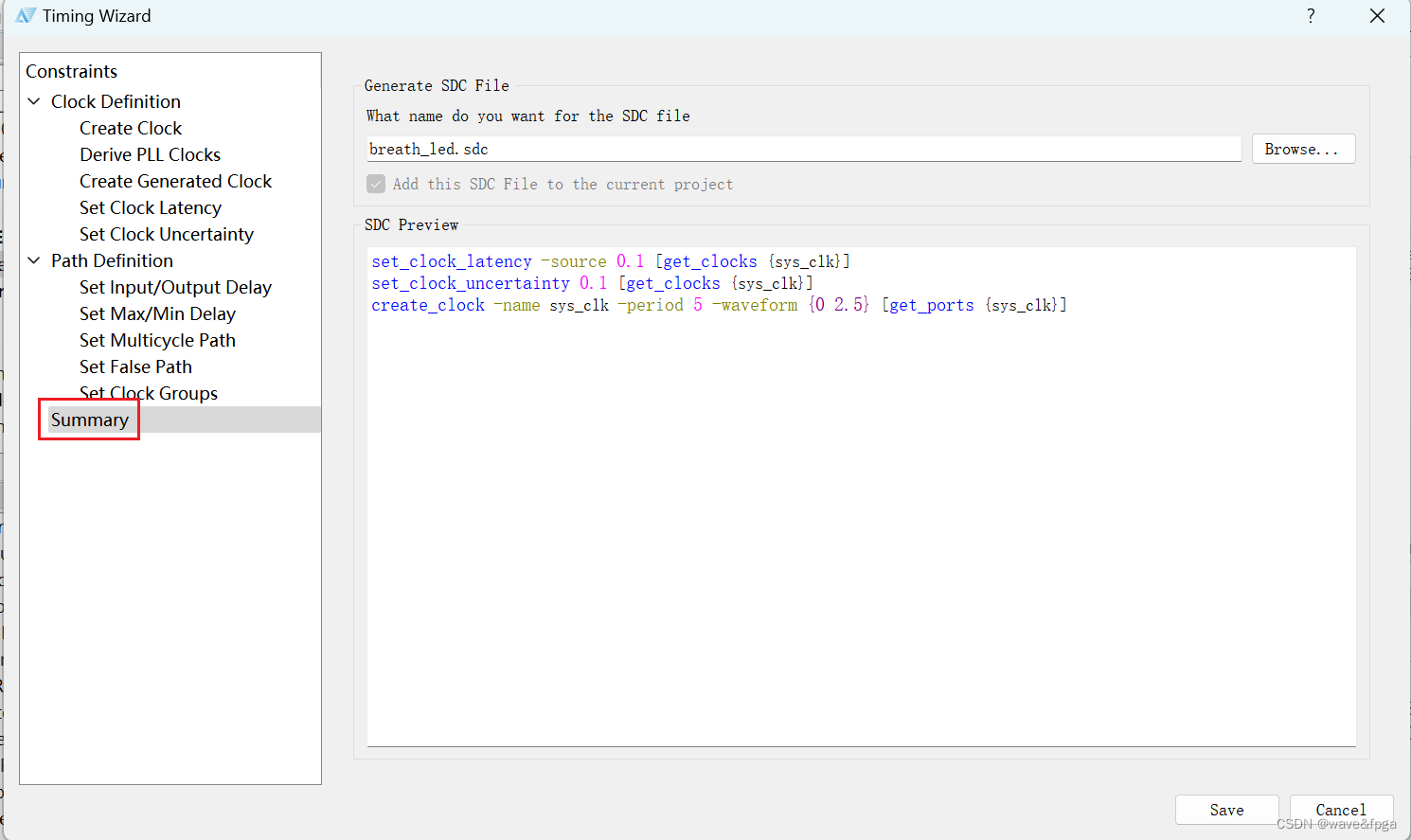

点击总结可以查看当前工程的总体约束情况。

二、查看时序报告

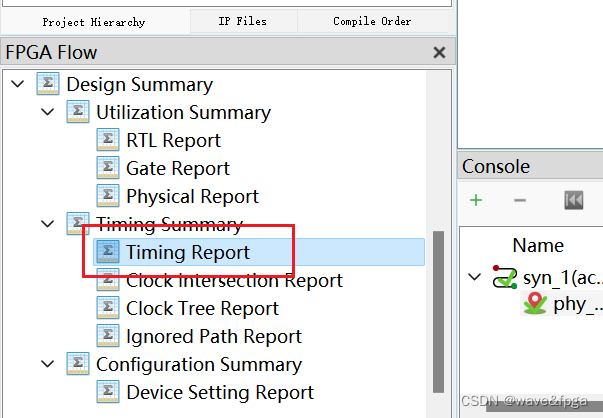

当约束设置完成,对工程进行全编译之后,点击Timing Report或者Tools -> Timing Analyzer会弹出时序报告窗口。

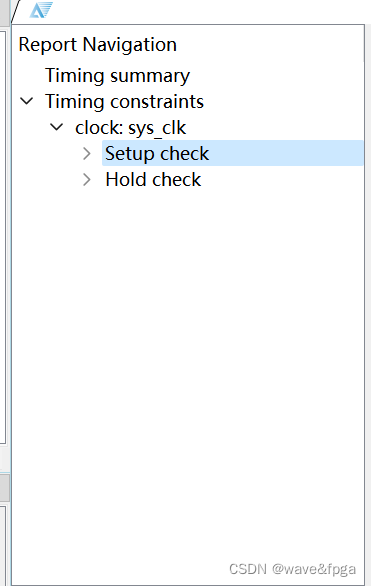

可以看到有建立检查和保持检查,我们先点看建立检查进行查看分析,保持裕量的查看方法也是同理的这里就不进行分析介绍了。

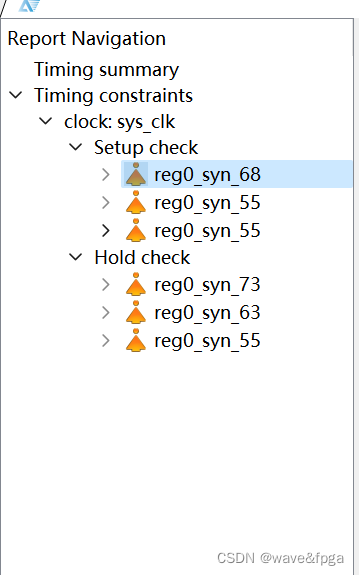

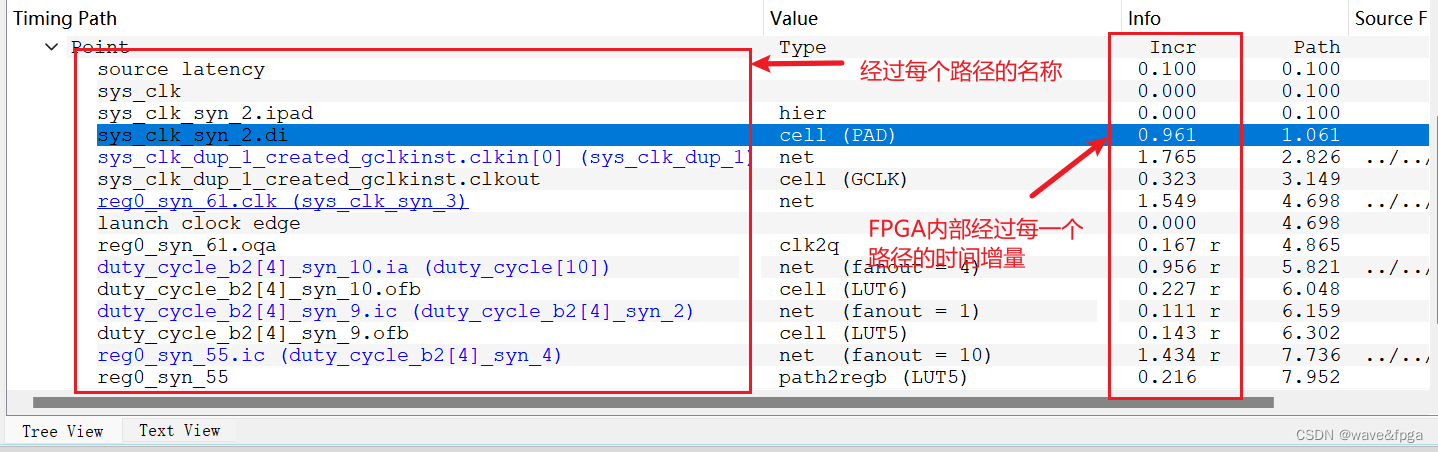

这里我们以reg0_syn_55为例子,先在建立时间检查内,点开reg0_syn_55路径,进行时序的分析。

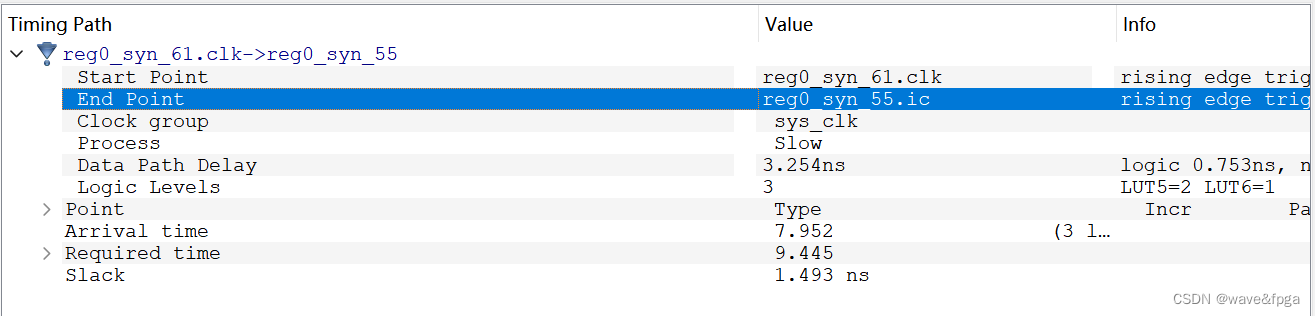

可以看到在时序路径中给我们展示了,路径的起始点和结束点,数据的抵达时间和需求时间,建立裕量=数据的需求时间-数据到达时间,这里可以看到数据的需求时间是9.445ns ,数据的道道时间是7.952 ,建立裕量是1.493 用9.445-7.952 = 1.493,说明我们的公式是符合软件分析工具计算的。

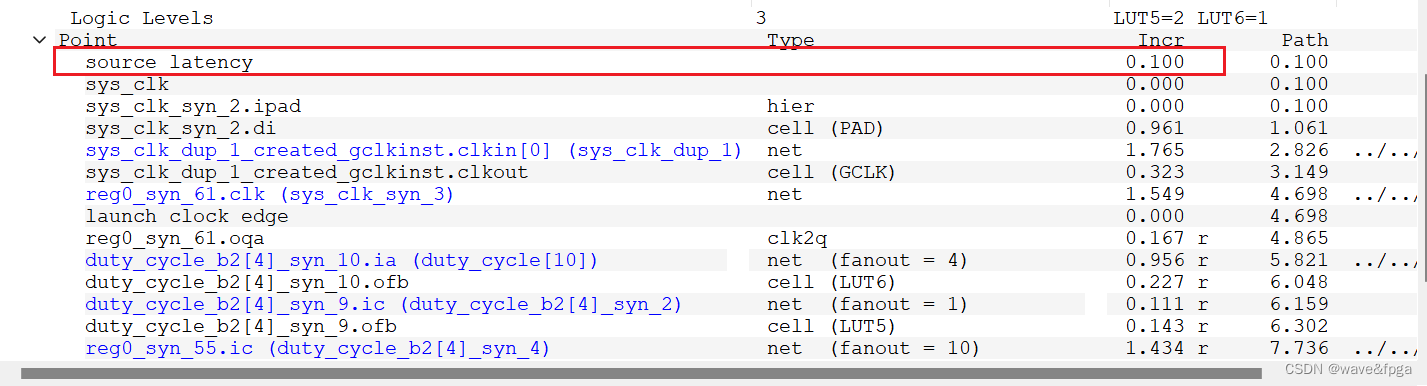

加下来打开Point,和Required time具体看一下时序路径,时钟延时是1ns,因为我们之前约束的就是1ns,软件计算的时候自动累加上。

从时钟的起始点时间开始算起,经过每一个路径EDA工具模拟真是器件参数,自动计算出时间的增量,经过的每一个路径时间累加和,最后计算出数据到达时间。net一般表示线网络延时,cell一般表示经过LUT延时。

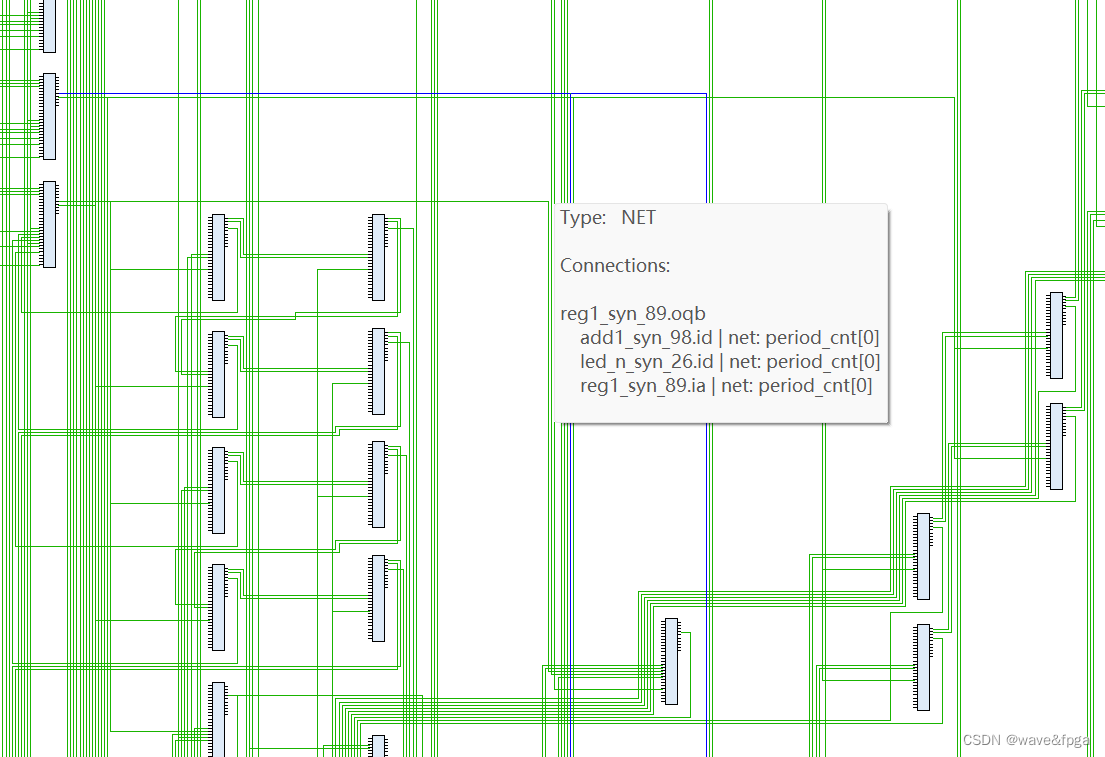

这里也可以查看具体的路径在RTL网表中的位置,在蓝色路径中,鼠标右键,查看原理图,进入RTL界面,可以反过来分析代码,同样也可以查看FPGA内部的布线位置,点击Chip Viewer。如下图所示。

接下来看下数据需求时间计算路径消耗的时间累加值也是一样的,这里要注意下,在需求时间里面,这里有建立时间的值,时钟不确定性的值和时钟恢复悲观的值,也只之前我们提到的,按照公式计算最后得到数据需求时间的值。

三、总结

本节介绍了创建时钟约束的方法,时序报告分析的方法,查看FPGA内对应路径的RTL视图和FPGA内布线网络视图的方法。FPGA的时序分析内容还是很多的,由于一节一节总说时序约束还是有点枯燥,从下一节开始介绍一些应用实例,然后使用到其他时序约束的地方再进行介绍。FPGA的时序约束也需要每个FPGA设计的工作者在项目实践中慢慢的探索,不是一蹴而就的。这一小节的参考工程在下面百度云链接,感兴趣的可以下载使用。

链接:https://pan.baidu.com/s/1_mgZyjgMUzbrO99E966-NQ

提取码:lz1w

这也应该是2023年发出来的最后一篇笔记了,今年在国产安路FPGA的专题里面,整好写了20篇,也上传了部分文档。一方面是自己学习记录,另一方面也希望能或多或少的对同行的人有所参考和帮助。下一节介绍国产安路FPGA UART串口的应用实例。

2502

2502

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?